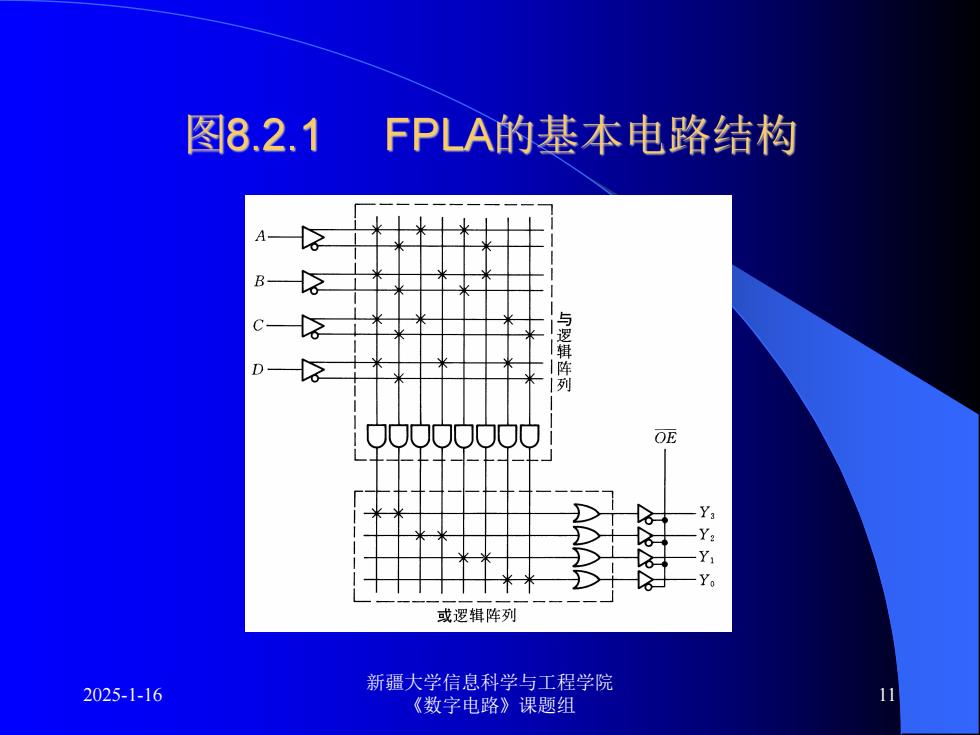

图8.2.1 FPLA的基本电路结构 B D 与逻辑阵列 OE 或逻辑阵列 新疆大学信息科学与工程学院 2025-1-16 《数字电路》课题组 11

2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 11

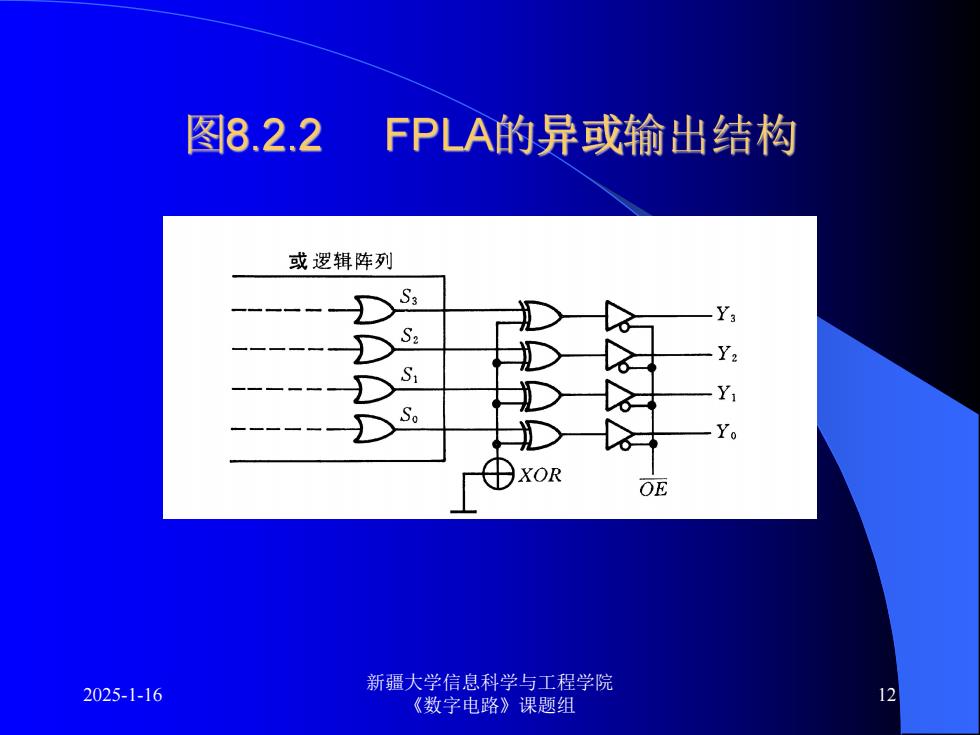

图8.2.2 FPLA的异或输出结构 或逻辑阵列 D D Y - -Yo ⊕xOR OE 2025-1-16 新疆大学信息科学与工程学院 12 《数字电路》课题组

2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 12

图8.2.3 时序逻辑型FPLA的电路结构 PR/OE D G D G D G Y D 2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 13

2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 13

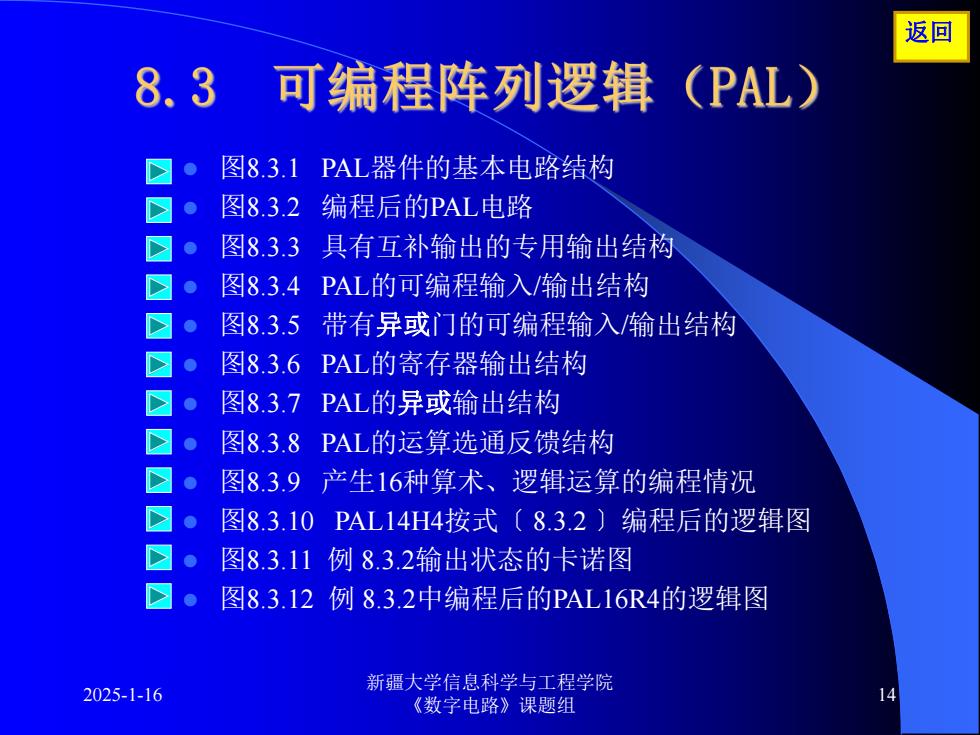

返回 8.3可编程阵列逻辑 (PAL) 图8.3.1PAL器件的基本电路结构 ● 图8.3.2编程后的PAL电路 图8.3.3具有互补输出的专用输出结构 图8.3.4PAL的可编程输入输出结构 )。图8.3.5带有异或门的可编程输入输出结构 图8.3.6PAL的寄存器输出结构 D 图8.3.7PAL的异或输出结构 图8.3.8PAL的运算选通反馈结构 ● 图8.3.9产生16种算术、逻辑运算的编程情况 图8.3.10PAL14H4按式〔8.3.2)编程后的逻辑图 图83.11例8.3.2输出状态的卡诺图 图8.3.12例8.3.2中编程后的PAL16R4的逻辑图 2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组

2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 14 l 图8.3.1 PAL器件的基本电路结构 l 图8.3.2 编程后的PAL电路 l 图8.3.3 具有互补输出的专用输出结构 l 图8.3.4 PAL的可编程输入/输出结构 l 图8.3.5 带有异或门的可编程输入/输出结构 l 图8.3.6 PAL的寄存器输出结构 l 图8.3.7 PAL的异或输出结构 l 图8.3.8 PAL的运算选通反馈结构 l 图8.3.9 产生16种算术、逻辑运算的编程情况 l 图8.3.10 PAL14H4按式〔 8.3.2 〕编程后的逻辑图 l 图8.3.11 例 8.3.2输出状态的卡诺图 l 图8.3.12 例 8.3.2中编程后的PAL16R4的逻辑图 返回

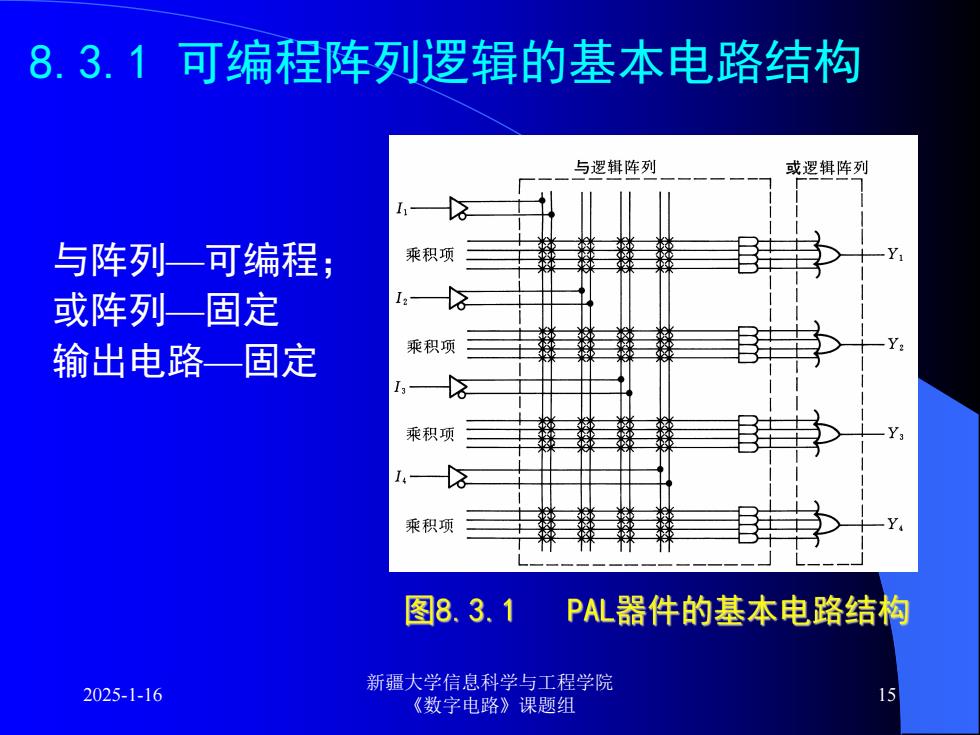

8.3.1可编程阵列逻辑的基本电路结构 与逻辑阵列 或逻辑阵列 与阵列一可编程; 乘积项 或阵列一固定 输出电路—固定 乘积项 乘积项 乘积项 图8.3.1 PAL器件的基本电路结构 新疆大学信息科学与工程学院 2025-1-16 《数字电路》课题组

2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 15 与阵列—可编程; 或阵列—固定 输出电路—固定 8.3.1 可编程阵列逻辑的基本电路结构