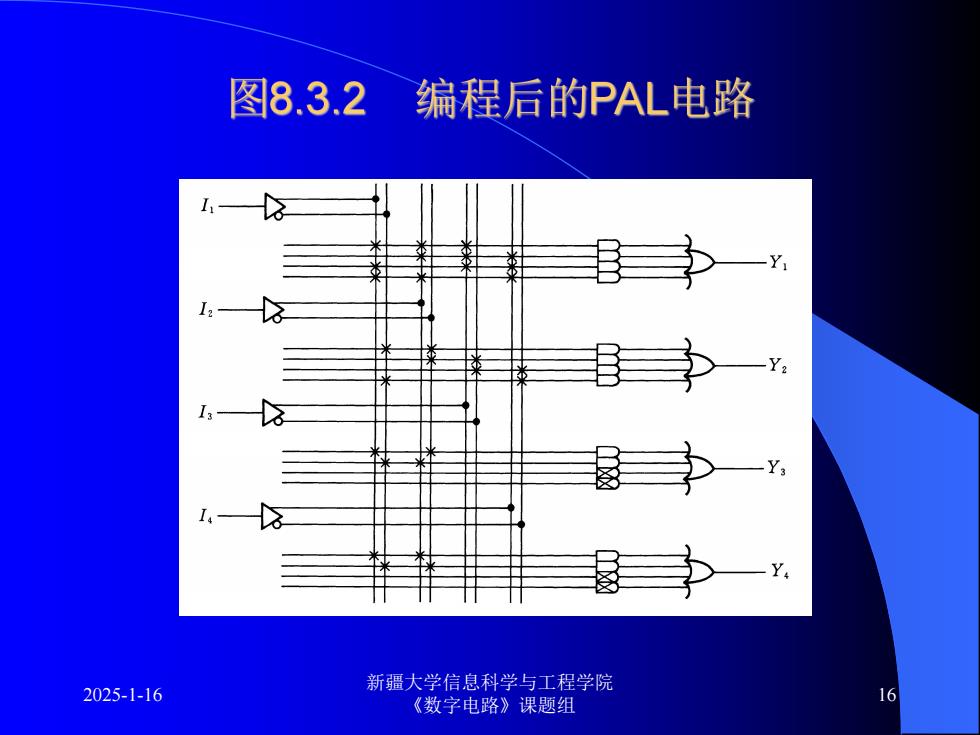

图8.3.2 编程后的PAL电路 2025-1-16 新疆大学信息科学与工程学院 16 《数字电路》课题组

2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 16

8.3.2 PAL的输出结构 ①专用输出结构。输出端只能输出信号,不能兼 作输入。只能实现组合逻辑函数。目前常用的产品有 PAL10H8、PAL10L8等。 输入项 新疆大学信息科学与工程学院 2025-1-16 《数字电路》课题组 17

2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 17 8.3.2 PAL的输出结构 ① 专用输出结构。输出端只能输出信号,不能兼 作输入。只能实现组合逻辑函数。目前常用的产品有 PAL10H8、PAL10L8等

②可编程/O结构。输出端有一个三态缓冲器, 三态门受一个乘积项的控制。 当三态门禁止,输出呈高阻状态时,/O引脚作 输入用; 当三态门被选通时,/O引脚作输出用。 输入项 I/0 2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 18

2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 18 ② 可编程I/O结构。输出端有一个三态缓冲器, 三态门受一个乘积项的控制。 当三态门禁止,输出呈高阻状态时,I/O引脚作 输入用; 当三态门被选通时,I/O引脚作输出用

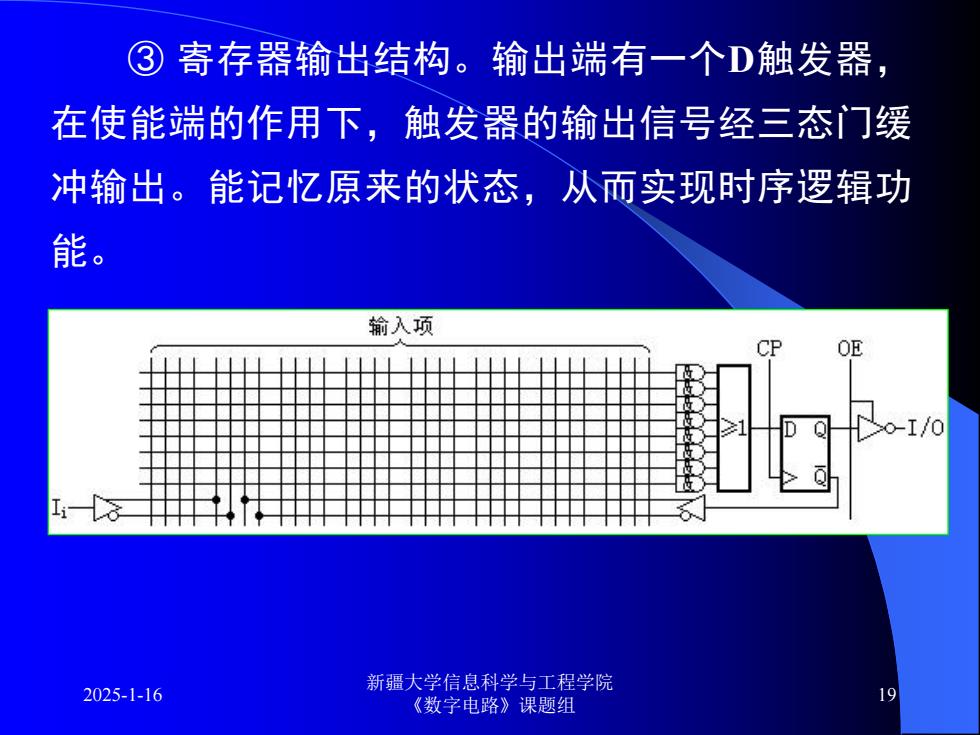

③寄存器输出结构。输出端有一个D触发器, 在使能端的作用下,触发器的输出信号经三态门缓 冲输出。能记忆原来的状态,从而实现时序逻辑功 能。 输入项 CP OE 0-I/0 新疆大学信息科学与工程学院 2025-1-16 《数字电路》课题组 19

2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 19 ③ 寄存器输出结构。输出端有一个D触发器, 在使能端的作用下,触发器的输出信号经三态门缓 冲输出。能记忆原来的状态,从而实现时序逻辑功 能

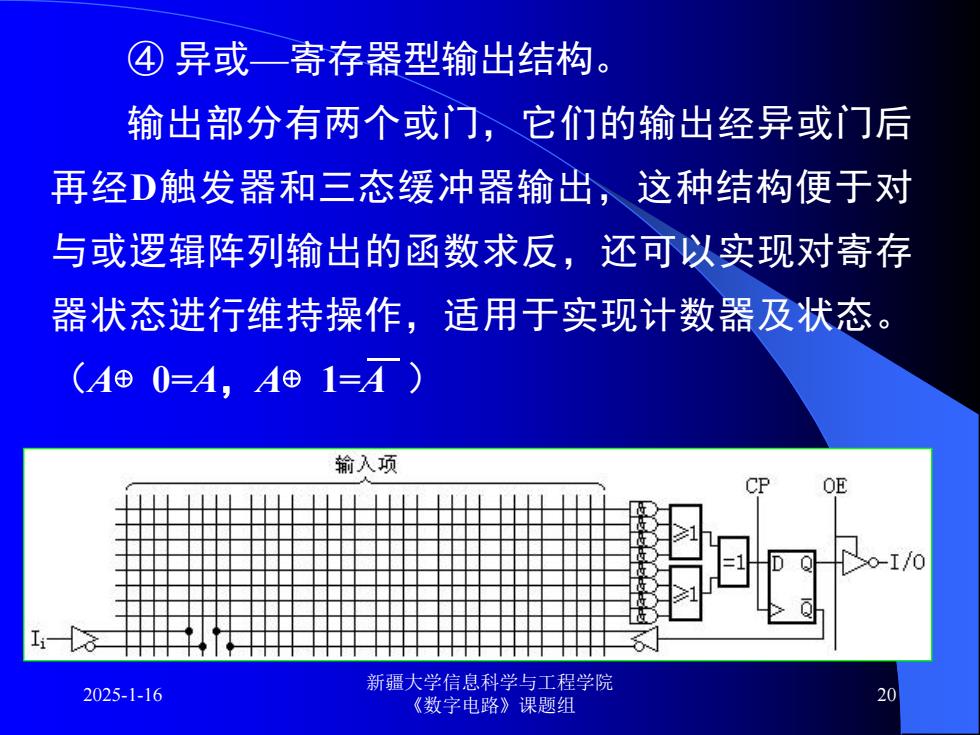

④异或一寄存器型输出结构。 输出部分有两个或门,它们的输出经异或门后 再经D触发器和三态缓冲器输出,这种结构便于对 与或逻辑阵列输出的函数求反,还可以实现对寄存 器状态进行维持操作,适用于实现计数器及状态。 (A⊕0=A,A⊕1=A) 输入项 CP OE o-I/0 2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 20

2025-1-16 新疆大学信息科学与工程学院 《数字电路》课题组 20 ④ 异或—寄存器型输出结构。 输出部分有两个或门,它们的输出经异或门后 再经D触发器和三态缓冲器输出,这种结构便于对 与或逻辑阵列输出的函数求反,还可以实现对寄存 器状态进行维持操作,适用于实现计数器及状态。 (A⊕ 0=A,A⊕ 1=A )