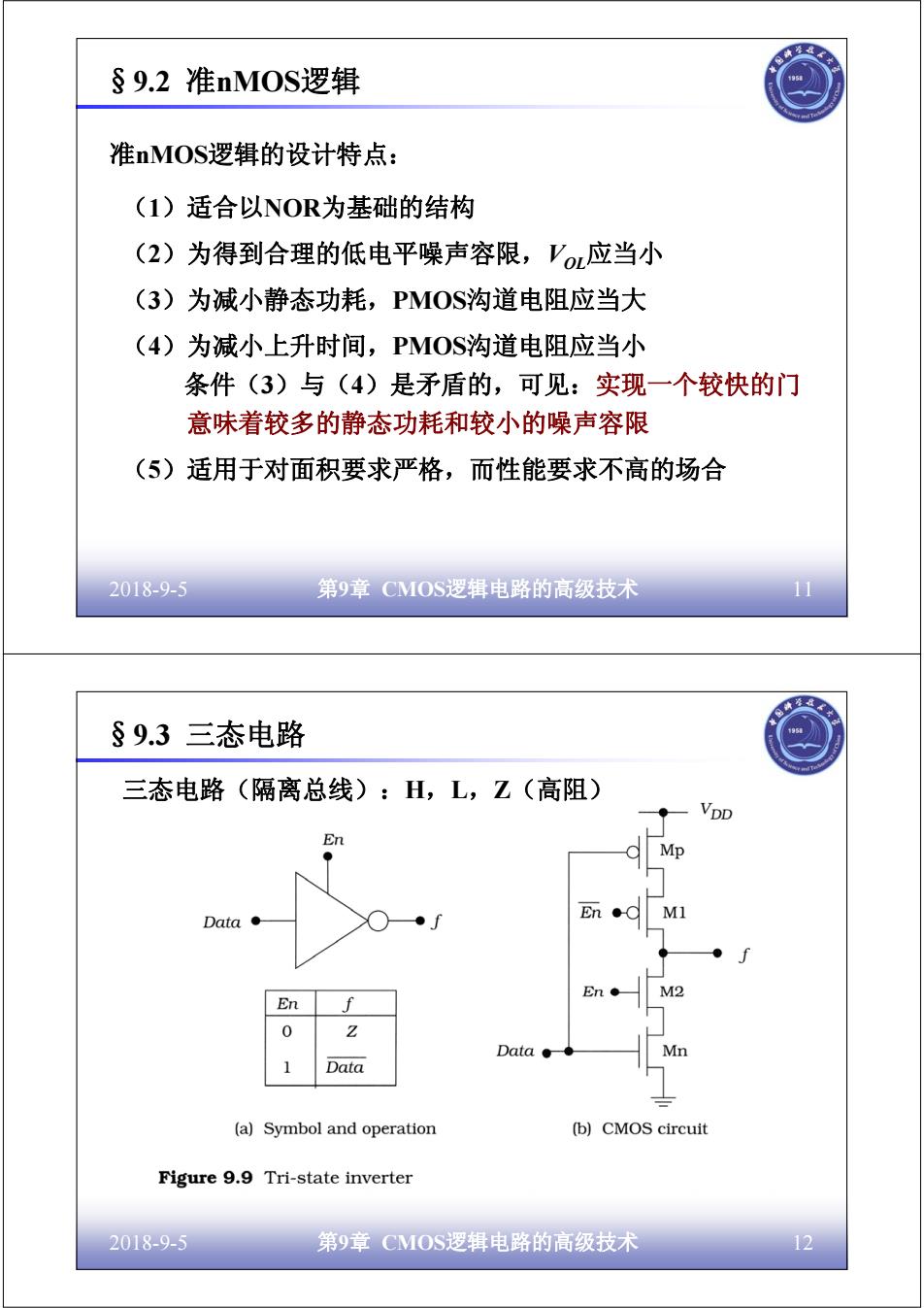

§9.2准nMOS逻辑 e 准nMOS逻辑的设计特点: (1)适合以NOR为基础的结构 (2)为得到合理的低电平噪声容限,Vo应当小 (3)为减小静态功耗,PMOS沟道电阻应当大 (4)为减小上升时间,PMOS沟道电阻应当小 条件(3)与(4)是矛盾的,可见:实现一个较快的门 意味着较多的静态功耗和较小的噪声容限 (5)适用于对面积要求严格,而性能要求不高的场合 2018-9-5 第9章CMOS逻辑电路的高级技术 §9.3 三态电路 三态电路(隔离总线):H,L,Z(高阻) VpD En Mp Data● En●- En● M2 En f 0 Z Data● 1 Data (a)Symbol and operation (b)CMOS circuit Figure 9.9 Tri-state inverter 2018-9-5 第9章CMOS逻辑电路的高级技术 12

2018-9-5 第9章 CMOS逻辑电路的高级技术 11 §9.2 准nMOS逻辑 准nMOS逻辑的设计特点: (1)适合以NOR为基础的结构 (2)为得到合理的低电平噪声容限,VOL应当小 (3)为减小静态功耗,PMOS沟道电阻应当大 (4)为减小上升时间,PMOS沟道电阻应当小 条件(3)与(4)是矛盾的,可见:实现一个较快的门 意味着较多的静态功耗和较小的噪声容限 (5)适用于对面积要求严格,而性能要求不高的场合 2018-9-5 第9章 CMOS逻辑电路的高级技术 12 §9.3 三态电路 三态电路(隔离总线):H,L,Z(高阻)

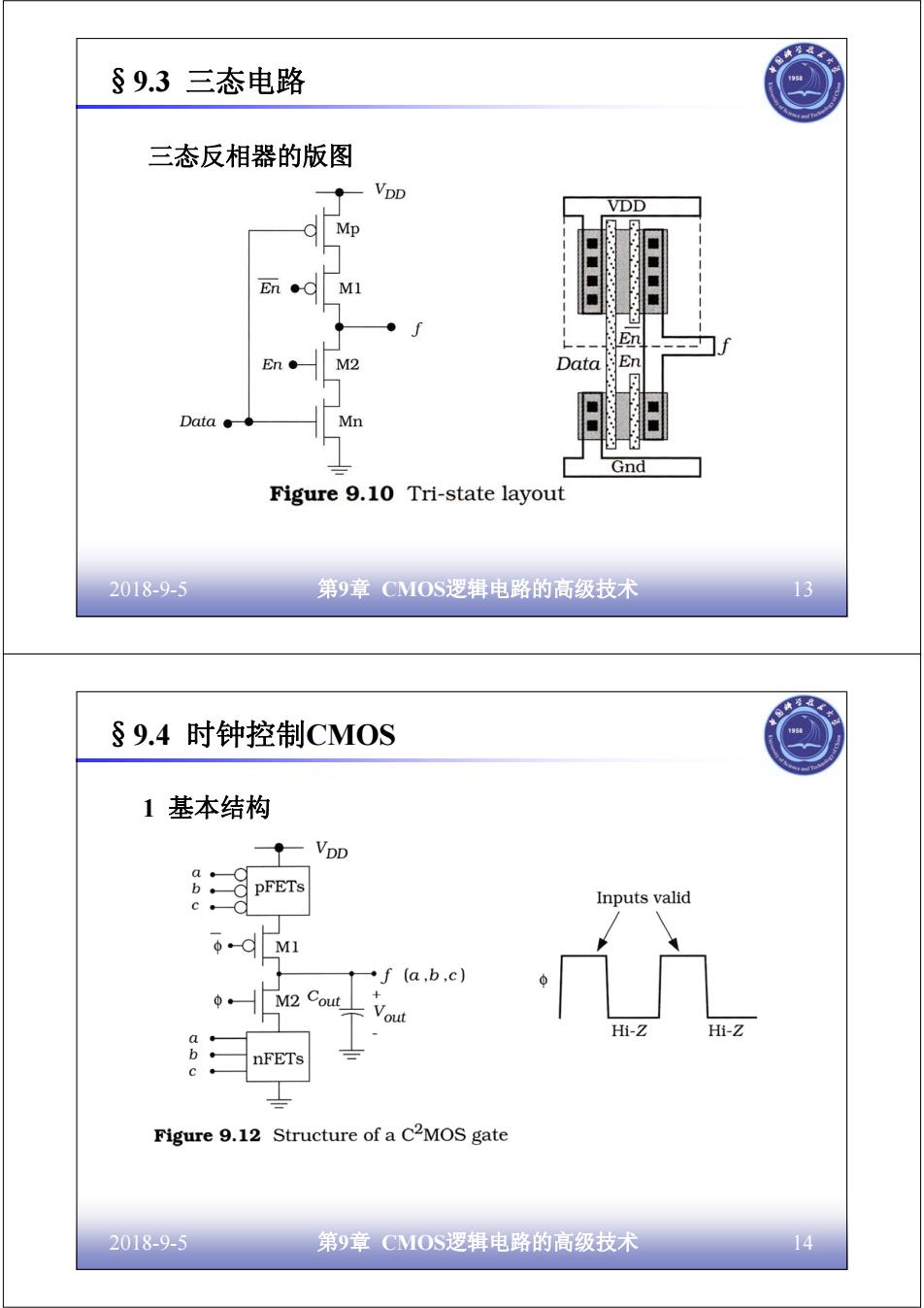

§9.3 三态电路 三态反相器的版图 VpD VDD MP En En● M2 Data En Data Mn Gnd Figure 9.10 Tri-state layout 2018-9-5 第9章CMOS逻辑电路的高级技术 13 §9.4时钟控制CMOS 1基本结构 VpD b·pFETs Inputs valid ·f(a,b,c) M2 Cout Vout Hi-Z Hi b nFETs Figure 9.12 Structure of a C2MOS gate 2018-9-5 第9章CMOS逻辑电路的高级技术 14

2018-9-5 第9章 CMOS逻辑电路的高级技术 13 §9.3 三态电路 三态反相器的版图 2018-9-5 第9章 CMOS逻辑电路的高级技术 14 §9.4 时钟控制CMOS 1 基本结构

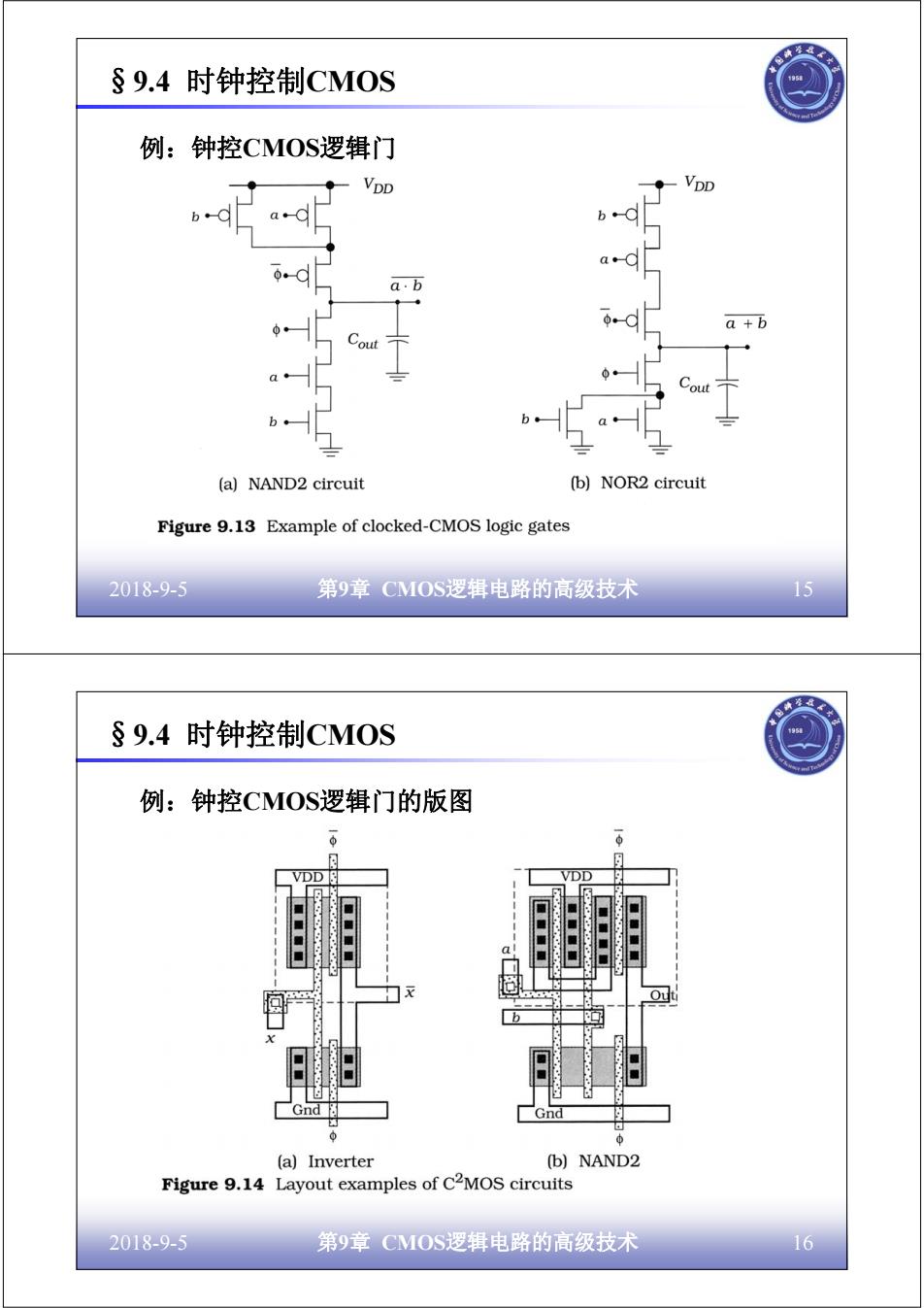

§9.4时钟控制CMOS 例:钟控CMOS逻辑门 VDD DD a·b a+b (a)NAND2 circuit (b)NOR2 circuit Figure 9.13 Example of clocked-CMOS logic gates 2018-9-5 第9章CMOS逻辑电路的高级技术 15 §9.4时钟控制CMOS 例:钟控CMOS逻辑门的版图 VDD VDD ● : a Gnd. Gnd (a)Inverter (b)NAND2 Figure 9.14 Layout examples of C2MOS circuits 2018-9-5 第9章CMOS逻辑电路的高级技术 16

2018-9-5 第9章 CMOS逻辑电路的高级技术 15 §9.4 时钟控制CMOS 例:钟控CMOS逻辑门 2018-9-5 第9章 CMOS逻辑电路的高级技术 16 §9.4 时钟控制CMOS 例:钟控CMOS逻辑门的版图