数模转换器简介 ● 分割结构一分段编码DAC 假定分段编码DAC中低B位采用二进制编码,高NB)位采用温度计编码,则仿照 前面的讨论,可知: ()(LSB) 从上面的分析中我们可以看出,对于DNL和glitch而言,温度计编码DAC性能最优, 分段编码次之,二进制编码最差。实际设计中,除了考虑这两方面因素外还要考虑芯片 面积这个因素,可结合设计的实际要求来选择结构。 综上所述,就一定输出动态范围和微分线性误差(DNL),并且忽略数字译码电 路的面积时,温度计编码所需要的面积最小,这样从理论上来说,温度计编码就具有最 小的芯片面积、微分线性误差(DNL)和毛刺(glitch)。实际上在分辨率很高时,数 字译码部分的面积会很快超过模拟部分的面积,而成为芯片面积的决定因素。所以对于 分辨率较高的情形,采用分段编码能兼顾芯片面积和精度这两方面的要求。这些也是本 文设计考虑到的问题,是本文设计的10位,100兆转换速率的数模转换器选择分段编码 结构的依据。 高速数模转换器的设计 11

数模转换器简介 高速数模转换器的设计 11 z 分割结构——分段编码DAC 假定分段编码DAC中低B位采用二进制编码,高(N-B)位采用温度计编码,则仿照 前面的讨论,可知: 1 ( ) () 2 1 ( ) B I I LSB I σ σ + ∆= − 从上面的分析中我们可以看出,对于DNL和glitch而言,温度计编码DAC性能最优, 分段编码次之,二进制编码最差。实际设计中,除了考虑这两方面因素外还要考虑芯片 面积这个因素,可结合设计的实际要求来选择结构。 综上所述,就一定输出动态范围和微分线性误差(DNL),并且忽略数字译码电 路的面积时,温度计编码所需要的面积最小,这样从理论上来说,温度计编码就具有最 小的芯片面积、微分线性误差(DNL)和毛刺(glitch)。实际上在分辨率很高时,数 字译码部分的面积会很快超过模拟部分的面积,而成为芯片面积的决定因素。所以对于 分辨率较高的情形,采用分段编码能兼顾芯片面积和精度这两方面的要求。这些也是本 文设计考虑到的问题,是本文设计的10位,100兆转换速率的数模转换器选择分段编码 结构的依据

10位,100兆采样速率数模转换器的设计 第三章10位,100兆转换速率数模转换器的设计 本章在第二章分析的基础上,综合考虑前面提到的各项指标,设计完成了一个10 位,100兆转换速率,分段编码的数模转换器(DAC)。 3.110位,100兆转换速率数模转换器的结构 在上章结束的时候,我们分析得到对于分辨率较高的DAC,采用分段编码结构能 兼顾芯片面积和精度这两方面的因素。所以本文设计采用的就是分段编码的形式。 分割结构采用“6+2+2”的形式,具体是高6位转换成温度计编码,中间2位也采用 温度计编码,这两种温度计编码是相互独立的,低2位采用的是二进制编码的形式。 图3.1为本文设计的DAC高6位的结构图,它包括电流源阵列、Ltch阵列、译码电 路(包括行译码电路和列译码电路)、选通电路、时钟缓冲器、输入寄存器,另外DAC中 还包括电流源的偏置电路(在图中未标明)等部分。对于低4位部分,与此大致相同, 不过译码和电流源阵列要简单得多。 下面我们对每个模块进行分析和设计,并给出仿真的结果。 Column Decoding Latchs current source Digital input cell array Out Clock Buffer Clock Input 图3.110位,100兆采样速率DAC的结构图 高速数模转换器的设计 12

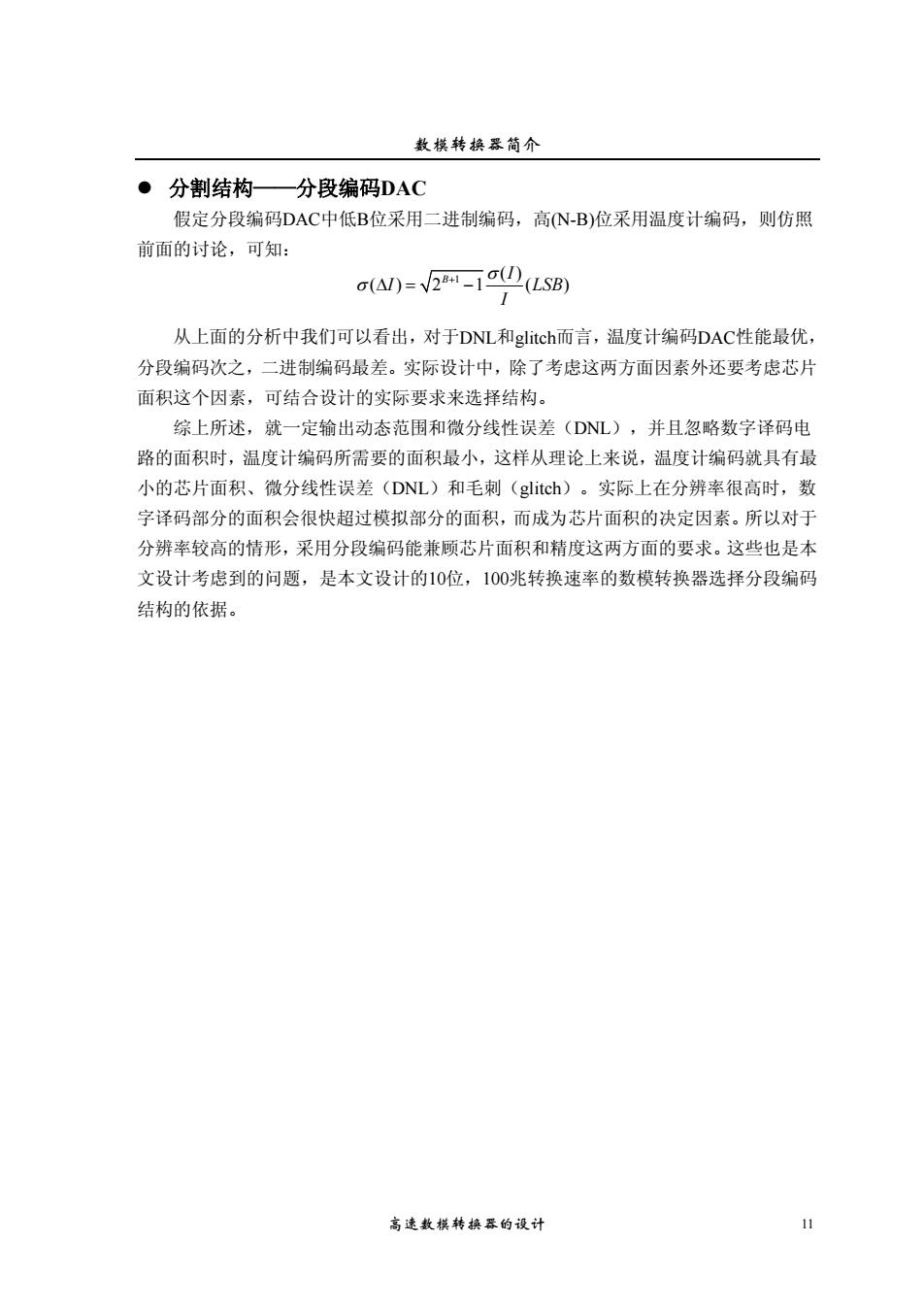

10 位,100 兆采样速率数模转换器的设计 高速数模转换器的设计 12 第三章 10 位,100 兆转换速率数模转换器的设计 本章在第二章分析的基础上,综合考虑前面提到的各项指标,设计完成了一个10 位,100兆转换速率,分段编码的数模转换器(DAC)。 3.1 10 位,100 兆转换速率数模转换器的结构 在上章结束的时候,我们分析得到对于分辨率较高的DAC,采用分段编码结构能 兼顾芯片面积和精度这两方面的因素。所以本文设计采用的就是分段编码的形式。 分割结构采用“6+2+2”的形式,具体是高6位转换成温度计编码,中间2位也采用 温度计编码,这两种温度计编码是相互独立的,低2位采用的是二进制编码的形式。 图3.1为本文设计的DAC高6位的结构图,它包括电流源阵列、Latch 阵列、译码电 路(包括行译码电路和列译码电路)、选通电路、时钟缓冲器、输入寄存器,另外DAC中 还包括电流源的偏置电路(在图中未标明)等部分。对于低4位部分,与此大致相同, 不过译码和电流源阵列要简单得多。 下面我们对每个模块进行分析和设计,并给出仿真的结果。 Column Decoding Row Decoding Input Register Clock Buffer Latchs Latchs current source cell array 图3.1 10位,100兆采样速率DAC的结构图 Digital input Clock Input Out

10位,100北采样速率数模转换器的设计 3.2“6+2+2”分割结构选择的原则 在上一章末,已经给出了二进制编码,温度计编码和分段编码的比较,文献[2]中给 出了三种编码的比较如图3.2所示。很明显,分段编码兼具了温度计编码和二进制编码 的优点,所以本文设计采用的是分段编码。文献[3]中给出了分段编码的划分比例与DAC 的性能(DNL、NL、面积)的关系图,如图3.3所示。图中的粗实线表示模拟部分的 面积与划分比例的关系,水平位置的面积最小,文献3]中分析仿真得知NL仅与模拟 部分的面积有关,而划分比例越大,DNL越小,但是一般情况下,系统对于NL的要 求比DNL要松,所以选择最优位置在水平线的末端,划分比例约为80%,也就是“8+2” 分割结构。文献[3]中还指出随着划分比例的增加,总谐波失真(THD)和glitch的能量 会减小,如图3.4所示。 High Resolution CMOS Current-Steering DAC B1 2 B1 BINARY UNARY B2 B2 41 B3 8 INL : B3 DNL Glltch Monotonicity Power 白 8则 + Area Complexity B2 41 SEGMENTED BO 白1 B3 .. B1 白21 8 图3.2 三种编码的比较 A total for DNL=0.5-Isb,INL=1.0-Isb THD oc Non-linear glitch energy A INL-0.5-isb ANL=1.08b A INL =20-sb 星 better HF THD 2 A DNL-0.5-isb 50 100 0 50 100 segmentation [% binary thermometer segmentation [% 图3.3NL、DNL和面积与划分比例的关系 图3.4THD和glitch能量与划分 比例的关系 高速数模转换器的设计 13

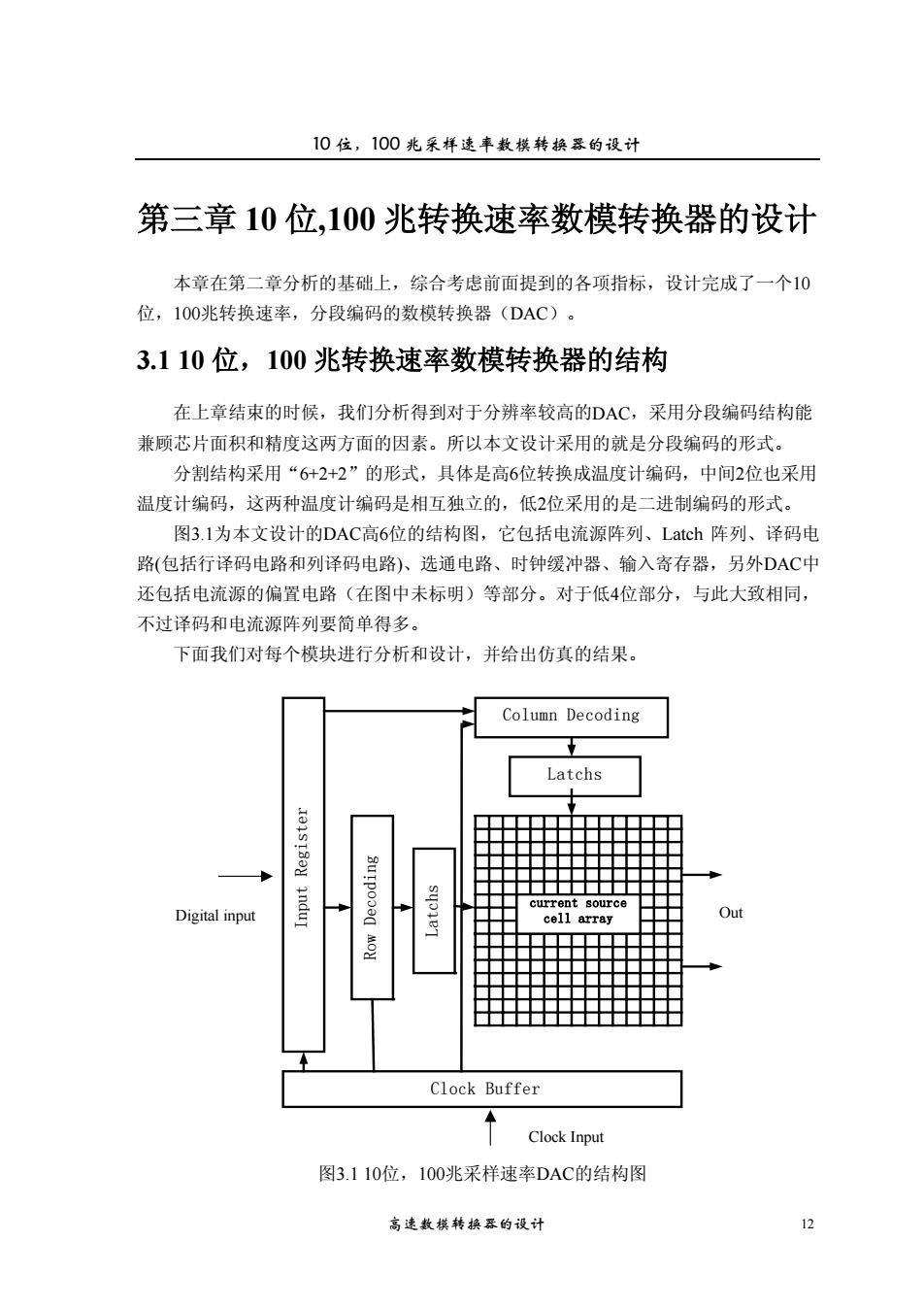

10 位,100 兆采样速率数模转换器的设计 高速数模转换器的设计 13 3.2 “6+2+2”分割结构选择的原则 在上一章末,已经给出了二进制编码,温度计编码和分段编码的比较,文献[2]中给 出了三种编码的比较如图 3.2 所示。很明显,分段编码兼具了温度计编码和二进制编码 的优点,所以本文设计采用的是分段编码。文献[3]中给出了分段编码的划分比例与 DAC 的性能(DNL、INL、面积)的关系图,如图 3.3 所示。图中的粗实线表示模拟部分的 面积与划分比例的关系,水平位置的面积最小,文献[3]中分析仿真得知 INL 仅与模拟 部分的面积有关,而划分比例越大,DNL 越小,但是一般情况下,系统对于 INL 的要 求比 DNL 要松,所以选择最优位置在水平线的末端,划分比例约为 80%,也就是“8+2” 分割结构。文献[3]中还指出随着划分比例的增加,总谐波失真(THD)和 glitch 的能量 会减小,如图 3.4 所示。 图 3.2 三种编码的比较 图 3.3 INL、DNL 和面积与划分比例的关系 图 3.4 THD 和 glitch 能量与划分 比例的关系

10位,100兆采样速率数模转换器的设计 但是采用“8+2”结构时,有4个行信号和4个列信号,译码电路比较复杂,占用芯 片的面积增加,而采用“6+2+2”结构,高8位仍为温度计编码,但是由于采用的是相互 独立的温度计编码,译码电路简单,面积减小,而且把高6位分为4个象限时,每个象 限中的64个单元只使用了63个,这样多余的4个单元刚好给中间2位的温度计编码使 用,不需要增加额外的单元,无需多余的硬件消耗。 3.3开关电路 与电流源电路一样,开关电路的设计也是多样化的。设计时主要考虑两个因素 导通电阻和时钟馈通(clock feedthrough)。设计时,应该尽可能地减小导通电阻和开关 引入的时钟馈通。在调节时,这两者之间存在一个折中(tradeoff)处理。 1)导通电阻 导通电阻必须比较低,这样才能降低开关管的电压降。所以在采用单个晶体管做开 关管的时候,管子的宽长比应该设置得比较大。 2)时钟馈通 由于开关上的电容耦合作用,时钟信号将会影响输出的模拟信号。时钟馈通会引起 总谐波失真,反映在电路的输出波形上同样是造成毛刺的存在。 尽可能减小开关引入的时钟馈通,这主要通过在保证电流切换速度的前提下,尽可 能减小WL来实现。因为这样可以有效地降低寄生电容,从而起到降低时钟馈通的作用。 但是必须注意开关管尺寸的减小又会引起导通电阻的上升,导通电阻升高引起开关管压 降升高,影响DAC电流源的线性度。因此开关管的尺寸也不能取得太小,要综合考虑 两个因素。 本文设计采用的是PMOS开关管,如图3.5所示。 3.4电流源阵列 电流源阵列是由电流源单元按照一定的形式组成的阵列,其基本单元是单个的 电流源,下面主要介绍电流源单元的设计。 图3.5PMOS开关管 高速数模转换器的设计 14

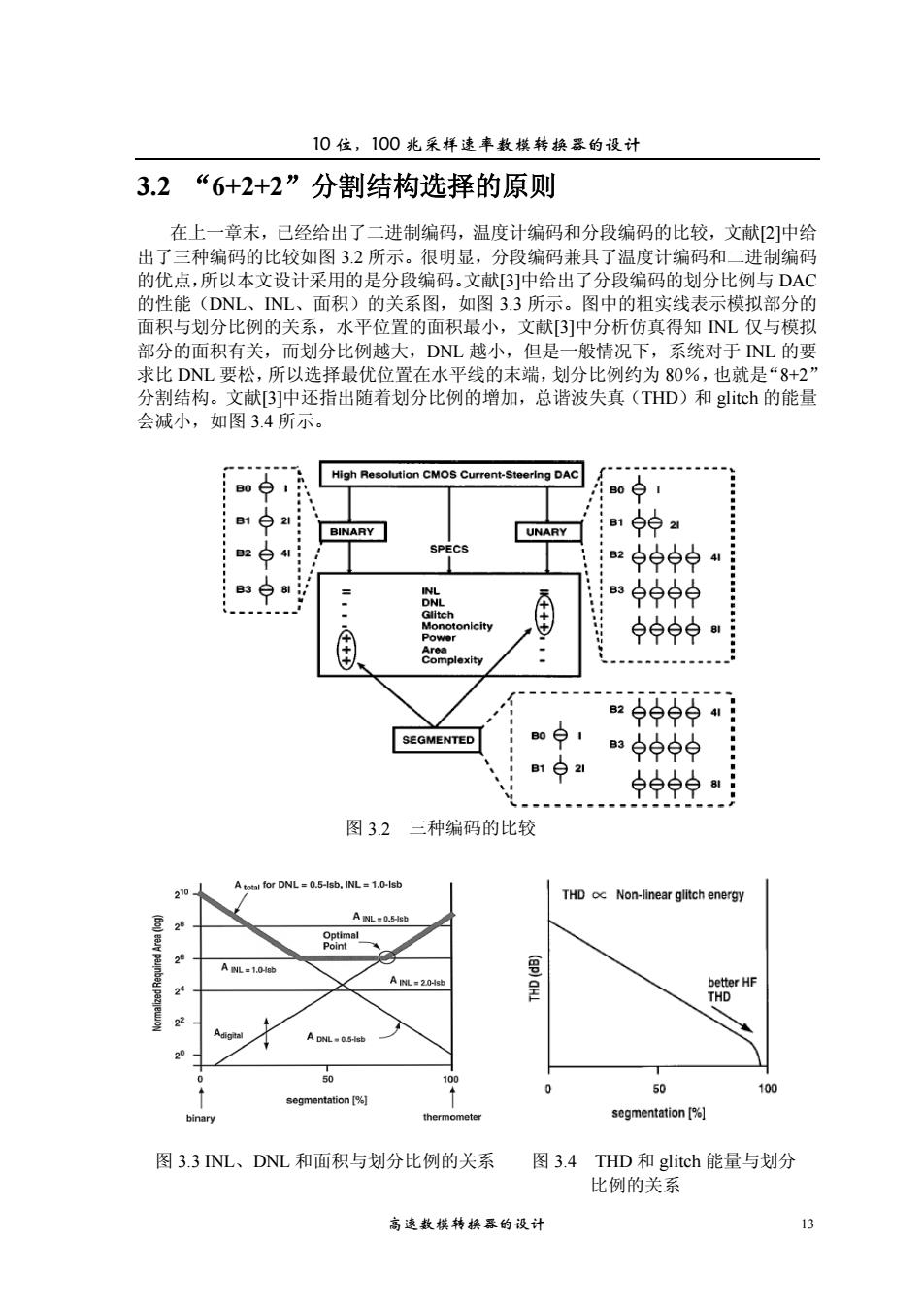

10 位,100 兆采样速率数模转换器的设计 高速数模转换器的设计 14 但是采用“8+2”结构时,有 4 个行信号和 4 个列信号,译码电路比较复杂,占用芯 片的面积增加,而采用“6+2+2”结构,高 8 位仍为温度计编码,但是由于采用的是相互 独立的温度计编码,译码电路简单,面积减小,而且把高 6 位分为 4 个象限时,每个象 限中的 64 个单元只使用了 63 个,这样多余的 4 个单元刚好给中间 2 位的温度计编码使 用,不需要增加额外的单元,无需多余的硬件消耗。 3.3 开关电路 与电流源电路一样,开关电路的设计也是多样化的。设计时主要考虑两个因素—— 导通电阻和时钟馈通(clock feedthrough)。设计时,应该尽可能地减小导通电阻和开关 引入的时钟馈通。在调节时,这两者之间存在一个折中(tradeoff)处理。 1)导通电阻 导通电阻必须比较低,这样才能降低开关管的电压降。所以在采用单个晶体管做开 关管的时候,管子的宽长比应该设置得比较大。 2)时钟馈通 由于开关上的电容耦合作用,时钟信号将会影响输出的模拟信号。时钟馈通会引起 总谐波失真,反映在电路的输出波形上同样是造成毛刺的存在。 尽可能减小开关引入的时钟馈通,这主要通过在保证电流切换速度的前提下,尽可 能减小W/L来实现。因为这样可以有效地降低寄生电容,从而起到降低时钟馈通的作用。 但是必须注意开关管尺寸的减小又会引起导通电阻的上升,导通电阻升高引起开关管压 降升高,影响DAC电流源的线性度。因此开关管的尺寸也不能取得太小,要综合考虑 两个因素。 本文设计采用的是PMOS开关管,如图3.5所示。 3.4 电流源阵列 电流源阵列是由电流源单元按照一定的形式组成的阵列,其基本单元是单个的 电流源,下面主要介绍电流源单元的设计。 图3.5 PMOS开关管 M1 Va M2 Vb

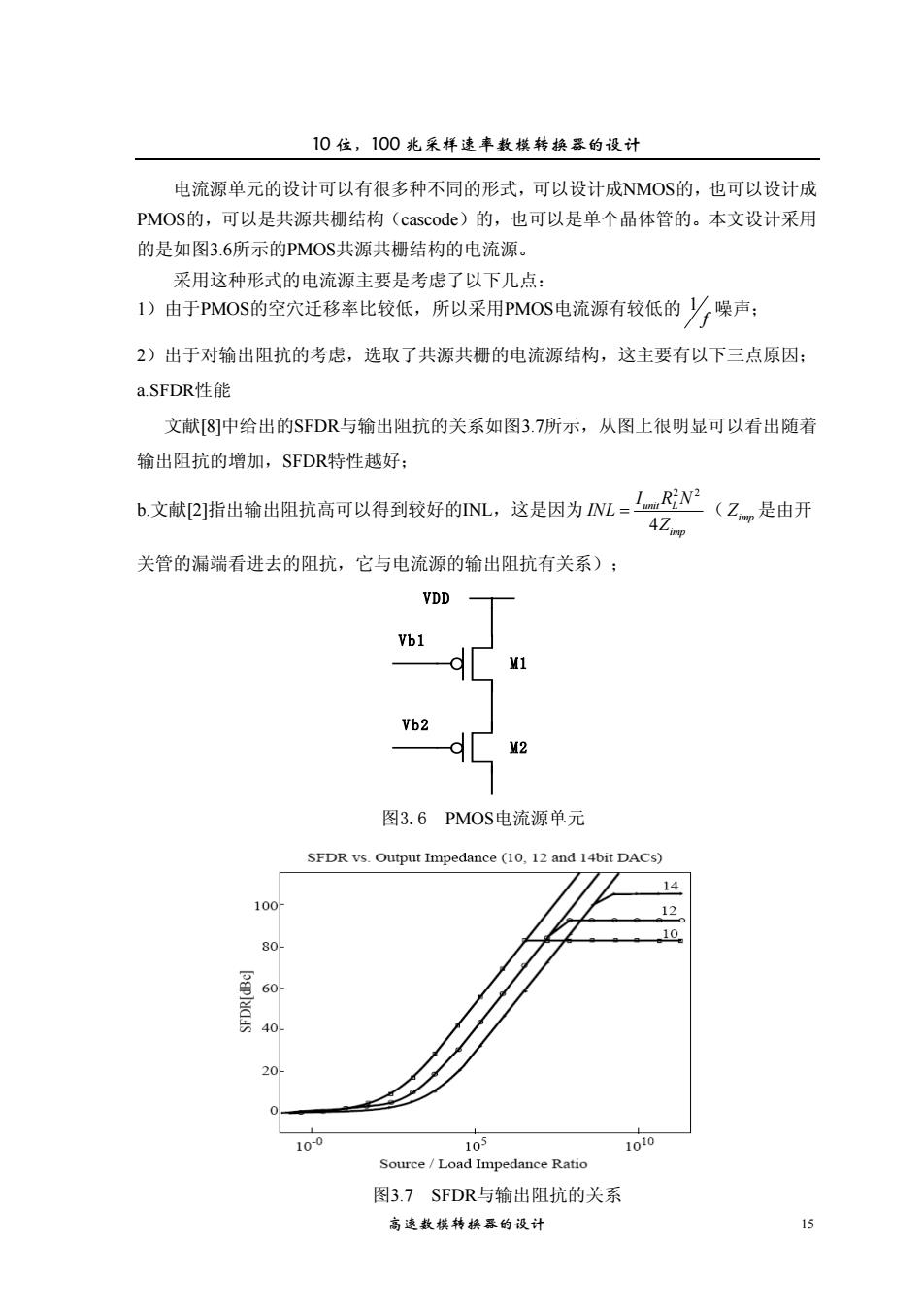

10位,100兆采样速率数模转换器的设计 电流源单元的设计可以有很多种不同的形式,可以设计成NMOS的,也可以设计成 PMOS的,可以是共源共栅结构(cascode)的,也可以是单个晶体管的。本文设计采用 的是如图3.6所示的PMOS共源共栅结构的电流源。 采用这种形式的电流源主要是考虑了以下几点: I)由于PMOS的空穴迁移率比较低,所以采用PMOs电流源有较低的片噪声: 2)出于对输出阻抗的考虑,选取了共源共栅的电流源结构,这主要有以下三点原因: a.SFDR性能 文献[8]中给出的SFDR与输出阻抗的关系如图3.7所示,从图上很明显可以看出随着 输出阻抗的增加,SFDR特性越好: b文献P脂出输出阻抗高可以得到较好的NL,这是因为ML='Y(乙是由开 AZimp 关管的漏端看进去的阻抗,它与电流源的输出阻抗有关系); VDD Vb1 Vb2 图3.6PMOS电流源单元 SFDR vs.Output Impedance (10,12 and 14bit DACs) 14 100 12 10 80 60 20 0 100 105 1010 Source/Load Impedance Ratio 图3.7SFDR与输出阻抗的关系 高速数模转换器的设计 15

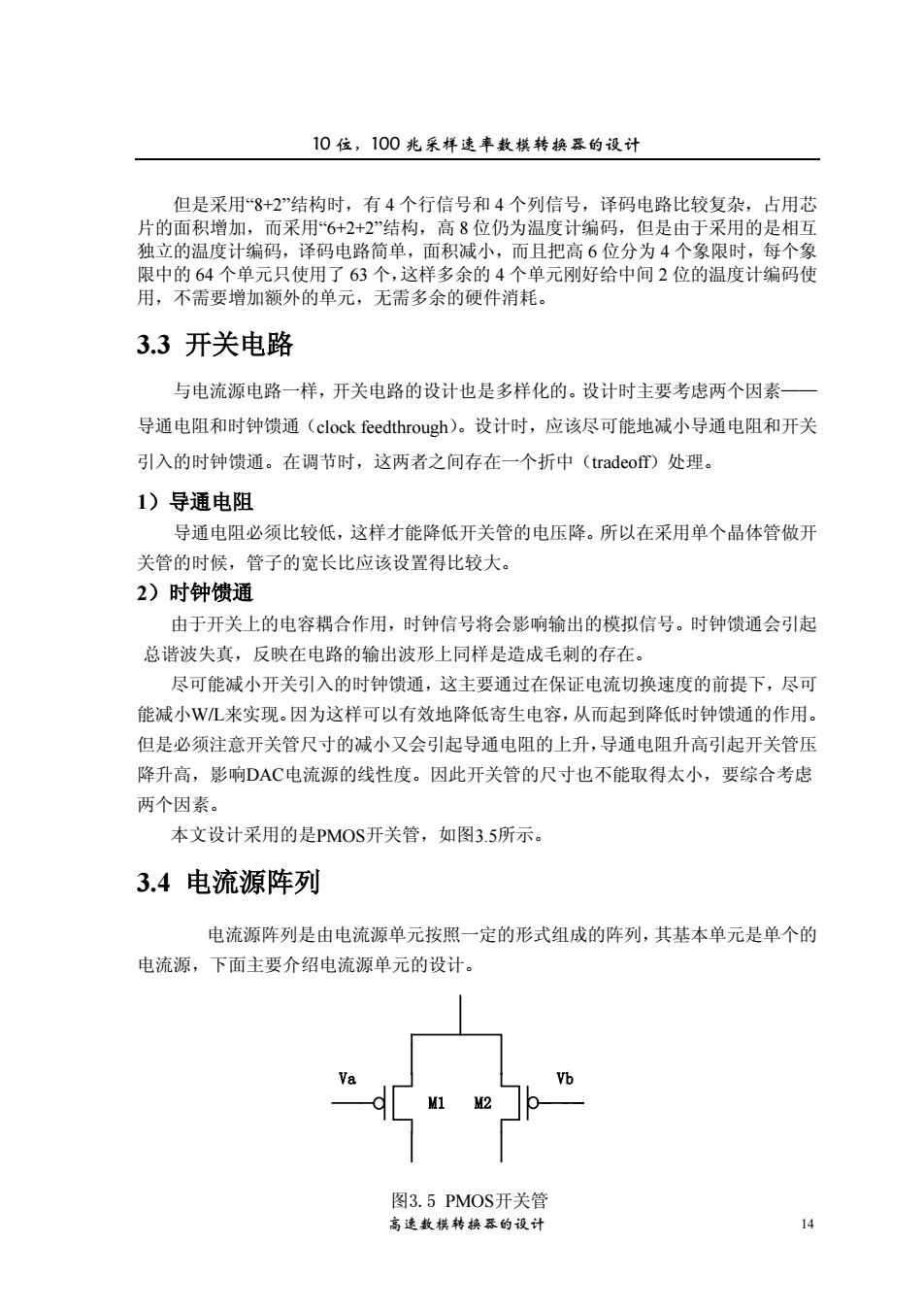

10 位,100 兆采样速率数模转换器的设计 高速数模转换器的设计 15 电流源单元的设计可以有很多种不同的形式,可以设计成NMOS的,也可以设计成 PMOS的,可以是共源共栅结构(cascode)的,也可以是单个晶体管的。本文设计采用 的是如图3.6所示的PMOS共源共栅结构的电流源。 采用这种形式的电流源主要是考虑了以下几点: 1)由于PMOS的空穴迁移率比较低,所以采用PMOS电流源有较低的 1 f 噪声; 2)出于对输出阻抗的考虑,选取了共源共栅的电流源结构,这主要有以下三点原因; a.SFDR性能 文献[8]中给出的SFDR与输出阻抗的关系如图3.7所示,从图上很明显可以看出随着 输出阻抗的增加,SFDR特性越好; b.文献[2]指出输出阻抗高可以得到较好的INL,这是因为 2 2 4 unit L imp I R N INL Z = ( Zimp 是由开 关管的漏端看进去的阻抗,它与电流源的输出阻抗有关系); M1 M2 VDD Vb1 Vb2 图3.6 PMOS电流源单元 图3.7 SFDR与输出阻抗的关系