第一章XSV800 Board简介 XSV800 Board提供各种各样的接口与外界进行通讯:串口, 并口,Xchecker电缆接口,USB接口,PS/2的鼠标键盘接口, 10/100以太网物理层接口。而主体部分是一块Virtex FPGA(XSV800)。一般通过串口,并口,Xchecker电缆来配置 Virtex FPGA,也可以通过存储在I6 M Flash RAM中的Bitstream 来配置。测试板的结构图如下(图1.1): 9 VDC Parallel Port Serial RCA S-Video Jack Port Jack Jack 5 DIP Sw. 16 Mbit Flash 0 日 骂 网 0 512KX8 西 的512Kx8 SRAM Virtex FPGA SRAM (XCV50-800) 马 r▣ 马 512K×8 凸 当 克512K×8 SRAM 遇 SRAM Pushbuttons F芭 H Ether Phy RAM DAC Stereo Stereo USB PS/2 RJ45 VGA Input Output Port Port Port Output (图1.1) 课题名称:数字视频编码器子模块的设计与优化 -1- PDF created with FinePrint pdfFactory trial version http://www.fineprint.com

课题名称:数字视频编码器子模块的设计与优化 - 1 - 第 一 章 XSV800 Board 简 介 XSV8 00 Board 提 供 各 种 各 样 的 接 口 与 外 界 进 行 通 讯 : 串 口 , 并 口 , Xc he cke r 电 缆 接 口 , USB 接 口 , PS/2 的 鼠 标 键 盘 接 口 , 10/ 10 0 以 太 网 物 理 层 接 口 。 而 主 体 部分是 一 块 Virt e x FPGA(XSV800) 。 一 般 通 过 串 口 , 并 口 , Xc he cke r 电缆来 配 置 Virtex FPGA, 也 可 以 通 过 存 储 在 16M Fl a s h RAM 中 的 Bitstream 来 配 置 。 测 试 板 的 结 构 图 如 下 (图 1.1): (图 1.1) PDF created with FinePrint pdfFactory trial version http://www.fineprint.com

XSV800 Board拥有的可用资源包括: Xilinx Virtex FPGA:Xilinx FPGA 57K Gates(XSV50) 888 K Gates(XSV800),它们都是采用240PIN的PQFP或HQFP 封装。这里是个888 K Gates的FPGA,它是这块XSV800 Board 的可编程逻辑的主要存储库。 Xilinx XC95108CPLD:用于通过串口,并口,或Flash RAM 来配置XSV800 Board,同时也控制着以太网芯片的配置。 可编程振荡器(Programmable Oscillator):以l00MHz的基 准频率为源向FPGA和CPLD提供时钟信号。 >16 M Flash RAM:存储FPGA所用配置信号和多用途的数据。 ,两组独立的512K*16 Bits SRAM:FPGA存储所要用的数据。 视频解码器(Video Decoder):通过RCA插孔或SVideo连 接器接受NTSC/PAL/SECAM信号并且向FPGA输出数字化的视 频信号。 ,RAMDAC:提供FPGA向显示器输出VGA信号的色彩表支 持。 ,立体声多媒体数字信号编码器(Stereo codec):数字化并产 生0一50KHz的音频信号。 P10/100的以太网芯片(10BASE-T/100BASE-TX Ethernet PHY Chip):FPGA用它来在LAN上以最高IO0Mbps接受或发送 数据。 )四按钮和一组DIP开关:向FPGA,CPLD提供多功能输入。 3根LED:显示FPGA,CPLD的状态信息。 PS/2鼠标键盘接口(Mouse/.Keyboard PS/2Port):让FPGA 能够使用通用的输入设备。 USB接口(USB port):向FPGA提供带宽为1.5tol2Mbps 的I/O信道。 串/并连接口(Parallel/Serial Port):可以让CPLD像PC一 样接受,发送串/并格式的数据。 Xchecker电缆接口(Xchecker Cable Interface):下载配置或 者读回配置。 ATX电源的连接器或者9V的直流电源插孔使得XSV800 Board可以接受标准的ATX电源或9V的直流电源。 课题名称:数字视频编码器子模块的设计与优化 -2- PDF created with FinePrint pdfFactory trial version http://www.fineprint.com

课题名称:数字视频编码器子模块的设计与优化 - 2 - XSV8 00 Boa r d 拥 有 的 可 用 资 源 包 括 : } Xilinx Virtex FPG A: Xili nx FPGA 从 57K Ga t e s (X SV5 0 )到 8 8 8K Gates(XSV800), 它 们 都 是 采 用 2 40PIN 的 PQFP 或 HQFP 封 装 。 这 里 是 个 88 8K Gat e s 的 FPGA, 它 是 这 块 XSV8 0 0 Board 的 可 编 程 逻 辑 的 主 要 存 储 库 。 } X ili nx XC9 51 08 CPLD:用 于 通 过 串 口 ,并 口 ,或 Fl a s h RAM 来 配 置 XSV8 00 Boa rd, 同 时 也 控 制 着 以 太 网 芯 片 的 配 置 。 } 可 编 程 振 荡 器 (Programmab l e Os cillator): 以 100MHz 的 基 准 频 率 为 源 向 FPGA 和 CPLD 提 供 时 钟 信 号 。 } 1 6M Fl a s h RAM:存 储 FPGA 所 用 配 置 信 号 和 多 用 途 的 数 据 。 } 两 组 独 立 的 512K* 1 6Bits SRAM:FPG A 存 储 所 要 用 的 数 据 。 } 视 频 解 码 器 (Vide o De c ode r): 通 过 RC A 插 孔 或 SVi de o 连 接 器 接 受 N TSC/PAL/SECAM 信 号 并 且 向 FPGA 输 出 数 字 化 的 视 频 信 号 。 } RAMDAC:提 供 FPGA 向 显 示 器 输 出 VGA 信 号 的 色 彩 表 支 持 。 } 立 体 声 多 媒 体 数 字 信 号 编 码 器 (St e r e o code c ): 数 字 化 并 产 生 0—50KHz 的 音 频 信 号 。 } 1 0/ 10 0 的 以 太 网 芯 片 ( 10BASE-T/10 0B ASE-TX Et he rnet PHY Chi p):FPG A 用 它 来 在 LA N 上 以 最 高 1 0 0 Mbps 接 受 或 发 送 数 据 。 } 四 按 钮 和 一 组 DIP 开 关 :向 FPGA,CPLD 提 供 多 功 能 输 入 。 } 3 根 LED: 显 示 FPGA,CPLD 的 状 态 信 息 。 } PS/2 鼠 标 键 盘 接 口 (Mou se/Keyboa rd PS/ 2 Po rt): 让 FPGA 能 够 使 用 通 用 的 输 入 设 备 。 } USB 接 口 (USB p o rt): 向 FPGA 提 供 带 宽 为 1. 5 t o 1 2 Mbp s 的 I/ O 信 道 。 } 串 /并 连 接 口 (Pa ra llel/Se rial Port): 可 以 让 CPLD 像 PC 一 样 接 受 , 发 送 串 /并 格 式 的 数 据 。 } Xc h e c ke r 电 缆 接 口 (Xc he cke r Ca ble In t e rface ): 下 载 配 置 或 者 读 回 配 置 。 ATX 电 源 的 连 接 器 或 者 9V 的 直 流 电 源 插 孔 使 得 XSV8 00 B o ard 可 以 接 受 标 准 的 ATX 电 源 或 9V 的 直 流 电 源 。 PDF created with FinePrint pdfFactory trial version http://www.fineprint.com

第二章视频信号输入处理 本章介绍系统处理全国电视委员会制式(NTSC)或顺序与存 储彩色电视系统制式(SECAM)或逐行倒相制式(PAL)的视频信号 的方案。 ◆2.1概述 在Active HDL上创建一个新的项目,实验中我将其命名为 Videoln,用以对FPGA编程,使其完成从特定的接口接受NTSC, SECAM.或PAL制式的视频信号,并将其数字化储存在测试板上的 缓冲区(两块独立的512Kx16SRAM)中的工作。上述程序可以通 过使用VHDL或Verilog来描述,这次实验中使用的是VHDL。这 个程序的最上层是一个名为saa7113的模块,且包含了以下子模 块:sram512 kleft16bit50mhz-sv01b(用来将数字化后视频信号 数据存入左侧的独立的SRAM中缓冲),prgramdac(用来对存有 8Bit色彩表的Ramdac编程),vgacore(创建显示器VGA同步信号 或其它控制信号)。 项目的主体部分是控制一个视频解码器(Video Decoder),其 型号是SAA7113,就是用它来完成将接收到的NTSC,SECAM, 或者PAL制式的视频信号数字化。数字化后的视频信号通过VPO 总线送到FPGA。这种数字化的视频数据的传送是用由视频解码 器(Video Decoder)发出的行锁时钟LLC(Line-locked Clock)的上 升沿同步的。而FPGA使用I2C总线(即串行数据线(SDA)和串 行时钟线(SCL))对SAA7113的视频选项编程。 ◆2.2关于I2C I2C总线在XSV800 Board上被普遍使用,因此为完成该项目 我必须对该总线结构有一个全面地了解。 串行扩展总线在单片机系统中的应用是目前单片机技术发 展的一种趋势。在目前比较流行的几种串行扩展总线中,I2C总 线以其严格的规范和众多带I2C接口的外围器件而获得广泛的 应用。I2C总线是由PHILIPS公司推出的芯片间串行传输总线。 它以1根串行数据线(SDA)和1根串行时钟线(SCL)实现了 全双工的同步数据传输。随着I2C总线研究的深入,它已经广泛 应用于视/音频领域、IC卡行业和一些家电产品中,在智能仪器、 仪表和工业测控领域也越来越多地得到应用。I2C总线的广泛应 用是同它卓越的性能和简便的操作方法分不开的。 (1)硬件结构上具有相同的硬件接口界面。I2C总线系统 课题名称:数字视频编码器子模块的设计与优化 -3- PDF created with FinePrint pdfFactory trial version http://www.fineprint.com

课题名称:数字视频编码器子模块的设计与优化 - 3 - 第二章 视 频 信 号 输 入 处 理 本 章 介 绍 系 统 处 理 全 国 电 视 委 员 会 制 式 (NTSC)或 顺 序 与 存 储 彩 色 电 视 系 统 制 式 (SECAM)或 逐 行 倒 相 制 式 (PAL)的 视 频 信 号 的 方 案 。 ¿2.1 概 述 在 Active HDL上 创 建 一 个 新 的 项 目 , 实 验 中 我 将 其 命 名 为 VideoIn,用 以 对 FPGA编 程 ,使 其 完 成 从 特 定 的 接 口 接 受 NTSC, SECA M或 PAL制 式 的 视 频 信 号 ,并 将 其 数 字 化 储 存 在 测 试 板 上 的 缓 冲 区 (两 块 独 立 的 51 2K x 1 6 SRAM)中 的 工 作 。上 述 程 序 可 以 通 过 使 用 VHDL或 Verilog来 描 述 , 这 次 实 验 中 使 用 的 是 VHDL。 这 个 程 序 的 最 上 层 是 一 个 名 为 saa7113的 模 块 ,且 包 含 了 以 下 子 模 块 : sram 512k left16bit50mhz-s v01b(用 来 将 数 字 化 后 视 频 信 号 数 据 存 入 左 侧 的 独 立 的 SRAM中 缓 冲 ), prgramdac(用 来 对 存 有 8Bit色 彩 表 的 Ramdac编 程 ), vgacore(创 建 显 示 器 VGA同 步 信 号 或 其 它 控 制 信 号 )。 项 目 的 主 体 部 分 是 控 制 一 个 视 频 解 码 器 (Vi deo De c oder),其 型 号 是 S AA7 11 3, 就 是 用 它 来 完 成 将 接 收 到 的 NTSC, SECAM, 或 者 PAL制 式 的 视 频 信 号 数 字 化 。数 字 化 后 的 视 频 信 号 通 过 VPO 总 线 送 到 FPGA。 这 种 数 字 化 的 视 频 数 据 的 传 送 是 用 由 视 频 解 码 器 (Vi deo Deco de r)发 出 的 行 锁 时 钟 LLC(Line-locked Cloc k)的 上 升 沿 同 步 的 。 而 FPGA使 用 I2C总 线 ( 即 串 行 数 据 线 ( SDA) 和 串 行 时 钟 线 ( SCL)) 对 SAA7113的 视 频 选 项 编 程 。 ¿2.2 关 于 I2C I2 C 总 线 在 XSV8 00 Board 上 被 普 遍 使 用 ,因 此 为 完 成 该 项 目 我 必 须 对 该 总 线 结 构 有 一 个 全 面 地 了 解 。 串 行 扩 展总线 在 单 片 机 系 统 中 的 应 用 是 目前单 片 机 技 术 发 展 的 一 种 趋 势 。 在 目 前 比 较 流 行 的 几 种 串 行 扩 展 总 线 中 , I2 C 总 线 以 其 严 格 的 规 范 和 众 多 带 I2C 接 口 的 外 围 器 件 而 获 得 广 泛 的 应 用 。 I2C 总 线 是 由 PHILIPS 公 司 推 出 的 芯 片 间 串 行 传 输 总 线 。 它 以 1 根 串 行 数 据 线 ( SDA) 和 1 根 串 行 时 钟 线 ( SC L) 实 现 了 全 双 工 的 同 步 数 据 传 输 。随 着 I2C 总 线 研 究 的 深 入 ,它 已 经 广 泛 应 用 于 视 /音 频 领 域 、IC 卡 行 业 和 一 些 家 电 产 品 中 ,在 智 能 仪 器 、 仪 表 和 工 业 测 控 领 域 也 越 来 越 多 地 得 到 应 用 。 I2C 总 线 的 广 泛 应 用 是 同 它 卓 越 的 性 能 和 简 便 的 操 作 方 法 分 不 开 的 。 ( 1) 硬 件 结 构 上 具 有 相 同 的 硬 件 接 口 界 面 。 I2C总 线 系 统 PDF created with FinePrint pdfFactory trial version http://www.fineprint.com

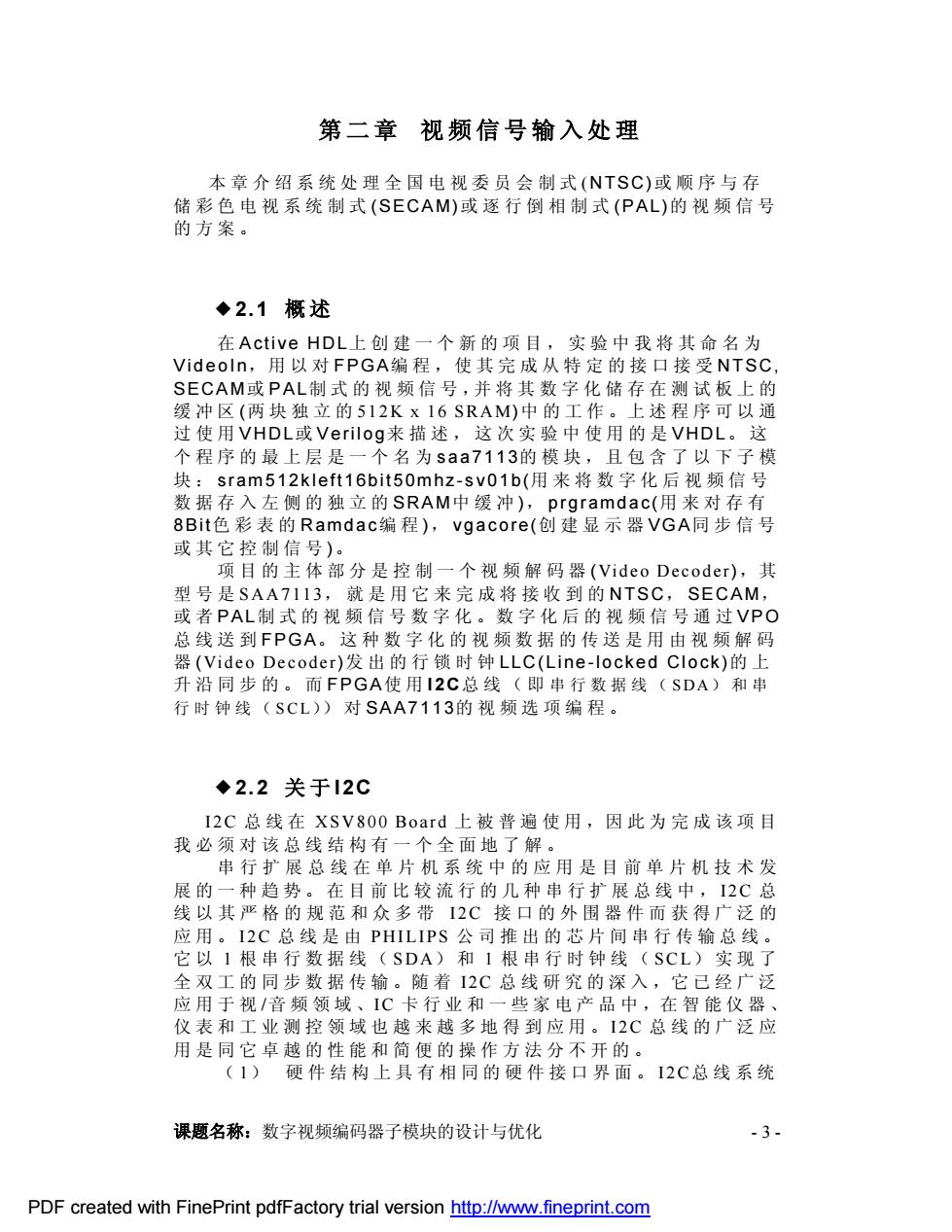

中,任何一个I2C总线接口的外围器件,不论其功能差别有多大, 都是通过串行数据线(SDA)和串行时钟线(SCL)连接到I2C 总线上。这一特点给用户在设计应用系统中带来了极大的便利 性。用户不必理解每个I2C总线接口器件的功能如何,只要将器 件的SDA和SCL引脚连到I2C总线上,然后对该器件模块进行独立 的电路设计,从而简化了系统设计的复杂性,提高了系统抗干扰 的能力,符合EMC(Electromagnetic Compatibility)设计原则。 (2)总线接口器件地址具有很大的独立性。在单主系统 中,每个I2C接口芯片具有惟一的器件地址,由于不能发出串行 时钟信号而只能作为从器件使用。各器件之间互不干扰,相互之 间不能进行通信,各个器件可以单独供电。MCU与I2C器件之间 的通信是通过独一无二的器件地址来实现的。 (3)软件操作的一致性。由于任何器件通过I2C总线与 MCU进行数据传送的方式是基本一样的,这就决定了I2C总线软 件编写的一致性。 (4)PHILIPS公司在推出I2C总线的同时,也为I2C总线制 订了严格的规范,如:接口的电气特性、信号时序、信号传输的 定义等。规范的严密性,结构的独立性和硬、软件接口界面的 致性,极大地方便了I2C总线的设计。模块化和规范化,伴随而 来的是用户在使用I2C总线时的“傻瓜”化。 ◆2.3 PrgRamdaci程序及其控制的RAMDAC RAMDAC与FPGA的连接如下图(图2.1)所示,用这个连接方 式来向外提供一个VGA接口。FPGA产生的视频信号可以直接显 示或通过一个BT481 A RAMDAC在一台VGA显示器上显示。 ◆syn VGA Connector (4 J59 fed blank red Virtex pixelclk BT481A green greer J69 FPGA RAMDAC J7。 blue blue (图2.1) 课题名称:数字视频编码器子模块的设计与优化 -4- PDF created with FinePrint pdfFactory trial version http://www.fineprint.com

课题名称:数字视频编码器子模块的设计与优化 - 4 - 中 ,任 何 一 个 I2C总 线 接 口 的 外 围 器 件 ,不 论 其 功 能 差 别 有 多 大 , 都 是 通 过 串 行 数 据 线 ( SDA) 和 串 行 时 钟 线 ( SC L) 连 接 到 I2C 总 线 上 。 这 一 特 点 给 用 户 在 设 计 应 用 系 统 中 带 来 了 极 大 的 便 利 性 。 用 户 不 必 理 解 每 个 I2 C总 线 接 口 器 件 的 功 能 如 何 , 只 要 将 器 件 的 SDA和 SC L引 脚 连 到 I2 C总 线 上 ,然 后 对 该 器 件 模 块 进 行 独 立 的 电 路 设 计 ,从 而 简 化 了 系 统 设 计 的 复 杂 性 ,提 高 了 系 统 抗 干 扰 的 能 力 , 符 合 EMC (Elec tromagnetic Compa tibili t y)设 计 原 则 。 ( 2) 总 线 接 口 器 件 地 址 具 有 很 大 的 独 立 性 。 在 单 主 系 统 中 , 每 个 I2 C接 口 芯 片 具 有 惟 一 的 器 件 地 址 , 由 于 不 能 发 出 串 行 时 钟 信 号 而 只 能 作 为 从 器 件 使 用 。各 器 件 之 间 互 不 干 扰 ,相 互 之 间 不 能 进 行 通 信 , 各 个 器 件 可 以 单 独 供 电 。 MC U与 I2C器 件 之 间 的 通 信 是 通 过 独 一 无 二 的 器 件 地 址 来 实 现 的 。 ( 3) 软 件 操 作 的 一 致 性 。 由 于 任 何 器 件 通 过 I2C总 线 与 MCU进 行 数 据 传 送 的 方 式 是 基 本 一 样 的 , 这 就 决 定 了 I2C总 线 软 件 编 写 的 一 致 性 。 ( 4) PHILIPS公 司 在 推 出 I2C总 线 的 同 时 ,也 为 I2 C总 线 制 订 了 严 格 的 规 范 ,如 :接 口 的 电 气 特 性 、信 号 时 序 、信 号 传 输 的 定 义 等 。规 范 的 严 密 性 ,结 构 的 独 立 性 和 硬 、软 件 接 口 界 面 的 一 致 性 , 极 大 地 方 便 了 I2C总 线 的 设 计 。 模 块 化 和 规 范 化 , 伴 随 而 来 的 是 用 户 在 使 用 I2C总 线 时 的 “傻 瓜 ”化 。 ¿2.3 PrgRamdac程 序 及 其控制的 RAMDAC RAMDAC与 FPGA的 连 接 如 下 图 (图 2.1)所 示 ,用 这 个 连 接 方 式 来 向 外 提 供 一 个 VGA接 口 。 FPGA产 生 的 视 频 信 号 可 以 直 接 显 示 或 通 过 一 个 BT481A RA MDAC在 一 台 VGA显 示 器 上 显 示 。 (图 2.1) PDF created with FinePrint pdfFactory trial version http://www.fineprint.com

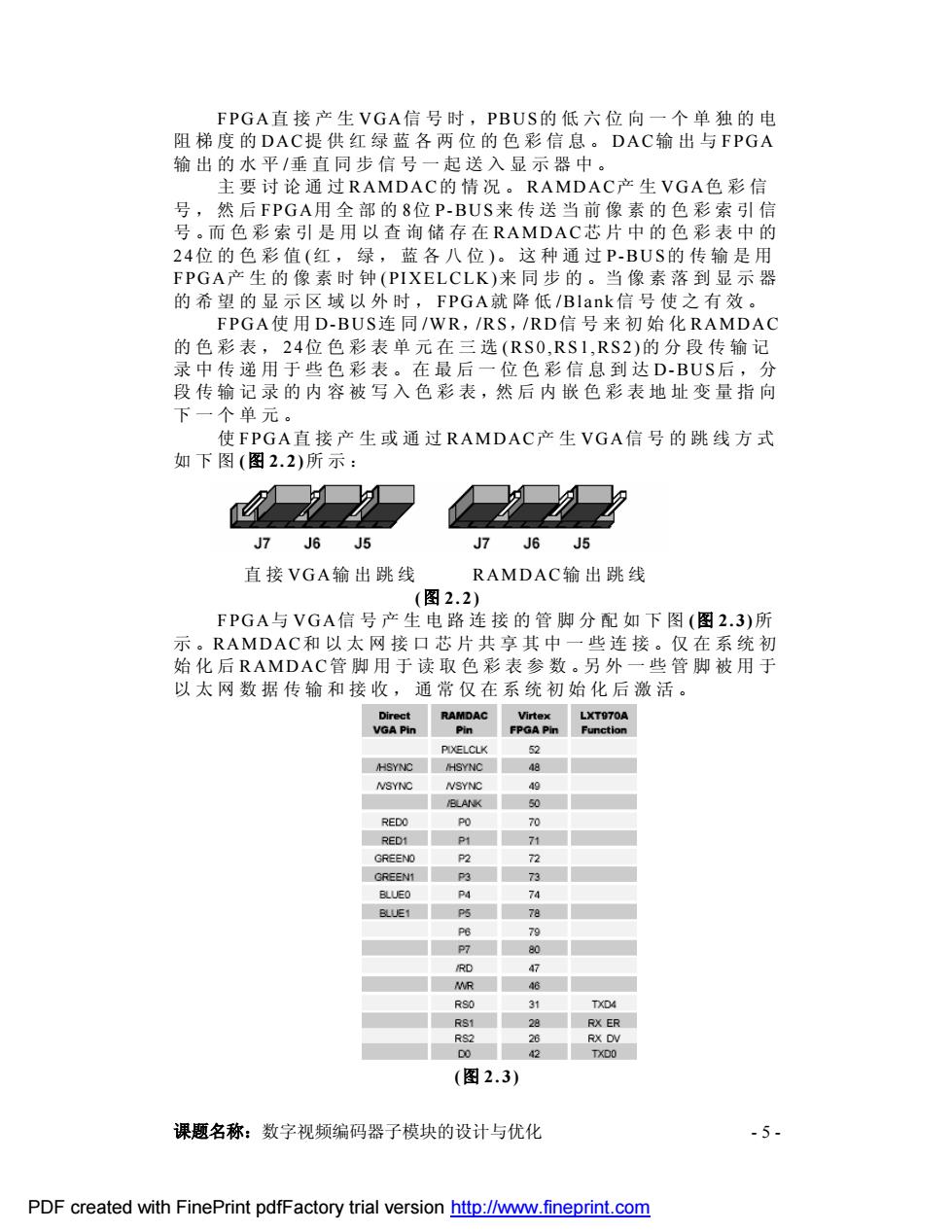

FPGA直接产生VGA信号时,PBUS的低六位向一个单独的电 阻梯度的DAC提供红绿蓝各两位的色彩信息。DAC输出与FPGA 输出的水平/垂直同步信号一起送入显示器中。 主要讨论通过RAMDAC的情况。RAMDAC产生VGA色彩信 号,然后FPGA用全部的8位P-BUS来传送当前像素的色彩索引信 号。而色彩索引是用以查询储存在RAMDAC芯片中的色彩表中的 24位的色彩值(红,绿,蓝各八位)。这种通过P-BUS的传输是用 FPGA产生的像素时钟(PIXELCLK)来同步的。当像素落到显示器 的希望的显示区域以外时,FPGA就降低/Blank信号使之有效。 FPGA使用D-BUS连同IWR,/RS,IRD信号来初始化RAMDAC 的色彩表,24位色彩表单元在三选(RS0,RS1,RS2)的分段传输记 录中传递用于些色彩表。在最后一位色彩信息到达D-BUS后,分 段传输记录的内容被写入色彩表,然后内嵌色彩表地址变量指向 下一个单元。 使FPGA直接产生或通过RAMDAC产生VGA信号的跳线方式 如下图(图2.2)所示: J7 J6 J5 J7 J6 J5 直接VGA输出跳线 RAMDAC输出跳线 (图2.2) FPGA与VGA信号产生电路连接的管脚分配如下图(图2.3)所 示。RAMDAC和以太网接口芯片共享其中一些连接。仅在系统初 始化后RAMDAC管脚用于读取色彩表参数。另外一些管脚被用于 以太网数据传输和接收,通常仅在系统初始化后激活。 Direct RAMDAC Virtex LXT970A VGA Pin Pin FPGA Pin Function PIXELCLK 52 HSYNC /HSYNC NSYNC NSYNC 49 /BLANK 50 REDO PO 70 RED1 P1 71 GREEND 2 72 GREEN1 P3 73 BLUEO P4 74 BLUE1 P5 78 P6 79 P7 /RD 47 MR 6 RSO 31 TXD4 RS1 28 RX ER RS2 28 RX DV DO 42 TXDO (图2.3) 课题名称:数字视频编码器子模块的设计与优化 -5 PDF created with FinePrint pdfFactory trial version http://www.fineprint.com

课题名称:数字视频编码器子模块的设计与优化 - 5 - FPGA直 接 产 生 VGA信 号 时 ,PBUS的 低 六 位 向 一 个 单 独 的 电 阻 梯 度 的 DA C提 供 红 绿 蓝 各 两 位 的 色 彩 信 息 。 DA C输 出 与 FPG A 输 出 的 水 平 /垂 直 同 步 信 号 一 起 送 入 显 示 器 中 。 主 要 讨 论 通 过 RAMDAC的 情 况 。 RAMDAC产 生 VGA色 彩 信 号 , 然 后 FPGA用 全 部 的 8位 P-BUS来 传 送 当 前 像 素 的 色 彩 索 引 信 号 。而 色 彩 索 引 是 用 以 查 询 储 存 在 RAM DAC芯 片 中 的 色 彩 表 中 的 2 4位 的 色 彩 值 (红 , 绿 , 蓝 各 八 位 )。 这 种 通 过 P-BUS的 传 输 是 用 FPGA产 生 的 像 素 时 钟 (PIXELCLK)来 同 步 的 。当 像 素 落 到 显 示 器 的 希 望 的 显 示 区 域 以 外 时 , FPGA就 降 低 /Blank信 号 使 之 有 效 。 FPGA使 用 D-BUS连 同 /WR,/R S,/RD信 号 来 初 始 化 RAM DAC 的 色 彩 表 , 2 4位 色 彩 表 单 元 在 三 选 (RS0,RS1,RS2 )的 分 段 传 输 记 录 中 传 递 用 于 些 色 彩 表 。在 最 后 一 位 色 彩 信 息 到 达 D-BUS后 ,分 段 传 输 记 录 的 内 容 被 写 入 色 彩 表 ,然 后 内 嵌 色 彩 表 地 址 变 量 指 向 下 一 个 单 元 。 使 FPGA直 接 产 生 或 通 过 RAM DAC产 生 VG A信 号 的 跳 线 方 式 如 下 图 (图 2.2)所 示 : 直 接 VG A输 出 跳 线 RAM DAC输 出 跳 线 (图 2.2) FPGA与 VGA信 号 产 生 电 路 连 接 的 管 脚 分 配 如 下 图 (图 2.3)所 示 。RAMDAC和 以 太 网 接 口 芯 片 共 享 其 中 一 些 连 接 。仅 在 系 统 初 始 化 后 RAMDAC管 脚 用 于 读 取 色 彩 表 参 数 。另 外 一 些 管 脚 被 用 于 以 太 网 数 据 传 输 和 接 收 , 通 常 仅 在 系 统 初 始 化 后 激 活 。 (图 2.3) PDF created with FinePrint pdfFactory trial version http://www.fineprint.com