復旦大等 州H州拉容 州收你口景共这士只盗账名 版(监) 田作价恤的帐行 数 T 杀置 n 9721004 要吵懿 趣丝名 R橙血聚 2001母6四8▣

1 系 ( 所 ) : 电 子 工 程 系 专 业 : 电 子 学 与 信 息 系 统 姓 名 : 祝 永 明 学 号 : 9721004 指 导 教 师 : 唐 长 文 完 成 日 期 : 2001 年 6 月 8 日 学 士 学 位 论 文 数 字 系 统 可 测 性 设 计 方 法 的 探 讨

兹外巴资日口冕型赵士R兴留举空 絮的 摘要 本文主要探讨了用全扫描传构(FULL SCAN METHOD)来实视数字电路 可测性设计(DESIGN FOR TEST)的原理与方法。其中涉及到扫描结构 (SCAN)的算法依据、电路的基本待构、测试失量的生成(ATPG)以.及测 试的时序等诸多向题。并结合最常用的综合三具SYNOPSYS中的DFT COMPILER部分,深入描述了为一教字电路芯件加入扫描部分和产生 测试失量集的具体流程。加描结构对数字电路的结构有一些限制,为了 避免违反这些限制,文中罗列了所谓的设外规范,并徉细介绍了如何对 违反这些没计规范的电路进行修改和处理的方法

数 字 电 路 可 测 性 设 计 方 法 的 探 讨 摘 要 I 摘 要 本文主要探讨了用全扫描结构(FULL SCAN METHOD)来实现数字电路 可测性设计(DESIGN FOR TEST)的原理与方法。其中涉及到扫描结构 (SCAN)的算法依据、电路的基本结构、测试矢量的生成(ATPG)以及测 试的时序等诸多问题。并结合最常用的综合工具 SYNOPSYS 中的 DFT COMPILER 部分,深入描述了为一数字电路芯片加入扫描部分和产生 测试矢量集的具体流程。扫描结构对数字电路的结构有一些限制,为了 避免违反这些限制,文中罗列了所谓的设计规范,并详细介绍了如何对 违反这些设计规范的电路进行修改和处理的方法

兹外已资日暴型赵士R兴超举女 匹悦 悦 L.可测性设计的概念及发展状况1 1.1可测性设计的度量… a.1 1.2可测性设计的分类1 1.3测试矢量与测试码自动生成 .2 1.4故障覆盖率… ..2 2.D算法的原理及实现方法.… 3 2.1故障模型… .3 2.2敏化路径法..... .3 2.3D算法简介… .4 3.SYNOPSYS中的测试部分及扫描结构. 6 3.1 SYNOPSYS中扫描电路的基本结构. 6 3.2扫描测试的协议及时序..… 8 3.3各阶段各管脚具体的时序图… .8 4.扫描电路的加入及ATPG的产生过程. .11 4.1对未布线源文件加入扫描电路的流程. .11 4.2对源文件进行综合及测试预备编译. .13 4.3建立扫描通路.… .15 4.4礼州景归以兴… .16 4.5对已编译电路及已有扫描路径的处理 .17 4.6 CHECK TEST命令的应用.… .18 4.7ATPG的产生及原理.… .20 5.扫描结构对电路的限制.… 23 5.1电路中需增加的管脚. .23 5.2避免使用LATCH.. 23 5.3避免产生组合电路的反馈.. .23

数 字 电 路 可 测 性 设 计 方 法 的 探 讨 目 录 I 目 录 1. 可测性设计的概念及发展状况....................................................................1 1.1 可测性设计的度量..............................................................................1 1.2 可测性设计的分类..............................................................................1 1.3 测试矢量与测试码自动生成 ..............................................................2 1.4 故障覆盖率.........................................................................................2 2. D 算法的原理及实现方法............................................................................3 2.1 故障模型.............................................................................................3 2.2 敏化路径法.........................................................................................3 2.3 D 算法简介..........................................................................................4 3. SYNOPSYS 中的测试部分及扫描结构........................................................6 3.1 SYNOPSYS 中扫描电路的基本结构...................................................6 3.2 扫描测试的协议及时序.......................................................................8 3.3 各阶段各管脚具体的时序图................................................................8 4. 扫描电路的加入及 ATPG 的产生过程........................................................11 4.1 对未布线源文件加入扫描电路的流程................................................11 4.2 对源文件进行综合及测试预备编译...................................................13 4.3 建立扫描通路...................................................................................15 4.4 产 生 测 试 矢 量 集 ................................................................................16 4.5 对已编译电路及已有扫描路径的处理................................................17 4.6 CHECK TEST 命令的应用...............................................................18 4.7 ATPG 的产生及原理.........................................................................20 5. 扫描结构对电路的限制.............................................................................23 5.1 电路中需增加的管脚.........................................................................23 5.2 避免使用LATCH...............................................................................23 5.3 避免产生组合电路的反馈..................................................................23

兹外已资日暴型赵士R兴超举女 匹悦 5.4对时钟信号及复位信号的限制.… .24 5.5对三态总线的限制.25 6.对有问题电路进行的修改.… 26 6.1手动修改… 26 6.2 自动修改… .31 6.3安h巡R的泾斯… .32 总结 33 致谢… 33 参考文献 34

数 字 电 路 可 测 性 设 计 方 法 的 探 讨 目 录 II 5.4 对时钟信号及复位信号的限制..........................................................24 5.5 对三态总线的限制............................................................................25 6. 对有问题电路进行的修改..........................................................................26 6.1 手动修改...........................................................................................26 6.2 自动修改...........................................................................................31 6.3 对 于 修 改 方 法 的 小 结 .........................................................................32 总结................................................................................................................33 致谢................................................................................................................33 参考文献.........................................................................................................34

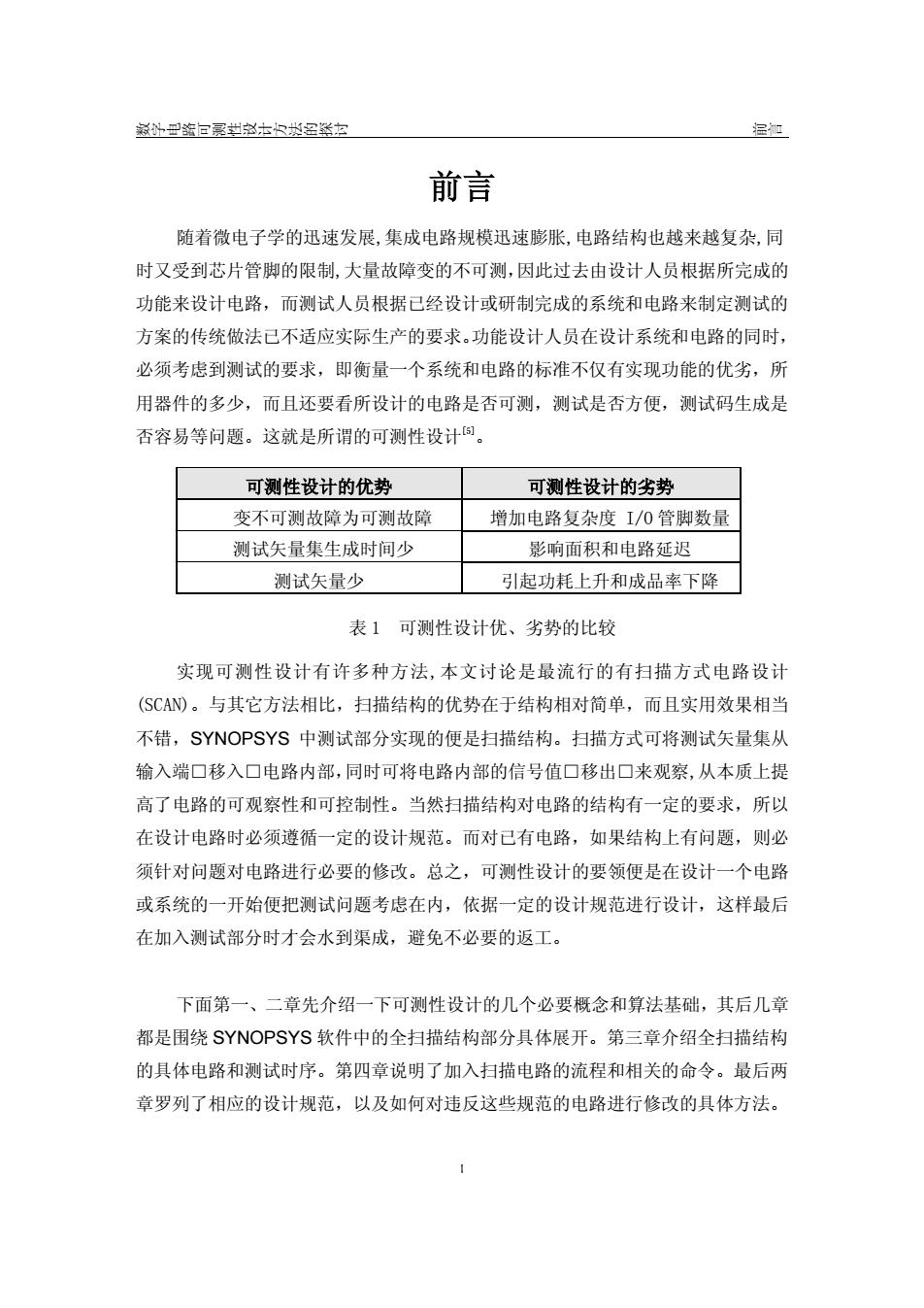

藏州巴资恒录出赵古只兴超张女 福加 前言 随着微电子学的迅速发展,集成电路规模迅速膨胀,电路结构也越来越复杂,同 时又受到芯片管脚的限制,大量故障变的不可测,因此过去由设计人员根据所完成的 功能来设计电路,而测试人员根据已经设计或研制完成的系统和电路来制定测试的 方案的传统做法已不适应实际生产的要求。功能设计人员在设计系统和电路的同时, 必须考虑到测试的要求,即衡量一个系统和电路的标准不仅有实现功能的优劣,所 用器件的多少,而且还要看所设计的电路是否可测,测试是否方便,测试码生成是 否容易等问题。这就是所谓的可测性设计。 可测性设计的优势 可测性设计的劣势 变不可测故障为可测故障 增加电路复杂度I/0管脚数量 测试矢量集生成时间少 影响面积和电路延迟 测试矢量少 引起功耗上升和成品率下降 表1可测性设计优、劣势的比较 实现可测性设计有许多种方法,本文讨论是最流行的有扫描方式电路设计 (SCAN)。与其它方法相比,扫描结构的优势在于结构相对简单,而且实用效果相当 不错,SYNOPSYS中测试部分实现的便是扫描结构。扫描方式可将测试矢量集从 输入端口移入口电路内部,同时可将电路内部的信号值口移出口来观察,从本质上提 高了电路的可观察性和可控制性。当然扫描结构对电路的结构有一定的要求,所以 在设计电路时必须遵循一定的设计规范。而对已有电路,如果结构上有问题,则必 须针对问题对电路进行必要的修改。总之,可测性设计的要领便是在设计一个电路 或系统的一开始便把测试问题考虑在内,依据一定的设计规范进行设计,这样最后 在加入测试部分时才会水到渠成,避免不必要的返工。 下面第一、二章先介绍一下可测性设计的几个必要概念和算法基础,其后几章 都是围绕SYNOPSYS软件中的全扫描结构部分具体展开。第三章介绍全扫描结构 的具体电路和测试时序。第四章说明了加入扫描电路的流程和相关的命令。最后两 章罗列了相应的设计规范,以及如何对违反这些规范的电路进行修改的具体方法

数 字 电 路 可 测 性 设 计 方 法 的 探 讨 前 言 I 前言 随着微电子学的迅速发展,集成电路规模迅速膨胀,电路结构也越来越复杂,同 时又受到芯片管脚的限制,大量故障变的不可测,因此过去由设计人员根据所完成的 功能来设计电路,而测试人员根据已经设计或研制完成的系统和电路来制定测试的 方案的传统做法已不适应实际生产的要求。功能设计人员在设计系统和电路的同时, 必须考虑到测试的要求,即衡量一个系统和电路的标准不仅有实现功能的优劣,所 用器件的多少,而且还要看所设计的电路是否可测,测试是否方便,测试码生成是 否容易等问题。这就是所谓的可测性设计[5]。 可测性设计的优势 可测性设计的劣势 变不可测故障为可测故障 增加电路复杂度 I/O 管脚数量 测试矢量集生成时间少 影响面积和电路延迟 测试矢量少 引起功耗上升和成品率下降 表 1 可测性设计优、劣势的比较 实现可测性设计有许多种方法,本文讨论是最流行的有扫描方式电路设计 (SCAN)。与其它方法相比,扫描结构的优势在于结构相对简单,而且实用效果相当 不错,SYNOPSYS 中测试部分实现的便是扫描结构。扫描方式可将测试矢量集从 输入端□移入□电路内部,同时可将电路内部的信号值□移出□来观察,从本质上提 高了电路的可观察性和可控制性。当然扫描结构对电路的结构有一定的要求,所以 在设计电路时必须遵循一定的设计规范。而对已有电路,如果结构上有问题,则必 须针对问题对电路进行必要的修改。总之,可测性设计的要领便是在设计一个电路 或系统的一开始便把测试问题考虑在内,依据一定的设计规范进行设计,这样最后 在加入测试部分时才会水到渠成,避免不必要的返工。 下面第一、二章先介绍一下可测性设计的几个必要概念和算法基础,其后几章 都是围绕 SYNOPSYS 软件中的全扫描结构部分具体展开。第三章介绍全扫描结构 的具体电路和测试时序。第四章说明了加入扫描电路的流程和相关的命令。最后两 章罗列了相应的设计规范,以及如何对违反这些规范的电路进行修改的具体方法