引言 第一章引言 今天,电子产品在人们的生活中扮演着举足轻重的角色。电视机、电脑、网络、无 线通信设备等电子工具,给人们带来了丰富多彩的娱乐享受,而采用电子系统控制的新 一代家电,如冰箱、空调、电饭锅、汽车等使我们的生活更加便利。这些现代电子设备 多采用数字电路的方式来实现,但我们生活的自然界却是模拟的,对于我们一自然界 中的人类来说,感知外界的方式也是模拟的。因此,这些电子系统需要把外部的模拟信 号采集进来,并把它转换成数字信号,然后通过DSP或CPU等数字信号处理器,对其进 行处理,最终得到的结果往往需要再变回到模拟形式,以便控制各种机电设备,或作为 各种家电设备的输出,来满足人们视听的享受。这种把模拟数据采集进来并转换成数字 数据,或把数字数据转换成模拟数据的功能是通过模数和数模转换器实现的。模数和数 模转换器作为数字信号和模拟信号的接口如图1.1所示。 1.1研究的背景、方向和意义 目前,可内嵌的高速、高精度、低功耗数据转换器成为模拟集成电路领域中的研究 热点。其原因是,1、与模拟信号相比,数字信号具有便于存储、转移、保真度和可靠 性高等优点,因此,在过去的20年,各国的研究机构对数字技术的发展非常重视,另外, 随着CMOS工艺水平的长足进步和数字系统设计软件的日趋成熟,使数字系统无论是在 处理能力还是处理速度上都取得了飞速的发展。相对而言,模拟和数模接口电路的设计 在过去的几十年没有得到足够的重视,加之模拟设计软件也不够成熟,使模拟尤其是数 模接口电路的发展落后于数字电路的发展,因此,在一些包括数模接口的电子系统,象 数字视频系统和数字通信系统中,接口电路的性能(如速度、精度)成为限制整个系统 性能的瓶颈:2、由于靠电池供电的便携式设备日益普及,也要求在达到高速、高精度 的前提下,消耗尽可能小的功耗,以维持较长的待机时间:3、随着单片系统集成的快 速发展,要求接口电路和数字系统集成在一块芯片上,这对降低成本、提高性能具有很 ADC Digital DAC 图1.1 模数和数模转换器作为数字和模拟信号的接口 高速数模转换器的设计 1

引言 高速数模转换器的设计 1 第一章 引言 今天,电子产品在人们的生活中扮演着举足轻重的角色。电视机、电脑、网络、无 线通信设备等电子工具,给人们带来了丰富多彩的娱乐享受,而采用电子系统控制的新 一代家电,如冰箱、空调、电饭锅、汽车等使我们的生活更加便利。这些现代电子设备 多采用数字电路的方式来实现,但我们生活的自然界却是模拟的,对于我们——自然界 中的人类来说,感知外界的方式也是模拟的。因此,这些电子系统需要把外部的模拟信 号采集进来,并把它转换成数字信号,然后通过DSP或CPU等数字信号处理器,对其进 行处理,最终得到的结果往往需要再变回到模拟形式,以便控制各种机电设备,或作为 各种家电设备的输出,来满足人们视听的享受。这种把模拟数据采集进来并转换成数字 数据,或把数字数据转换成模拟数据的功能是通过模数和数模转换器实现的。模数和数 模转换器作为数字信号和模拟信号的接口如图1.1所示。 1.1 研究的背景、方向和意义 目前,可内嵌的高速、高精度、低功耗数据转换器成为模拟集成电路领域中的研究 热点。其原因是,1、与模拟信号相比,数字信号具有便于存储、转移、保真度和可靠 性高等优点,因此,在过去的20年,各国的研究机构对数字技术的发展非常重视,另外, 随着CMOS工艺水平的长足进步和数字系统设计软件的日趋成熟,使数字系统无论是在 处理能力还是处理速度上都取得了飞速的发展。相对而言,模拟和数模接口电路的设计 在过去的几十年没有得到足够的重视,加之模拟设计软件也不够成熟,使模拟尤其是数 模接口电路的发展落后于数字电路的发展,因此,在一些包括数模接口的电子系统,象 数字视频系统和数字通信系统中,接口电路的性能(如速度、精度)成为限制整个系统 性能的瓶颈;2、由于靠电池供电的便携式设备日益普及,也要求在达到高速、高精度 的前提下,消耗尽可能小的功耗,以维持较长的待机时间;3、随着单片系统集成的快 速发展,要求接口电路和数字系统集成在一块芯片上,这对降低成本、提高性能具有很 图1.1 模数和数模转换器作为数字和模拟信号的接口

引言 重要的意义[2]。 从上面的介绍可以看到,目前发达国家对高速数据转换电路的研究开发已经达到了 很高的水平,由于各种原因,我国在这方面的研发水平与国外相比还十分落后,这严重 限制了我国在集成电路设计尤其是系统集成方面的发展。为了缩短与国外先进水平之间 的差距,我们急需加强在这个领域的研究。本文以高速、高精度数模转换器的设计为研 究方向,学习了高速数据转换电路的设计理论和设计方法,希望这些学习经验对自己以 后的研究生活能够有一定的帮助。 1.2主要工作 在本文工作期间,作者查阅了大量有关数据转换方面的资料,较系统地研究了各种 数据转换器的结构和性能,并在唐长文老师的指导下,设计了一个10位,100兆采样速 率的数模转换器。 为了使电路达到最优的性能,作者在设计仿真期间,又查阅了许多相关的资料,并 与指导老师进行了一些讨论。 数模转换器的性能对版图的依赖性比较强,对于本文设计的10位,100兆采样速 率的数模转换器的版图设计,作者参考了文献[1]和[5],具体的版图设计目前正在紧张 的进行中。 1.3论文的组织结构 本文主要介绍数模转换器的设计。论文的结构安排大致如下: 第二章简单介数模转换器的工作原理、一些基本概念和几种常用的拓扑结构: 第三章主要介绍本文设计所采用的结构和具体的实现方法: 第四章详细叙述10位,100兆采样速率电流型数模转换器的设计和仿真过程; 第五章主要是根据仿真结果进行分析和讨论: 第六章主要介绍芯片的版图设计。 高速数模转换器的设计 2

引言 高速数模转换器的设计 2 重要的意义[2]。 从上面的介绍可以看到,目前发达国家对高速数据转换电路的研究开发已经达到了 很高的水平,由于各种原因,我国在这方面的研发水平与国外相比还十分落后,这严重 限制了我国在集成电路设计尤其是系统集成方面的发展。为了缩短与国外先进水平之间 的差距,我们急需加强在这个领域的研究。本文以高速、高精度数模转换器的设计为研 究方向,学习了高速数据转换电路的设计理论和设计方法,希望这些学习经验对自己以 后的研究生活能够有一定的帮助。 1.2 主要工作 在本文工作期间,作者查阅了大量有关数据转换方面的资料,较系统地研究了各种 数据转换器的结构和性能,并在唐长文老师的指导下,设计了一个10位,100兆采样速 率的数模转换器。 为了使电路达到最优的性能,作者在设计仿真期间,又查阅了许多相关的资料,并 与指导老师进行了一些讨论。 数模转换器的性能对版图的依赖性比较强,对于本文设计的 10 位,100 兆采样速 率的数模转换器的版图设计,作者参考了文献[1]和[5],具体的版图设计目前正在紧张 的进行中。 1.3 论文的组织结构 本文主要介绍数模转换器的设计。论文的结构安排大致如下: 第二章简单介绍数模转换器的工作原理、一些基本概念和几种常用的拓扑结构; 第三章主要介绍本文设计所采用的结构和具体的实现方法; 第四章详细叙述10位,100兆采样速率电流型数模转换器的设计和仿真过程; 第五章主要是根据仿真结果进行分析和讨论; 第六章主要介绍芯片的版图设计

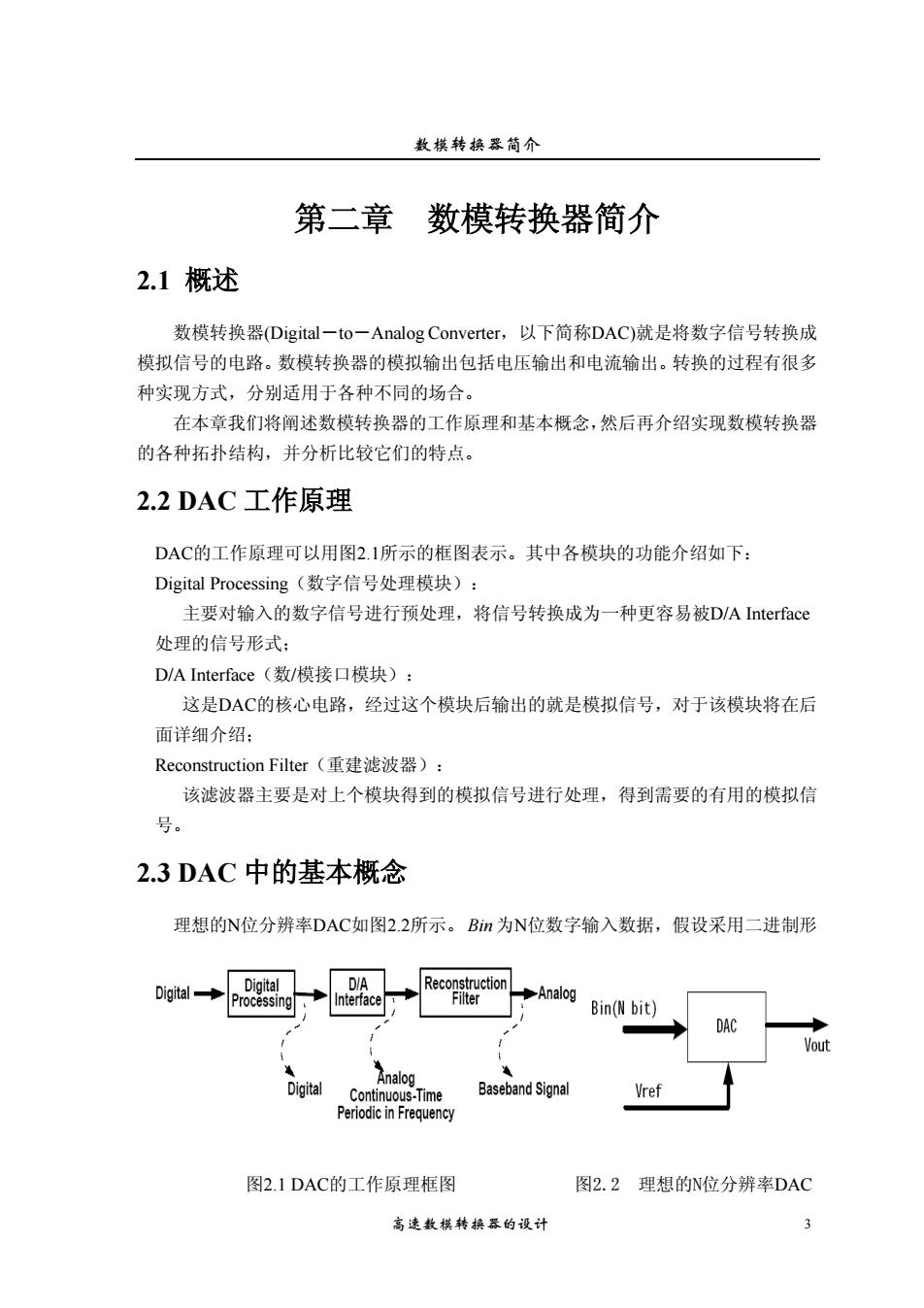

数模转换器简介 第二章 数模转换器简介 2.1概述 数模转换器(Digital一to一Analog Converter, 以下简称DAC)就是将数字信号转换成 模拟信号的电路。数模转换器的模拟输出包括电压输出和电流输出。转换的过程有很多 种实现方式,分别适用于各种不同的场合。 在本章我们将阐述数模转换器的工作原理和基本概念,然后再介绍实现数模转换器 的各种拓扑结构,并分析比较它们的特点。 2.2DAC工作原理 DAC的工作原理可以用图2.1所示的框图表示。其中各模块的功能介绍如下: Digital Processing(数字信号处理模块): 主要对输入的数字信号进行预处理,将信号转换成为一种更容易被D/A Interface 处理的信号形式: D/A Interface(数/模接口模块): 这是DAC的核心电路,经过这个模块后输出的就是模拟信号,对于该模块将在后 面详细介绍: Reconstruction Filter(重建滤波器): 该滤波器主要是对上个模块得到的模拟信号进行处理,得到需要的有用的模拟信 号。 2.3DAC中的基本概念 理想的N位分辨率DAC如图2.2所示。Bim为N位数字输入数据,假设采用二进制形 Digital DIA Reconstruction Digital- Processing Interface Filter Analog Bin(N bit) DAC Vout Digital Analog Continuous-Time Baseband Signal Vref Periodic in Frequency 图2.1DAC的工作原理框图 图2.2理想的N位分辨率DAC 高速数模转换器的设计 3

数模转换器简介 高速数模转换器的设计 3 第二章 数模转换器简介 2.1 概述 数模转换器(Digital-to-Analog Converter,以下简称DAC)就是将数字信号转换成 模拟信号的电路。数模转换器的模拟输出包括电压输出和电流输出。转换的过程有很多 种实现方式,分别适用于各种不同的场合。 在本章我们将阐述数模转换器的工作原理和基本概念,然后再介绍实现数模转换器 的各种拓扑结构,并分析比较它们的特点。 2.2 DAC 工作原理 DAC的工作原理可以用图2.1所示的框图表示。其中各模块的功能介绍如下: Digital Processing(数字信号处理模块): 主要对输入的数字信号进行预处理,将信号转换成为一种更容易被D/A Interface 处理的信号形式; D/A Interface(数/模接口模块): 这是DAC的核心电路,经过这个模块后输出的就是模拟信号,对于该模块将在后 面详细介绍; Reconstruction Filter(重建滤波器): 该滤波器主要是对上个模块得到的模拟信号进行处理,得到需要的有用的模拟信 号。 2.3 DAC 中的基本概念 理想的N位分辨率DAC如图2.2所示。 Bin 为N位数字输入数据,假设采用二进制形 图2.1 DAC的工作原理框图 图2.2 理想的N位分辨率DAC

数模转换器简介 式,即: Bin=b2°+b2'+…+bw-2 b,(=0,L,…N-1)为1或者0。我们定义bN为最高位MSB),定义b,为最低位(LSB)。对 于一个给定的数字Bn,模拟电平输出为: Vot=ref-(b2°+h2'+…+bw-12-)=ref-Bin 下面简要介绍DAC中通用的术语。 分辨率DAC中的分辨率定义为在不同的输入数字码值下所有可能输出的模拟电平的 个数,N位分辨率意味着DAC能产生2-1个不同的模拟电平,一般情况下它就指输入 数字码的位数。 失调和增益误差失调定义为当输入0码值时实际输出的模拟信号的值,增益误差定 义为当扣除失调后理想的满量程输出的值和实际输出的值的差,如图2.3所示。 精度DAC中的精度分为绝对精度和相对精度。绝对精度定义为理想输出和实际输出之 间的差,包括各种失调和非线性误差在内。相对精度定义为最大积分非线性误差(下面 将讲述这个概念)。精度表示为满量程的比例,用有效位数来表示。例如8-bt精度表示 DAC的误差小于DAC输出满量程的1/28.注意精度这个概念和分辨率不相关。一个12-bit 分辨率的DAC可能精度只有10-bit:而一个10-bit分辨率的DAC可能有12-bit的精度。精 度大于分辨率意味着DAC的传输响应能够被比较精确地控制。 积分线性误差(NL一Integral Nonlinearity)当除去失调和增益误差后,积分线 性误差就定义为实际输出传输特性曲线对理想传输特性曲线(一条直线)的偏离。如图2.4 所示。 微分线性误差DNL一Differential Nonlinearity)在理想的DACc中,每次模拟输 出变化最小为1LSB,微分线性误差定义为每次模拟输出变化最小时对1LSB的偏离(将增 益误差和失调除外)。我们定义的DL是对每个数字输入码值而言的,有时也有用最大 的DNL来定义整个DAC的DNL。理想的DAC对于每个数字输入其微分线性误差均为O, 而一个具有最大DNL为0.5LSB的DAC的每次最小变化输出在0.5LSB到1.5LSB之间。如 图2.4所示。 Ideal DAC Response ideal ndino INL=2 LSB Gain error DNL =-1 LSB Bin 十十一 Offset error Digital Code 图2.3DAC的失调和增益误差 图2.4DAC的积分和微分线性误差 高速数模转换器的设计

数模转换器简介 高速数模转换器的设计 4 式,即: 01 1 01 1 22 2N Bin b b bN − = + ++ " − ( 0,1, 1) i bi N = − " 为1或者0。我们定义 N 1 b − 为最高位(MSB),定义 0 b 为最低位(LSB)。对 于一个给定的数字 Bin ,模拟电平输出为: 01 1 01 1 (2 2 2 ) N Vout Vref b b b Vref Bin N − = + ++ = − i" i 下面简要介绍DAC中通用的术语。 分辨率 DAC中的分辨率定义为在不同的输入数字码值下所有可能输出的模拟电平的 个数,N位分辨率意味着DAC能产生2 1 N − 个不同的模拟电平,一般情况下它就指输入 数字码的位数。 失调和增益误差 失调定义为当输入0码值时实际输出的模拟信号的值,增益误差定 义为当扣除失调后理想的满量程输出的值和实际输出的值的差,如图2.3所示。 精度 DAC中的精度分为绝对精度和相对精度。绝对精度定义为理想输出和实际输出之 间的差,包括各种失调和非线性误差在内。相对精度定义为最大积分非线性误差(下面 将讲述这个概念)。精度表示为满量程的比例,用有效位数来表示。例如8-bit 精度表示 DAC的误差小于DAC输出满量程的 8 1 2 。注意精度这个概念和分辨率不相关。一个12-bit 分辨率的DAC可能精度只有10-bit;而一个10-bit分辨率的DAC可能有12-bit的精度。精 度大于分辨率意味着DAC的传输响应能够被比较精确地控制。 积分线性误差(INL-Integral Nonlinearity) 当除去失调和增益误差后,积分线 性误差就定义为实际输出传输特性曲线对理想传输特性曲线(一条直线)的偏离。如图2.4 所示。 微分线性误差(DNL-Differential Nonlinearity) 在理想的DAC中,每次模拟输 出变化最小为1LSB,微分线性误差定义为每次模拟输出变化最小时对1LSB的偏离(将增 益误差和失调除外)。我们定义的DNL是对每个数字输入码值而言的,有时也有用最大 的DNL来定义整个DAC的DNL。理想的DAC对于每个数字输入其微分线性误差均为0, 而一个具有最大DNL为0.5LSB的DAC的每次最小变化输出在0.5LSB到1.5LSB之间。如 图2.4所示。 图2.3 DAC的失调和增益误差 图2.4 DAC的积分和微分线性误差

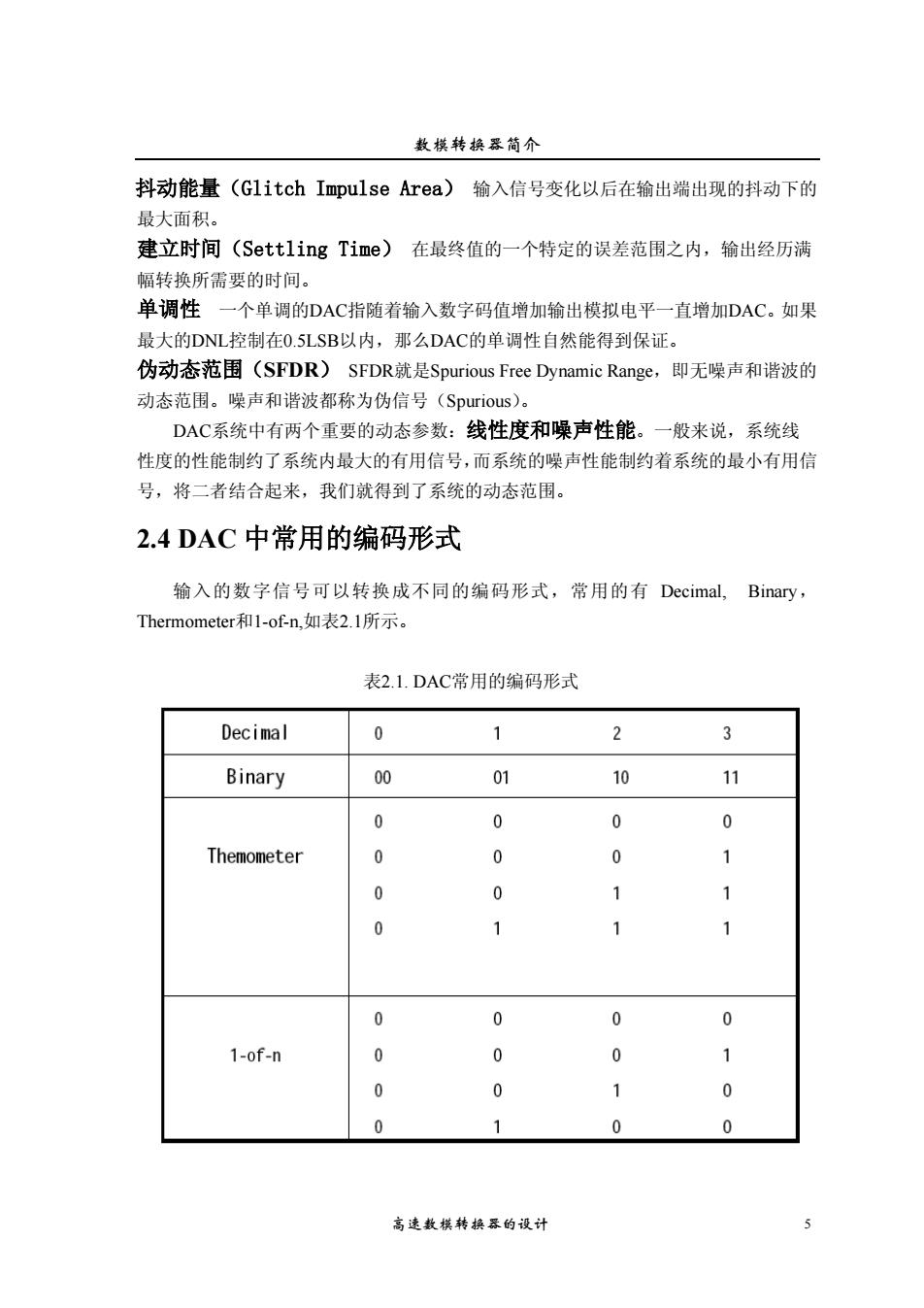

数模转换器简介 抖动能量(G1 itch Impulse Area)输入信号变化以后在输出端出现的抖动下的 最大面积。 建立时间(Settling Time)在最终值的一个特定的误差范围之内,输出经历满 幅转换所需要的时间。 单调性一个单调的DAC指随着输入数字码值增加输出模拟电平一直增加DAC。如果 最大的DNL控制在O.5LSB以内,那么DAC的单调性自然能得到保证。 伪动态范围(SFDR)SFDR就是Spurious Free Dynamic Range,即无噪声和谐波的 动态范围。噪声和谐波都称为伪信号(Spurious)。 DAC系统中有两个重要的动态参数:线性度和噪声性能。一般来说,系统线 性度的性能制约了系统内最大的有用信号,而系统的噪声性能制约着系统的最小有用信 号,将二者结合起来,我们就得到了系统的动态范围。 2.4DAC中常用的编码形式 输入的数字信号可以转换成不同的编码形式,常用的有Decimal,Binary, Thermometer和1-of-n,如表2.1所示。 表2.1.DAC常用的编码形式 Decimal 0 1 2 3 Binary 00 01 10 11 0 0 0 0 Themometer 0 0 0 1 0 0 1 1 0 1 1 1 0 0 0 0 1-of-n 0 0 0 1 0 0 1 0 0 1 0 0 高速戴模转换器的设计 5

数模转换器简介 高速数模转换器的设计 5 抖动能量(Glitch Impulse Area) 输入信号变化以后在输出端出现的抖动下的 最大面积。 建立时间(Settling Time) 在最终值的一个特定的误差范围之内,输出经历满 幅转换所需要的时间。 单调性 一个单调的DAC指随着输入数字码值增加输出模拟电平一直增加DAC。如果 最大的DNL控制在0.5LSB以内,那么DAC的单调性自然能得到保证。 伪动态范围(SFDR) SFDR就是Spurious Free Dynamic Range,即无噪声和谐波的 动态范围。噪声和谐波都称为伪信号(Spurious)。 DAC系统中有两个重要的动态参数:线性度和噪声性能。一般来说,系统线 性度的性能制约了系统内最大的有用信号,而系统的噪声性能制约着系统的最小有用信 号,将二者结合起来,我们就得到了系统的动态范围。 2.4 DAC 中常用的编码形式 输入的数字信号可以转换成不同的编码形式,常用的有 Decimal, Binary, Thermometer和1-of-n,如表2.1所示。 表2.1. DAC常用的编码形式