。尽管缓冲器能够改善互连时延, 但其本身具有一定的延迟 (Tr=RC),过多的插入缓冲器可能反而会导致互连延时 的增加。因此必须对插入缓冲器数目进行合理优化。 对于插入个缓冲器的互连线,其时延可以表述如下 ,=0.69(C,+5+069(C,)+038rc(月9 设∂t,/am=0和ot。/os=0 求得n,s和tp,min: 0.38rcL2 S= 0.69RCa rCa =2.4LRCarc

• 尽管缓冲器能够改善互连时延,但其本身具有一定的延迟 (Tbuff = RC),过多的插入缓冲器可能反而会导致互连延时 的增加。因此必须对插入缓冲器数目进行合理优化。 对于插入n个缓冲器的互连线,其时延可以表述如下 设 和 ,求得 n , s 和tp,min:

表明插入缓冲器能够使一条导线的延时与长度的关系改变 为线性。互连线越长,插入优化效果越明显。对于一个给 定的工艺和给定的互连层,存在缓冲器之间导线段的最优 长度。这一临界长度由下列表达式给出 .69R 0.38rc 插入缓冲器来减少导线延时只有在导线长度至少为临界长 度的两倍时才有意义。 在65 nm CMOS工艺下,推导出一条长10cm,宽1um的 Cu-1全局互连线的传播延时为9.45ns。利用上面提到的 插入缓冲器技术,将该导线分成26段可使它的延时最小 其结果是总延时为1.76ns,大大改善了互连性能。 2互连线宽优化技术

• 在 65nm CMOS 工艺下,推导出一条长 10cm,宽 1um 的 Cu-1 全局互连线的传播延时为 9.45ns。利用上面提到的 插入缓冲器技术,将该导线分成 26 段可使它的延时最小 ,其结果是总延时为 1.76ns,大大改善了互连性能。 表明插入缓冲器能够使一条导线的延时与长度的关系改变 为线性。互连线越长,插入优化效果越明显。对于一个给 定的工艺和给定的互连层,存在缓冲器之间导线段的最优 长度。这一临界长度由下列表达式给出 插入缓冲器来减少导线延时只有在导线长度至少为临界长 度的两倍时才有意义。 2 互连线宽优化技术

十、衬底串扰噪声 随着集成电路设计进入深亚微米,芯片的集成度 显著提高,金属线的布线层数、布线密度急剧升 高,使信号线之间的寄生关系错综复杂。金属布 线层数与密度的变化使串扰噪声对芯片的影响也 越来越大。 在深亚微米工艺设计中,特别是在0.13微米及以 下尺寸的工艺设计中,串扰是影响芯片性能的主 要问题之一。芯片上的连线之间会产生寄生耦合 芯片加工中采用的材料、连线的尺寸、连线的间 距等因素都会对芯片的最终性能产生极大的影响

• 十、衬底串扰噪声 • 随着集成电路设计进入深亚微米,芯片的集成度 显著提高,金属线的布线层数、布线密度急剧升 高,使信号线之间的寄生关系错综复杂。金属布 线层数与密度的变化使串扰噪声对芯片的影响也 越来越大。 • 在深亚微米工艺设计中,特别是在0.13微米及以 下尺寸的工艺设计中,串扰是影响芯片性能的主 要问题之一。芯片上的连线之间会产生寄生耦合。 芯片加工中采用的材料、连线的尺寸、连线的间 距等因素都会对芯片的最终性能产生极大的影响

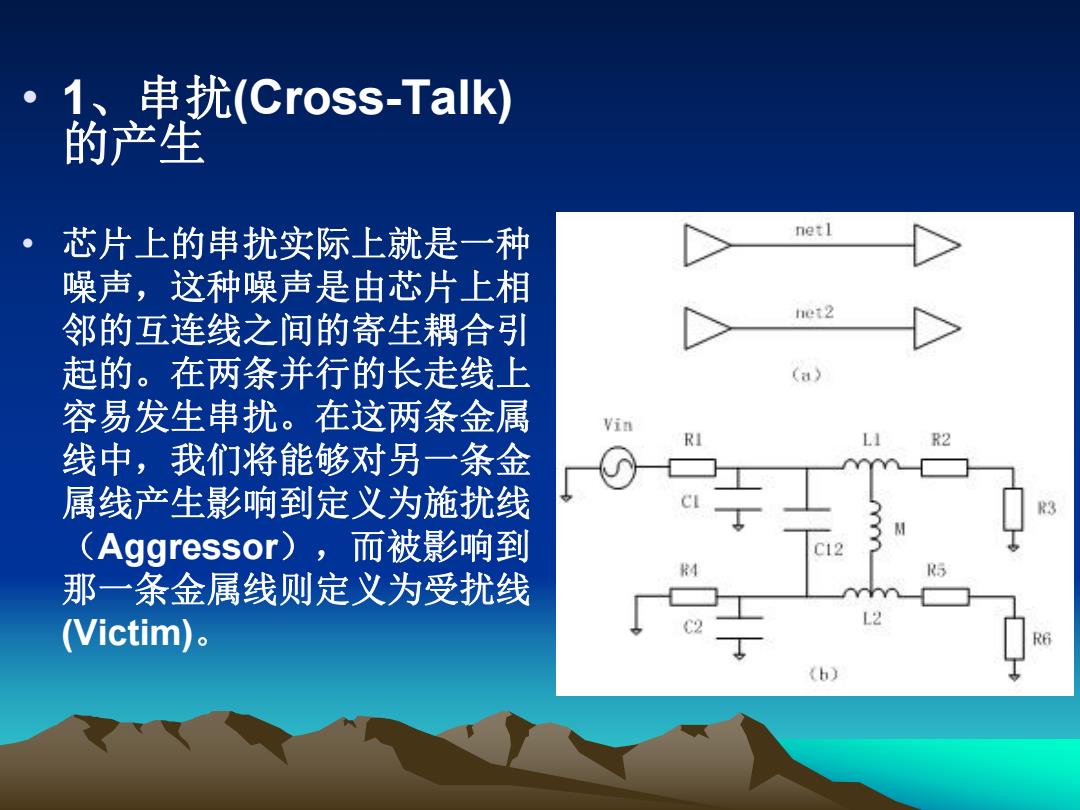

1、串扰(Cross-Talk) 的产生 芯片上的串扰实际上就是一种 netl 噪声,这种噪声是由芯片上相 het2 邻的互连线之间的寄生耦合引 起的。在两条并行的长走线上 (a 容易发生串扰。在这两条金属 Vin R2 线中,我们将能够对另一条金 属线产生影响到定义为施扰线 (Aggressor),而被影响到 那一条金属线则定义为受扰线 (Victim) (b)

• 1、串扰(Cross-Talk) 的产生 • 芯片上的串扰实际上就是一种 噪声,这种噪声是由芯片上相 邻的互连线之间的寄生耦合引 起的。在两条并行的长走线上 容易发生串扰。在这两条金属 线中,我们将能够对另一条金 属线产生影响到定义为施扰线 (Aggressor),而被影响到 那一条金属线则定义为受扰线 (Victim)

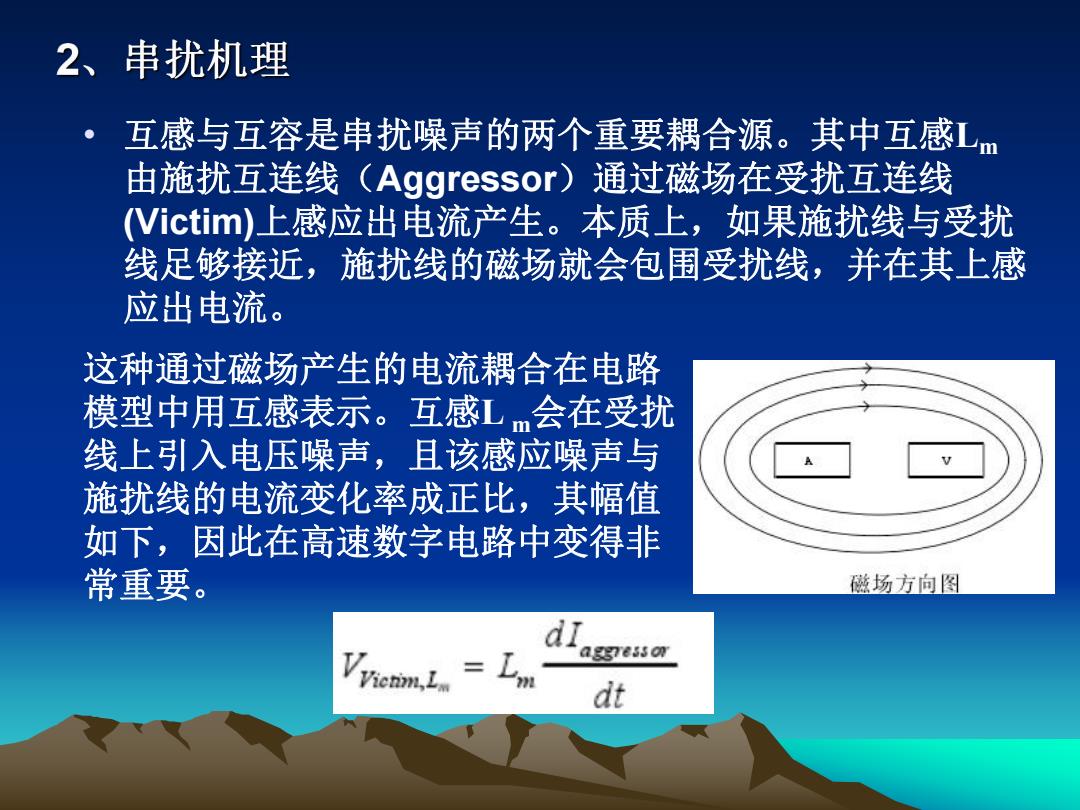

2、串扰机理 互感与互容是串扰噪声的两个重要耦合源。其中互感Lm 由施扰互连线(Aggressor)通过磁场在受扰互连线 (Victim)上感应出电流产生。本质上,如果施扰线与受扰 线足够接近,施扰线的磁场就会包围受扰线,并在其上感 应出电流。 这种通过磁场产生的电流耦合在电路 模型中用互感表示。互感Lm会在受扰 线上引入电压噪声,且该感应噪声与 施扰线的电流变化率成正比,其幅值 如下,因此在高速数字电路中变得非 常重要。 磁场方向图 =Lm dt

• 互感与互容是串扰噪声的两个重要耦合源。其中互感Lm 由施扰互连线(Aggressor)通过磁场在受扰互连线 (Victim)上感应出电流产生。本质上,如果施扰线与受扰 线足够接近,施扰线的磁场就会包围受扰线,并在其上感 应出电流。 这种通过磁场产生的电流耦合在电路 模型中用互感表示。互感L m会在受扰 线上引入电压噪声,且该感应噪声与 施扰线的电流变化率成正比,其幅值 如下,因此在高速数字电路中变得非 常重要