八、天线效应 1、天线效应(Process Antenna Effect,PAE), 又称之为“等离子导致栅氧损伤(plasma induced gate oxide damage,PID) 在离子刻蚀等工艺加工过程中,芯片表面会有很多暴露 的导体(如金属线或多晶硅)等会收集附近的游离电荷, 导致其电位升高。如果有MOS管的栅端与这片导线相 连,栅端上的薄氧化层就有可能被导体上积聚的高电压 击穿,使电路失效。 由于导体收集游离电荷的行为类似于现实中天线收集信 号的行为,因此这种现象也被称为“天线效应” 随着工艺技术的发展,栅的尺寸越来越小,金属的层数 越来越多,发生天线效应的可能性就越大

• 1、天线效应(Process Antenna Effect,PAE), 又称之为“等离子导致栅氧损伤(plasma induced gate oxide damage,PID)” 。 • 在离子刻蚀等工艺加工过程中,芯片表面会有很多暴露 的导体(如金属线或多晶硅)等会收集附近的游离电荷, 导致其电位升高。如果有MOS管的栅端与这片导线相 连,栅端上的薄氧化层就有可能被导体上积聚的高电压 击穿,使电路失效。 • 由于导体收集游离电荷的行为类似于现实中天线收集信 号的行为,因此这种现象也被称为“天线效应” 。 • 随着工艺技术的发展,栅的尺寸越来越小,金属的层数 越来越多,发生天线效应的可能性就越大

在还未形成metal22的时候,AB段metal1上积累 的电荷由器件1中的NMOS管的栅极和地之间通路 泄放到地,会对NMOS管的栅氧化层造成损害; 而器件2的NMOS管的有源区和地之间形成泄放通 路,CD段metal1上积累的电荷泄放不会对栅氧化 层造成损害。 工艺上完成 VDD 扩散区 电荷 相区 VDD metal2以后, 两个器件中所 有MOS管的 栅氧化层都不 会受到损害。 器件2 器件1 D 器 Metall Metal2 V1A12

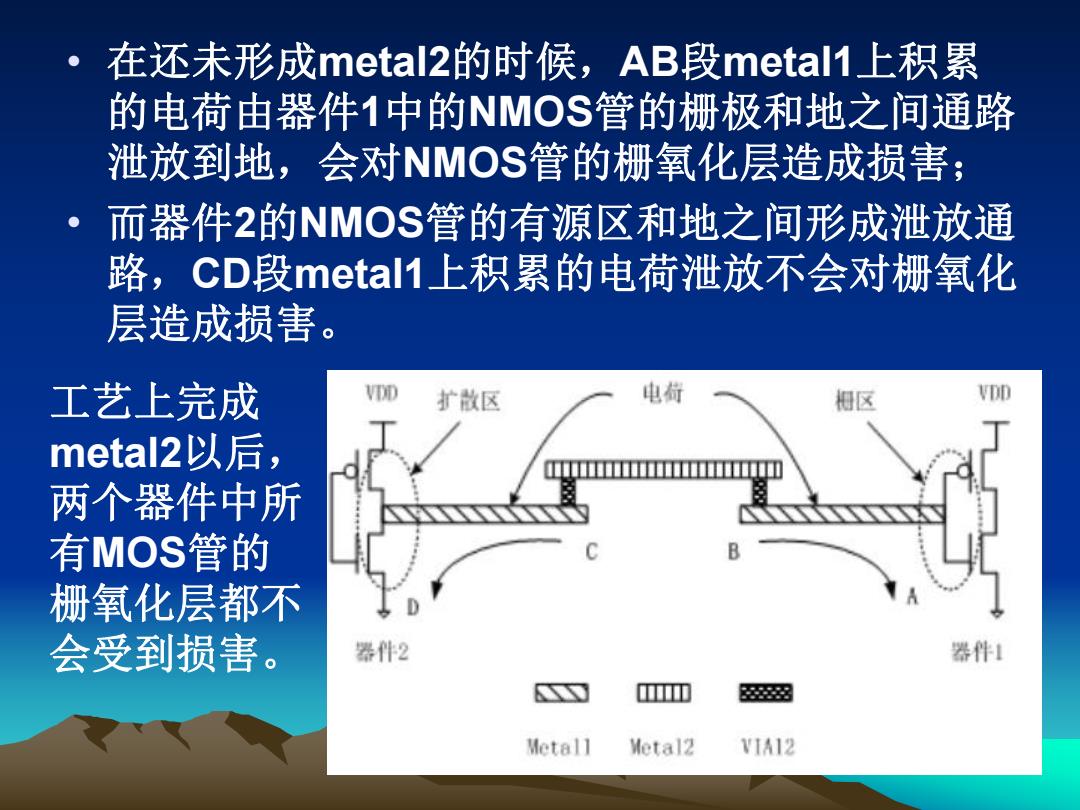

• 在还未形成metal2的时候,AB段metal1上积累 的电荷由器件1中的NMOS管的栅极和地之间通路 泄放到地,会对NMOS管的栅氧化层造成损害; • 而器件2的NMOS管的有源区和地之间形成泄放通 路,CD段metal1上积累的电荷泄放不会对栅氧化 层造成损害。 工艺上完成 metal2以后, 两个器件中所 有MOS管的 栅氧化层都不 会受到损害

2、天线效应的消除 对天线效应产生机理的分析,可以得到能够有效 消除天线效应的方法:减少暴露的导体面积;在 发生天线效应的走线上添加其它的电荷泄放回路。 一般在集成电路的版图设计中,消除天线效应的 方法有下面三种: A、增大器件栅极面积,增强栅极对泄放电流的 承受能力,减小天线效应的影响。缺点是影响器 件性能和增大芯片面积

• 2、天线效应的消除 • 对天线效应产生机理的分析,可以得到能够有效 消除天线效应的方法:减少暴露的导体面积;在 发生天线效应的走线上添加其它的电荷泄放回路。 • 一般在集成电路的版图设计中,消除天线效应的 方法有下面三种: A、增大器件栅极面积,增强栅极对泄放电流的 承受能力,减小天线效应的影响。缺点是影响器 件性能和增大芯片面积

B、跳线法 跳线法就是将存在天线效应的金属层断开,通 过通孔连接到其它的金属层,最后再回到之前 的金属层。这种方法还可以分为向上跳线法和 向下跳线法,如图(c)和(d)所示,其中, 向上跳线法更为常用。 存在天线效应 a c向上跳线 添加反偏二极管 b d向下跳线

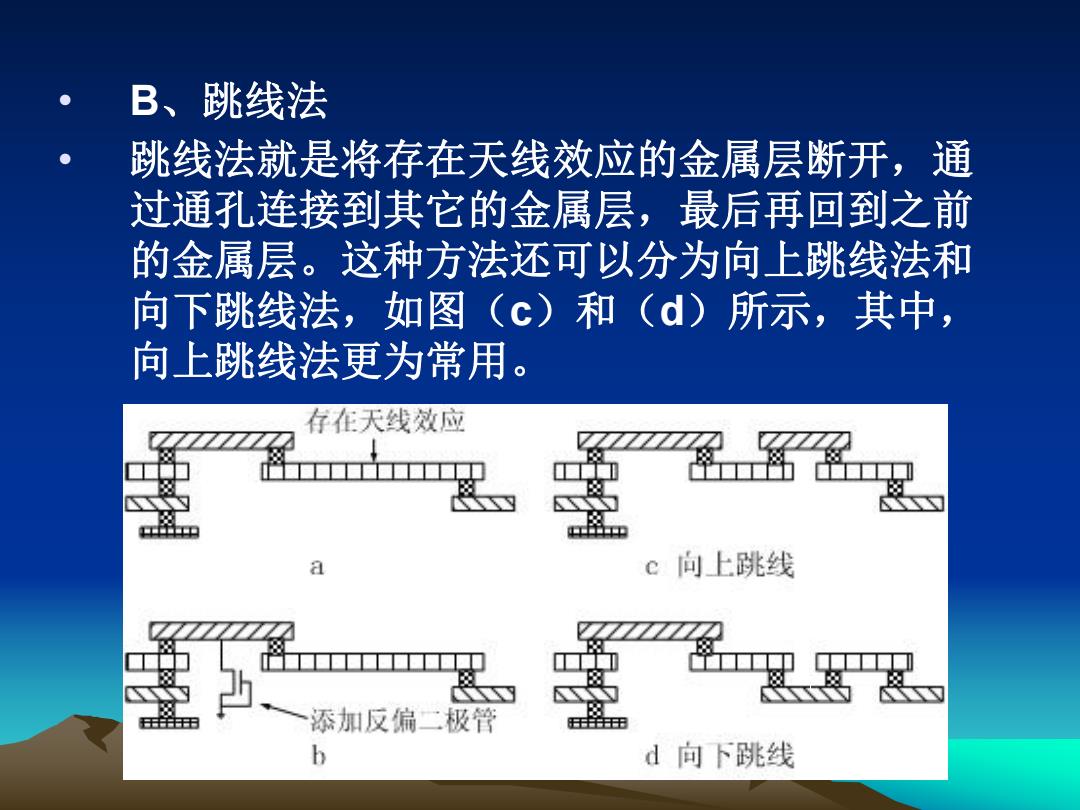

• B、跳线法 • 跳线法就是将存在天线效应的金属层断开,通 过通孔连接到其它的金属层,最后再回到之前 的金属层。这种方法还可以分为向上跳线法和 向下跳线法,如图(c)和(d)所示,其中, 向上跳线法更为常用

跳线法对消除天线效应十分有效。缺点是这种方 法为了采用不同的金属层,在芯片上增加了通孔, 由于通孔电阻的存在,该通路上的电阻也大大增 加,有可能会对芯片的性能造成直接的影响 3、添加泄放回路 具有天线效应的通路都会直接和MOS管的栅极相 连。如果在靠近这个MOS管栅极的位置添加一个 连接该通路和地的反偏二极管,就可以在二极管 处形成一个电荷泄放回路,从而使MOS管的栅免 受通路上积累的电荷损害,这就是添加泄放回路 以消除天线效应的原理。如图(b)所示

• 跳线法对消除天线效应十分有效。缺点是这种方 法为了采用不同的金属层,在芯片上增加了通孔, 由于通孔电阻的存在,该通路上的电阻也大大增 加,有可能会对芯片的性能造成直接的影响。 • 3、添加泄放回路 • 具有天线效应的通路都会直接和MOS管的栅极相 连。如果在靠近这个MOS管栅极的位置添加一个 连接该通路和地的反偏二极管,就可以在二极管 处形成一个电荷泄放回路,从而使MOS管的栅免 受通路上积累的电荷损害,这就是添加泄放回路 以消除天线效应的原理。如图(b)所示