第四章纳米CMOS器件中的栅工程 栅电极层、栅介质层和Si衬底构成的MIS结构称为栅结构。 其中栅电极层的功函数、栅介质层的厚度、介电常数、介 质层电荷及界面缺陷态度等因素直接决定着CMOS器件的 特性。 栅电极层为重掺杂的多晶硅和硅化物的复合结构,栅介质 为高质量的热氧化Si0,其氧化层电荷和界面缺陷态密度 均很低。 CMOS器件栅工程即是通过栅结构和栅材料的优化选择, 提高器件性能

• 栅电极层、栅介质层和Si衬底构成的MIS结构称为栅结构。 • 其中栅电极层的功函数、栅介质层的厚度、介电常数、介 质层电荷及界面缺陷态度等因素直接决定着CMOS器件的 特性。 • 栅电极层为重掺杂的多晶硅和硅化物的复合结构,栅介质 为高质量的热氧化SiO2,其氧化层电荷和界面缺陷态密度 均很低

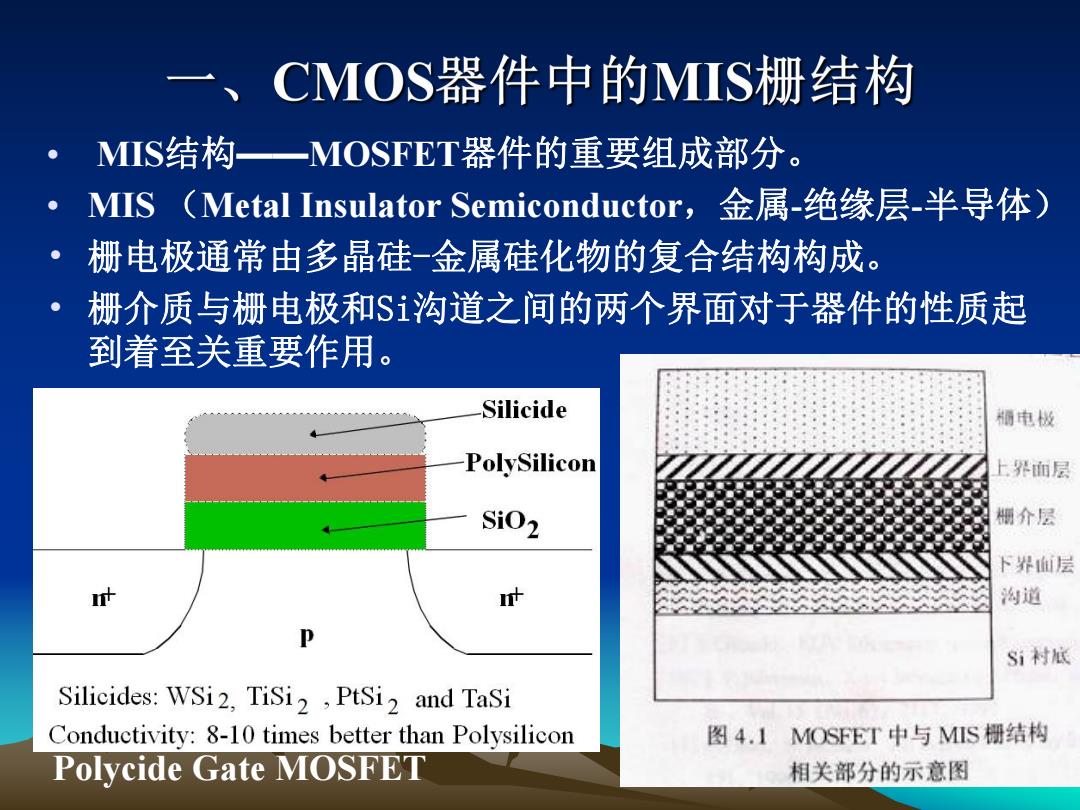

CMOS器件中的MⅡS栅结构 MIS结构一MOSFET器件的重要组成部分。 MIS(Metal Insulator Semiconductor,金属-绝缘层-半导体) 栅电极通常由多晶硅-金属硅化物的复合结构构成。 栅介质与栅电极和$沟道之间的两个界面对于器件的性质起 到着至关重要作用。 Silicide 料精电极 PolySilicon 上界血层 Si02 概介层 下界面层 t 沟道 P Si村底 Silicides:WSi2,TiSi2,PtSi2 and TaSi Conductivity:8-10 times better than Polysilicon 图4.1 MOSFET中与MIS栅结构 Polycide Gate MOSFET 相关部分的示意图

• MIS结构——MOSFET器件的重要组成部分。 • MIS (Metal Insulator Semiconductor,金属-绝缘层-半导体) • 栅电极通常由多晶硅-金属硅化物的复合结构构成。 • 栅介质与栅电极和Si沟道之间的两个界面对于器件的性质起 到着至关重要作用。 Polycide Gate MOSFET

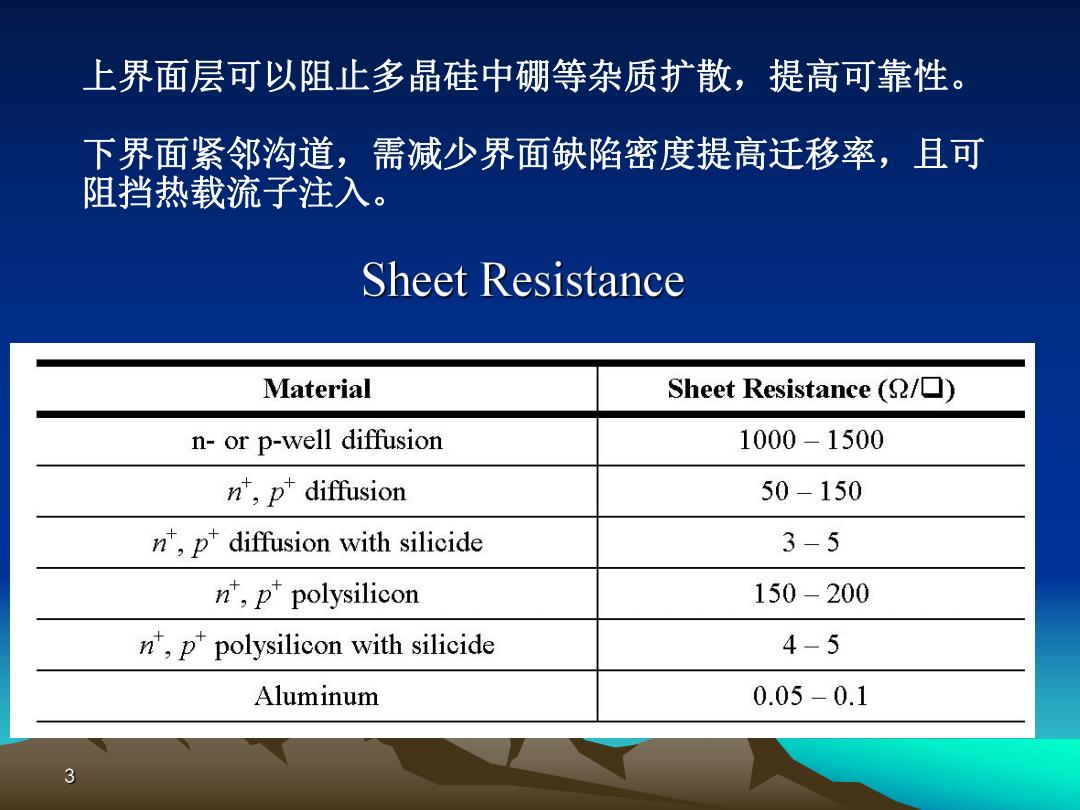

上界面层可以阻止多晶硅中硼等杂质扩散,提高可靠性。 下界面紧邻沟道,需减少界面缺陷密度提高迁移率,且可 阻挡热载流子注入。 Sheet Resistance Material Sheet Resistance (/ n-or p-well diffusion 1000-1500 n",p*diffusion 50-150 n',p diffusion with silicide 3-5 n,p*polysilicon 150-200 n,p polysilicon with silicide 4-5 Aluminum 0.05-0.1 3

上界面层可以阻止多晶硅中硼等杂质扩散,提高可靠性。 下界面紧邻沟道,需减少界面缺陷密度提高迁移率,且可 阻挡热载流子注入

栅介质、栅电极、S沟道之间的两个界面厚度通常在几个 埃的数量级,是栅电极、栅介质和S沟道之间材料的过渡。 当界面层的厚度与栅介质层的厚度接近时,界面层将直接 影响总的栅电容的大小,从而影响着MOSFET器件的性 能。这些界面层还可以加以利用以获得某些所需的作用 栅介质层:热氧化硅(SiO,) —新型栅介质材料如氮化 二氧化硅材料一高K栅介质材料。 MIS结构中栅介层的厚度t。决定了单位面积栅电容,表面 量子化效应和多晶硅耗尽效应等的影响,使栅电容降 低 等效的介质层厚度增加一 等效电容厚度CET增

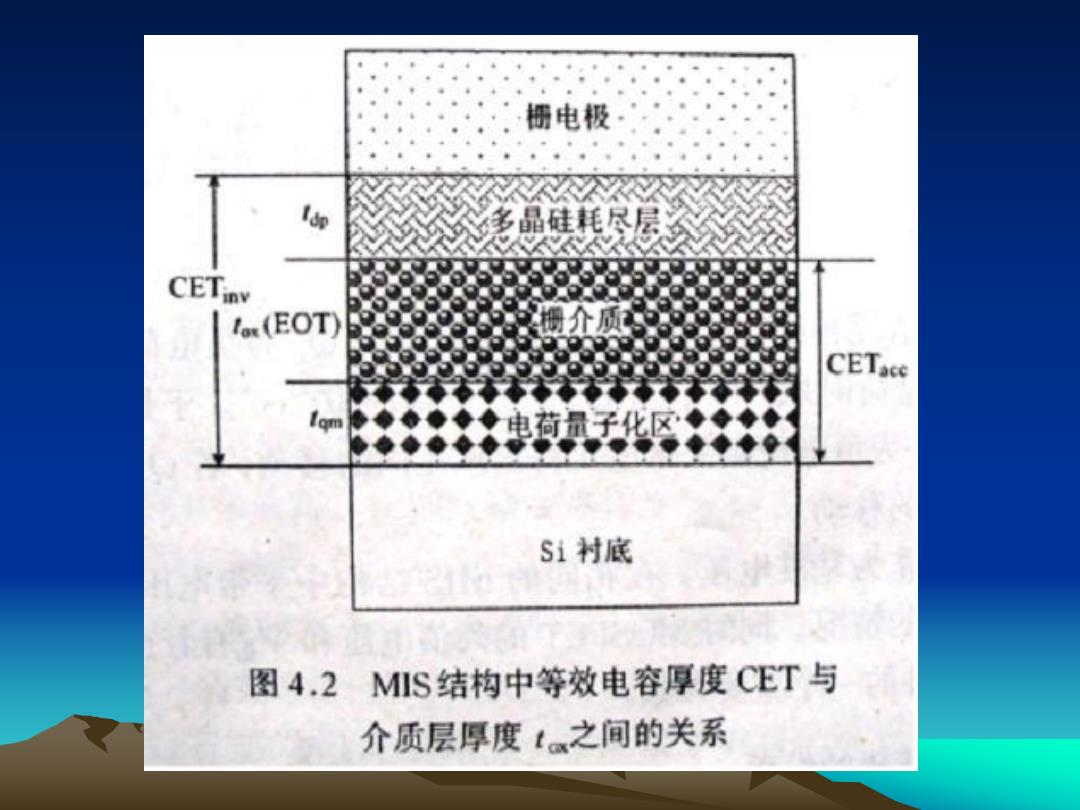

• 栅介质、栅电极、Si沟道之间的两个界面厚度通常在几个 埃的数量级,是栅电极、栅介质和Si沟道之间材料的过渡。 • 当界面层的厚度与栅介质层的厚度接近时,界面层将直接 影响总的栅电容的大小,从而影响着MOSFET器件的性 能。这些界面层还可以加以利用以获得某些所需的作用。 • 栅介质层:热氧化硅(SiO2)——新型栅介质材料如氮化 二氧化硅材料——高K栅介质材料。 • MIS结构中栅介层的厚度tox决定了单位面积栅电容,表面 量子化效应和多晶硅耗尽效应等的影响,使栅电容降 低 ——等效的介质层厚度增加——等效电容厚度CET增 加

栅电极 169 CETm¥ tar (EOT) CETace S1村底 图4.2MIS结构中等效电容厚度CET与 介质层厚度t之间的关系