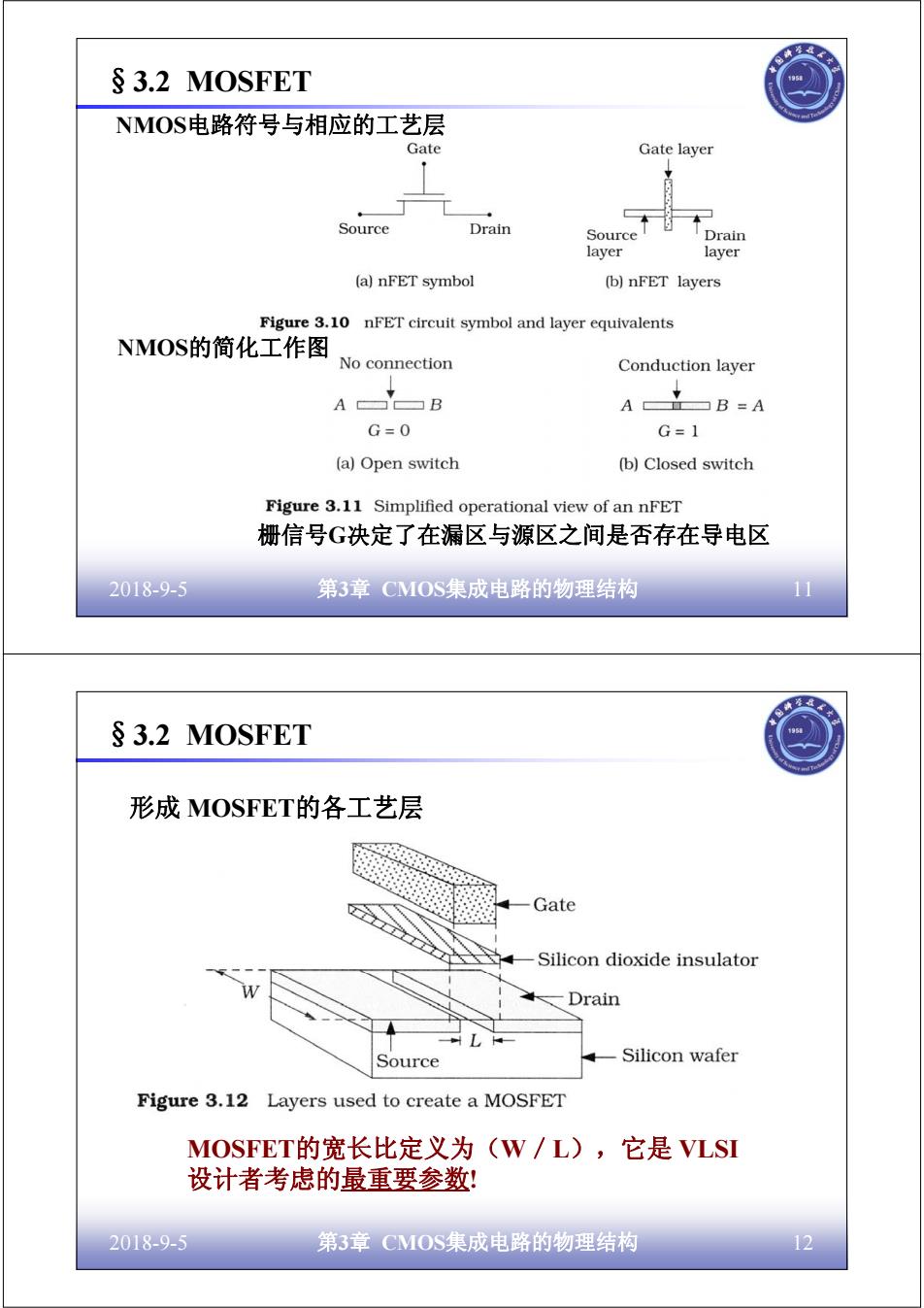

§3.2 MOSFET NMOS电路符号与相应的工艺层 Gate Gate layer Source Drain Source Drain layer layer (a)nFET symbol (b)nFET layers Figure 3.10 nFET circuit symbol and layer equivalents NMOS的简化工作图 No connection Conduction layer A☐B A☐B=A G=0 G=1 (a)Open switch (b)Closed switch Figure 3.11 Simplified operational view of an nFET 栅信号G决定了在漏区与源区之间是否存在导电区 2018-9-5 第3章CMOS集成电路的物理结构 §3.2 MOSFET 形成MOSFET的各工艺层 Gate 04 Silicon dioxide insulator Drain Source Silicon wafer Figure 3.12 Layers used to create a MOSFET MOSFET的宽长比定义为(W/L),它是VLSI 设计者考虑的最重要参数! 2018-9-5 第3章CMOS集成电路的物理结构 12

2018-9-5 第3章 CMOS集成电路的物理结构 11 §3.2 MOSFET NMOS电路符号与相应的工艺层 NMOS的简化工作图 栅信号G决定了在漏区与源区之间是否存在导电区 2018-9-5 第3章 CMOS集成电路的物理结构 12 §3.2 MOSFET 形成 MOSFET的各工艺层 MOSFET的宽长比定义为(W/L),它是 VLSI 设计者考虑的最重要参数!

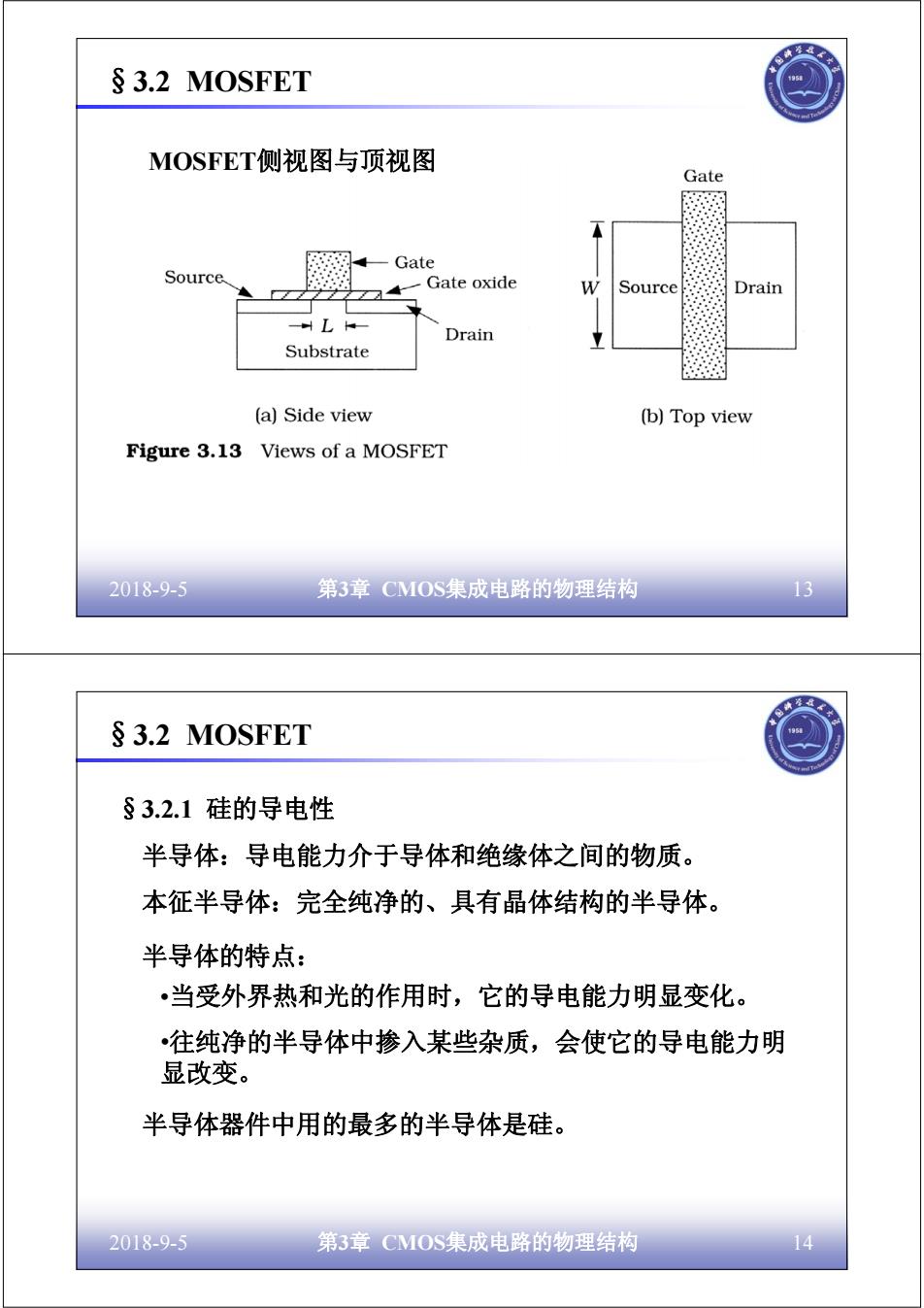

§3.2 MOSFET MOSFET侧视图与顶视图 Gate Gate Source Gate oxide Source Drain L Drain Substrate (a)Side view (b)Top view Figure 3.13 Views of a MOSFET 2018-9-5 第3章CMOS集成电路的物理结构 3 §3.2 MOSFET §3.2.1硅的导电性 半导体:导电能力介于导体和绝缘体之间的物质。 本征半导体:完全纯净的、具有晶体结构的半导体。 半导体的特点: •当受外界热和光的作用时,它的导电能力明显变化。 •往纯净的半导体中掺入某些杂质,会使它的导电能力明 显改变。 半导体器件中用的最多的半导体是硅。 2018-9-5 第3章CMOS集成电路的物理结构 14

2018-9-5 第3章 CMOS集成电路的物理结构 13 §3.2 MOSFET MOSFET侧视图与顶视图 2018-9-5 第3章 CMOS集成电路的物理结构 14 §3.2 MOSFET §3.2.1 硅的导电性 半导体:导电能力介于导体和绝缘体之间的物质。 半导体的特点: •当受外界热和光的作用时,它的导电能力明显变化。 •往纯净的半导体中掺入某些杂质,会使它的导电能力明 显改变。 半导体器件中用的最多的半导体是硅。 本征半导体:完全纯净的、具有晶体结构的半导体

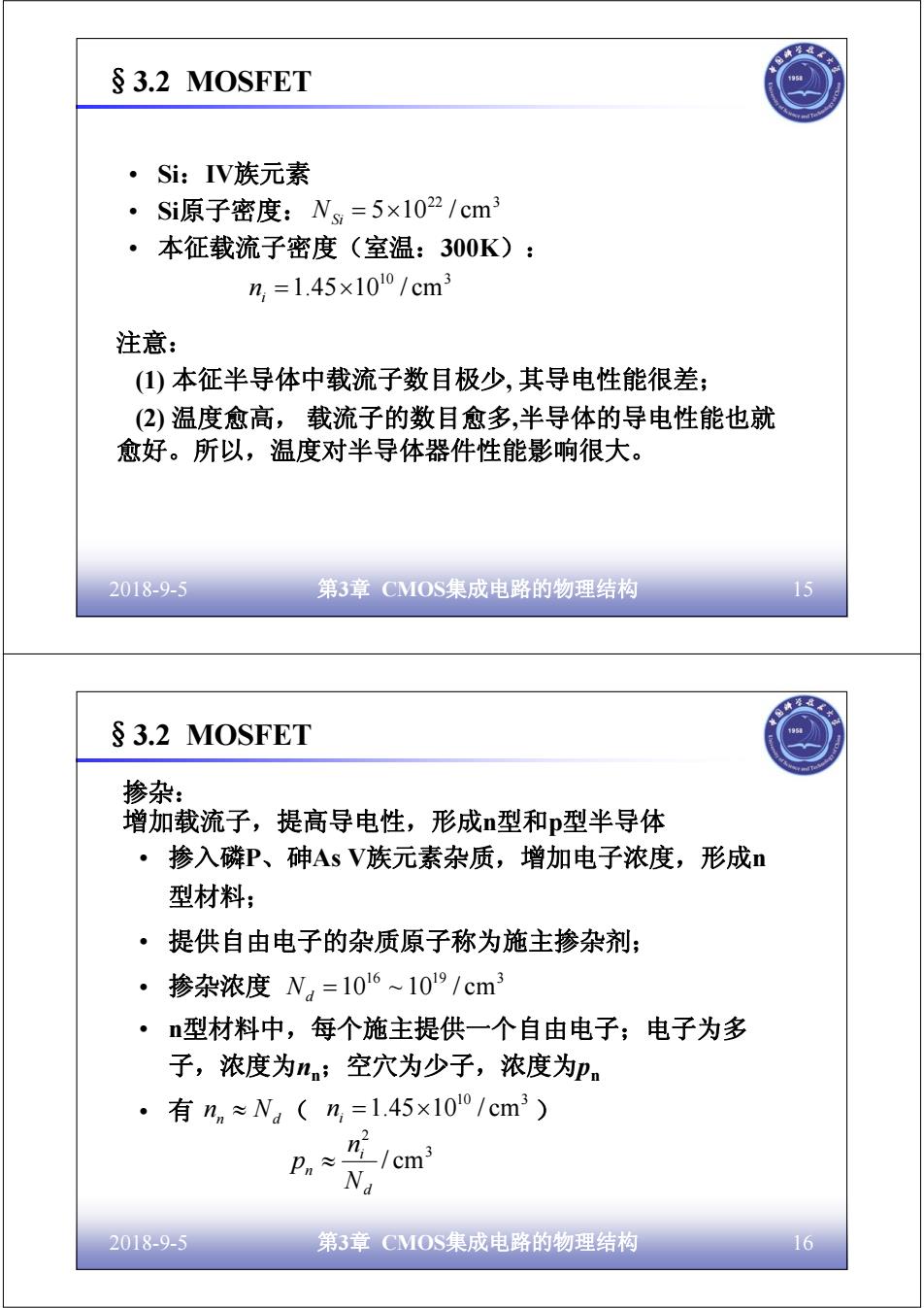

§3.2 MOSFET © Si:IV族元素 Si原子密度:N=5×1022/cm3 本征载流子密度(室温:300K): n,=1.45×1010/cm3 注意: (①)本征半导体中载流子数目极少,其导电性能很差; (2)温度愈高,载流子的数目愈多,半导体的导电性能也就 愈好。所以,温度对半导体器件性能影响很大。 2018-9-5 第3章CMOS集成电路的物理结构 15 §3.2 MOSFET 掺杂: 增加载流子,提高导电性,形成型和p型半导体 ·掺入磷P、砷AsV族元素杂质,增加电子浓度,形成和 型材料; 提供自由电子的杂质原子称为施主掺杂剂; ·掺杂浓度N,=1016~109/cm3 型材料中,每个施主提供一个自由电子;电子为多 子,浓度为n:空穴为少子,浓度为p。 ·有nn≈N.(n,=1.45×101°/cm3) , cm Na 2018-9-5 第3章CMOS集成电路的物理结构 16

2018-9-5 第3章 CMOS集成电路的物理结构 15 • Si:IV族元素 • Si原子密度: • 本征载流子密度(室温:300K): 22 3 NSi = 5×10 / cm 10 3 ni =1.45×10 / cm §3.2 MOSFET 注意: (1) 本征半导体中载流子数目极少, 其导电性能很差; (2) 温度愈高, 载流子的数目愈多,半导体的导电性能也就 愈好。所以,温度对半导体器件性能影响很大。 2018-9-5 第3章 CMOS集成电路的物理结构 16 掺杂: 增加载流子,提高导电性,形成n型和p型半导体 • 掺入磷P、砷As V族元素杂质,增加电子浓度,形成n 型材料; • 提供自由电子的杂质原子称为施主掺杂剂; • 掺杂浓度 • n型材料中,每个施主提供一个自由电子;电子为多 子,浓度为nn;空穴为少子,浓度为pn • 有( ) 3 2 / cm d i n N n p ≈ 10 3 ni =1.45×10 / cm 16 19 3 Nd =10 ~ 10 / cm nn ≈ Nd §3.2 MOSFET

§3.2 MOSFET 。 掺入硼BⅢ族元素,增加空穴,形成p型材料; 。 提供空穴的杂质原子称为受主掺杂剂; 掺杂浓度N。=104→10/cm3 。1 型材料中,每个受主提供一个空穴,空穴为多子, 浓度为pp;电子为少子,浓度为n。 并有Pp≈N。 np≈ N 2018-9-5 第3章CMOS集成电路的物理结构 §3.2 MOSFET 电导率σ 。 载流子密度为n和p的半导体区域电导率: =q(u n+upp) ·式中:"n和"p为电子和空穴迁移率,cmVs) 常温下本征硅: 4n=1360cm/(V.s) 'p=480cm/(V.s) 本征硅电导率ō≈4.27×10-6/2·cm) 本征硅电阻率p=1/o≈2.34×102cm ·N型材料:o≈q4nn ·P型材料:O≈q4pp 2018-9-5 第3章CMOS集成电路的物理结构 18

2018-9-5 第3章 CMOS集成电路的物理结构 17 • 掺入硼B III族元素,增加空穴,形成p型材料; • 提供空穴的杂质原子称为受主掺杂剂; • 掺杂浓度 • p型材料中,每个受主提供一个空穴,空穴为多子, 浓度为pp;电子为少子,浓度为np • 并有 14 19 3 Na =10 →10 / cm 3 2 / cm N n n a i p ≈ pp ≈ Na §3.2 MOSFET 2018-9-5 第3章 CMOS集成电路的物理结构 18 电导率σ • 载流子密度为n和p的半导体区域电导率: • 式中: 和 为电子和空穴迁移率, • 常温下本征硅: • 本征硅电导率 • 本征硅电阻率 • N型材料: • P型材料: q( n p) σ = μ n + μ p μ n μ p 1360cm /(V s) 2 = ⋅ μn 480cm /(V s) 2 = ⋅ μ p cm /(V s) 2 ⋅ 4.27 10 /( cm) 6 ≈ × Ω⋅ − σ 1/ 2.34 10 cm 5 ρ = σ ≈ × Ω⋅ σ ≈ qμ n n σ ≈ qμ p p §3.2 MOSFET