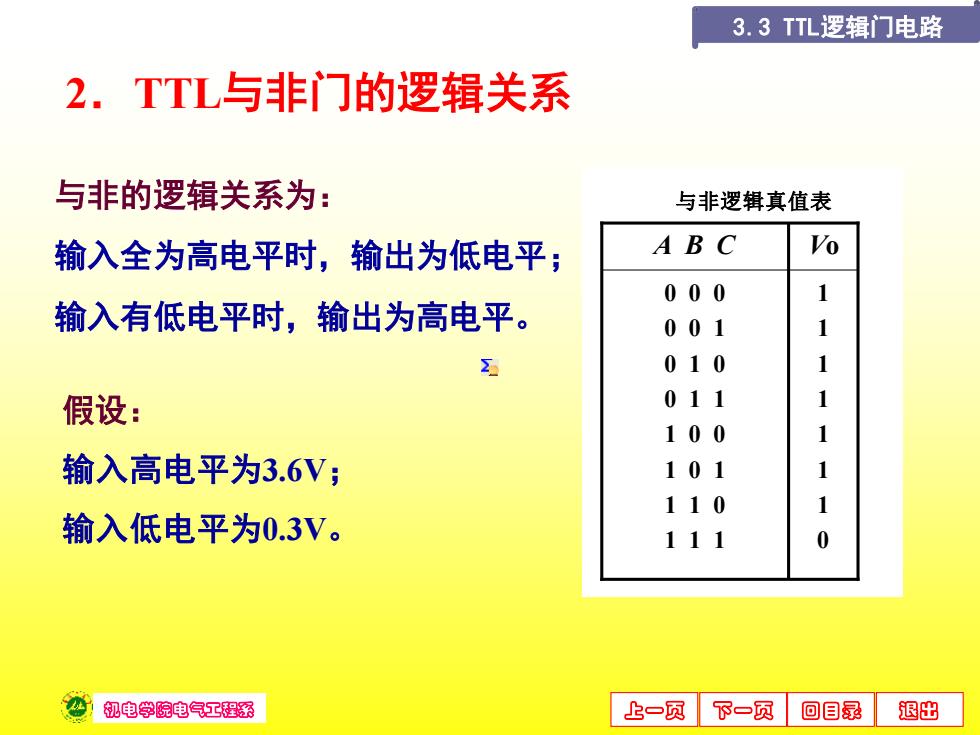

3.3TTL逻辑门电路 2.TTL与非门的逻辑关系 与非的逻辑关系为: 与非逻辑真值表 输入全为高电平时,输出为低电平; ABC Vo 000 1 输入有低电平时,输出为高电平。 001 1 010 1 假设: 011 1 100 2 输入高电平为3.6V; 101 110 输入低电平为0.3V。 111 机电学院电气工程系 上一页 下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 2.TTL与非门的逻辑关系 与非的逻辑关系为: 输入全为高电平时,输出为低电平; 输入有低电平时,输出为高电平。 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 A B C 1 1 1 1 1 1 1 0 Vo 与非逻辑真值表 假设: 输入高电平为3.6V; 输入低电平为0.3V。 3.3 TTL逻辑门电路

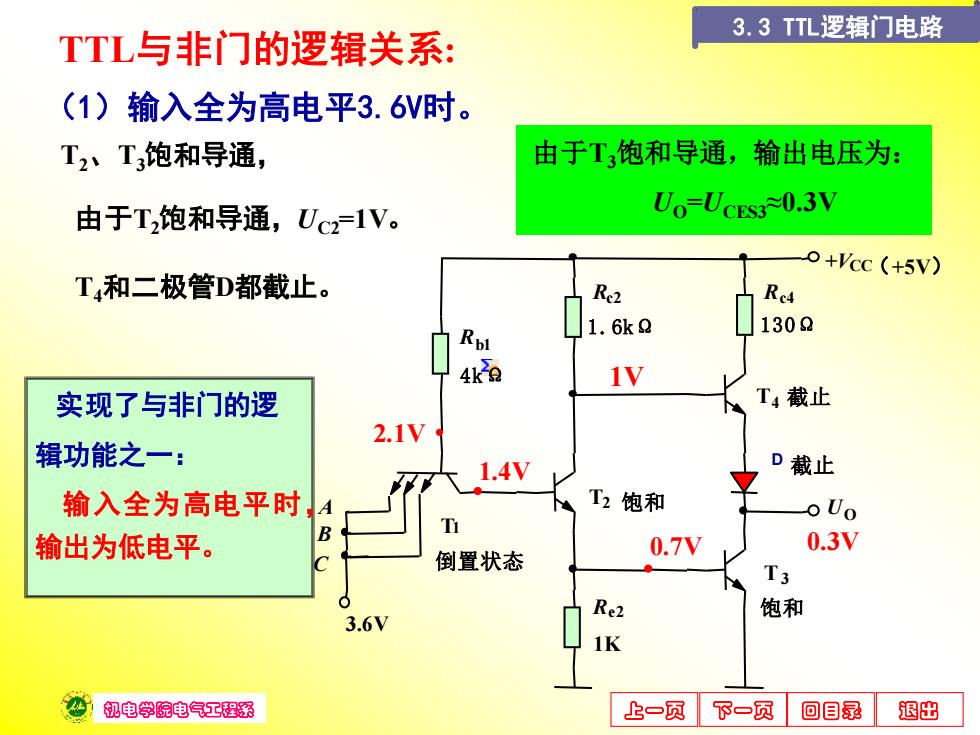

3.3TTL逻辑门电路 TTL与非门的逻辑关系: (1)输入全为高电平3.6V时。 T2T3饱和导通, 由于T,饱和导通,输出电压为: 由于T,饱和导通,Uc2=1V。 Uo-UCES3~-0.3V +Vcc (+5V) T和二极管D都截止。 Re2 Re4 1.6k2 1302 4k9 1V 实现了与非门的逻 T4截止 2.1V 辑功能之一: 1.4V D截止 输入全为高电平时 A T2饱和 oUo T 输出为低电平。 B 倒置状态 0.7V 0.3V T3 ● Re2 饱和 3.6V 1K 心机电学院电气工程繇 上一页 下一页 回目绿 退出

机电学院电气工程系 上一页 下一页 回目录 退出 U 3.6V +V 1 2 3 1 D 4kΩ R O 1.6kΩ c4 CC 130Ω e2 3 B c2 R (+5V) A 4 C 2 截止 倒置状态 b1 T 截止 1 T 饱和 1K 饱和 R R T T TTL与非门的逻辑关系: (1)输入全为高电平3.6V时。 T2、T3饱和导通, 实现了与非门的逻 辑功能之一: 输入全为高电平时, 输出为低电平。 由于T2饱和导通,UC2=1V。 T4和二极管D都截止。 由于T3饱和导通,输出电压为: UO=UCES3≈0.3V 2.1V 1.4V 0.7V 1V 0.3V 3.3 TTL逻辑门电路

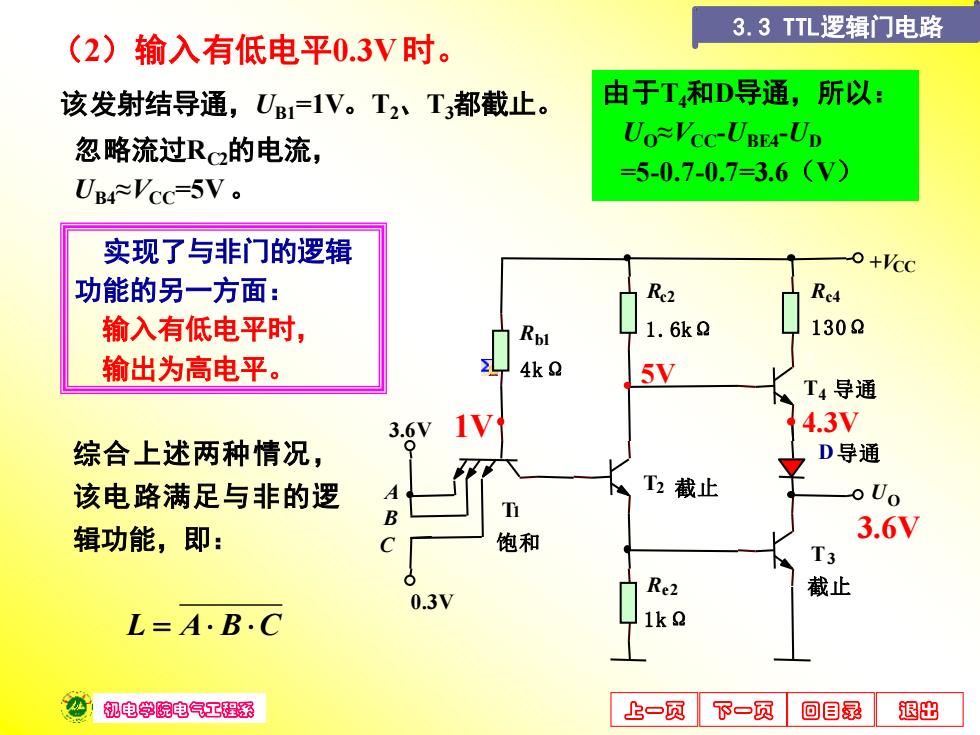

3.3TTL逻辑门电路 (2)输入有低电平0.3V时。 该发射结导通,UB1=1V。T2、T3都截止。 由于T和D导通,所以: 忽略流过R2的电流, UO-VCC-UBEA-UD =5-0.7-0.7=3.6(V) UB4'cc=5V。 实现了与非门的逻辑 +VCC 功能的另一方面: Re2 Re4 输入有低电平时, Rbl 1.6k 1302 输出为高电平。 4k2 5V T4导通 3.6V 4.3V 综合上述两种情况, D导通 该电路满足与非的逻 T2截止 oUo B T 辑功能,即: 饱和 3.6V T3 0.3V Re2 截止 L=A.B.C 1k2 机电学院电气工程系 上一页 下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 该发射结导通,UB1=1V。T2、T3都截止。 (2)输入有低电平0.3V时。 实现了与非门的逻辑 功能的另一方面: 输入有低电平时, 输出为高电平。 忽略流过RC2的电流, UB4≈VCC=5V 。 由于T4和D导通,所以: UO≈VCC-UBE4 -UD =5-0.7-0.7=3.6(V) L = A B C 综合上述两种情况, 该电路满足与非的逻 辑功能,即: 1V 5V 4.3V3.6V 3.3 TTL逻辑门电路 +V U 0.3V 3.6V 1 3 1 2 3 1 2 3 D 1 2 3 R 130Ω 1 c2 c4 3 B A CC T2 R C R R T 4 b1 T T 4kΩ e2 饱和 截止 截止 导通 导通 1.6kΩ 1kΩ O

3.3TTL逻辑门电路 二、TTL与非门的开关速度 1.TTL与非门提高工作速度的原理 (1)采用多发射极三极管加快了存储电荷的消散过程。 o+VCC 1.6k2 4k2 3.6V 4V B B/BI 0.7V 0.3V 必,机电学院电气工 上一页下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 二、TTL与非门的开关速度 1.TTL与非门提高工作速度的原理 (1)采用多发射极三极管加快了存储电荷的消散过程。 3.3 TTL逻辑门电路 +V 0.3V 3.6V U 1 3 R 1 c2 3 B A CC T2 R C R T b1 T e2 1V 1.4V 0.7V β iB1 iB1 4kΩ 1.6kΩ 1kΩ O

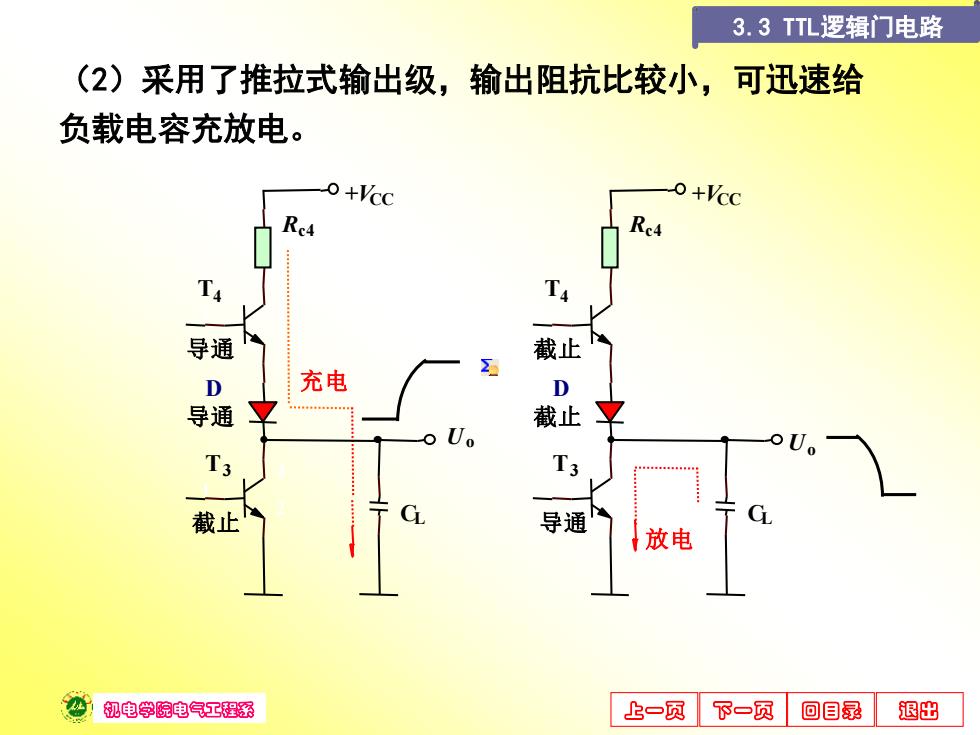

3.3TTL逻辑门电路 (2)采用了推拉式输出级,输出阻抗比较小,可迅速给 负载电容充放电。 o+Vcc o+VCC T4 T4 导通 截止 D 充电 D 导通 截止 Uo ● T3 T3 截止 导通 放电 机电学院电气工程系 上一页下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 (2)采用了推拉式输出级,输出阻抗比较小,可迅速给 负载电容充放电。 3.3 TTL逻辑门电路 +V U 1 2 3 1 2 3 D CC c4 截止 T3 T4 导通 导通 R 充电 CL o +V U 1 2 3 1 2 3 D c4 CC 导通 T3 T4 截止 截止 R 放电 CL o