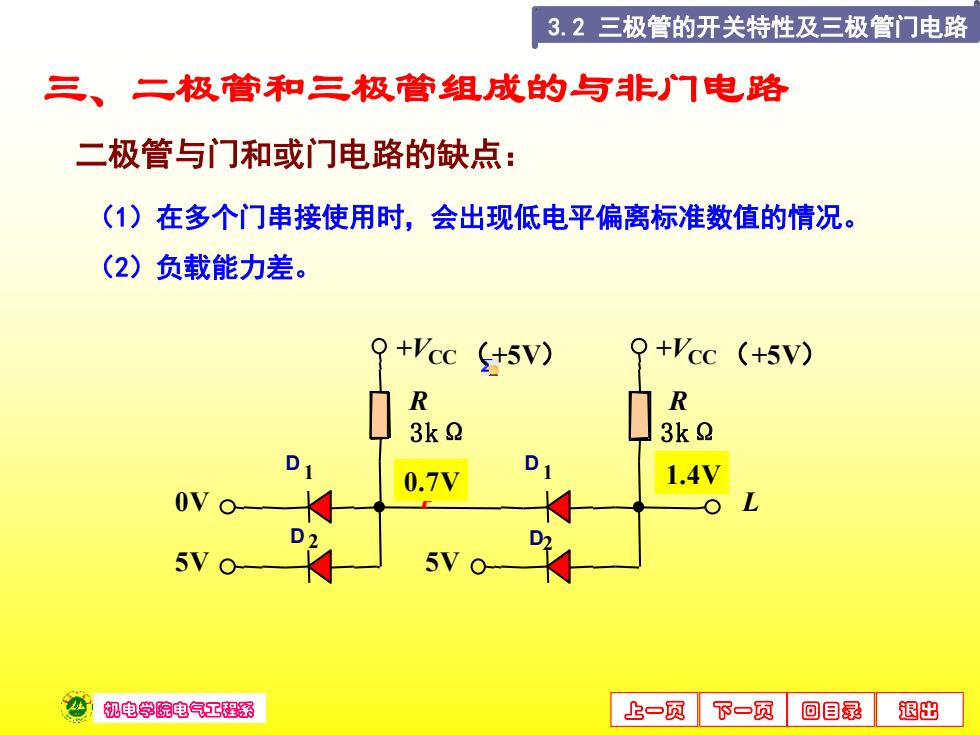

3.2三极管的开关特性及三极管门电路 三、二极管和三极管组成的与非门电路 二极管与门和或门电路的缺点: (1)在多个门串接使用时,会出现低电平偏离标准数值的情况。 (2)负载能力差。 Q+Vcc( +5V) 9+Vcc(+5V) R R 3k2 3k2 D D 0.7V 1.4V D 5V o 机电学院电气工程系 上一页下一页回目绿 退出

机电学院电气工程系 上一页 下一页 回目录 退出 0V 5V L 5V +V +V D D D D 1 2 1 3kΩ R R 3kΩ 2 CC (+5V) CC (+5V) p 二极管与门和或门电路的缺点: (1)在多个门串接使用时,会出现低电平偏离标准数值的情况。 (2)负载能力差。 三、二极管和三极管组成的与非门电路 3.2 三极管的开关特性及三极管门电路 0.7V 1.4V

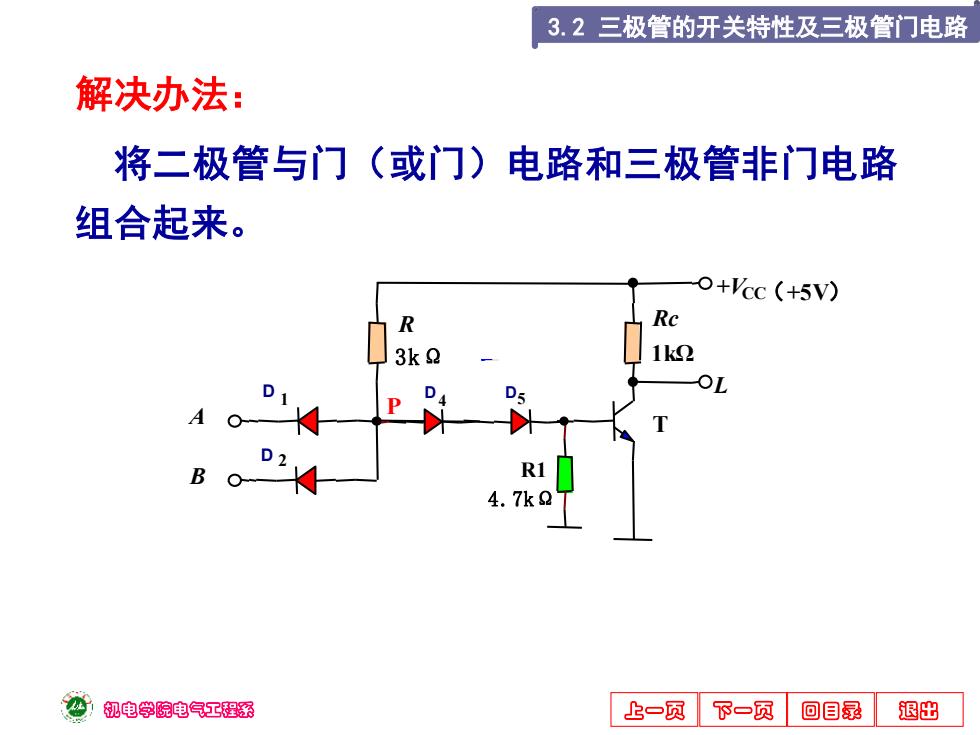

3.2三极管的开关特性及三极管门电路 解决办法: 将二极管与门(或门)电路和三极管非门电路 组合起来。 +Vcc (+5V) Rc 3k2 1k2 D R 4.7k 机电学院电气工程系 上一页下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 解决办法: 将二极管与门(或门)电路和三极管非门电路 组合起来。 3.2 三极管的开关特性及三极管门电路 L B A +V D D 1kΩ T P (+5V) 1 R 2 Rc 3kΩ CC D RbD5 R1 4.7kΩ 4

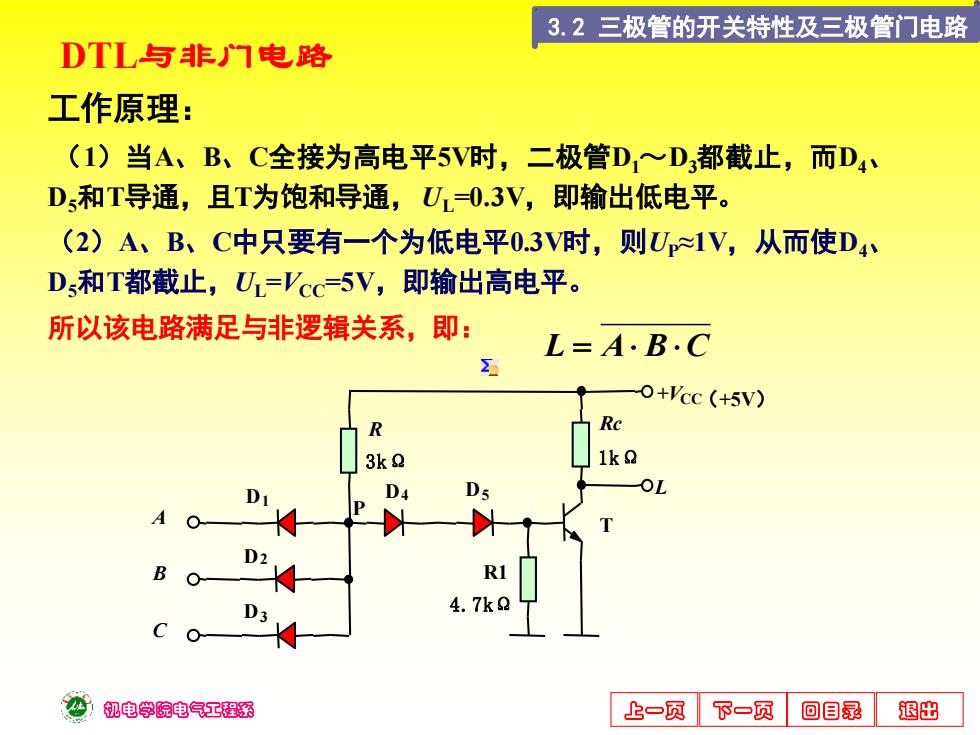

3.2三极管的开关特性及三极管门电路 DTL与非门电路 工作原理: (1)当A、B、C全接为高电平5V时,二极管D1~D都截止,而D4 D和T导通,且T为饱和导通,U=0.3V,即输出低电平。 (2)A、B、C中只要有一个为低电平0.3V时,则U1V,从而使D4 Ds和T都截止,U='cc=5V,即输出高电平。 所以该电路满足与非逻辑关系,即: L=A.B.C E O+Vcc (+5V) 3k 1k2 机电学院电气工程系 上一页下一页回目绿 退出

机电学院电气工程系 上一页 下一页 回目录 退出 L = A B C DTL与非门电路 工作原理: (1)当A、B、C全接为高电平5V时,二极管D1 ~D3都截止,而D4、 D5和T导通,且T为饱和导通,UL =0.3V,即输出低电平。 (2)A、B、C中只要有一个为低电平0.3V时,则UP≈1V,从而使D4、 D5和T都截止,UL=VCC=5V,即输出高电平。 所以该电路满足与非逻辑关系,即: 3.2 三极管的开关特性及三极管门电路 A B C L +V D D D 1 2 D D 3 1 R 2 3 CC(+5V) R1 Rc T 4 5 P 3kΩ 1kΩ 4.7kΩ

3.3TTL逻辑门电路 一、TTL与非门的基本结构及工作原理 1.TTL与非门的基本结构 +Vcc (+5V) R Rc 3k2 1k2 D4 -OL 9+Ψcc(+5V) 4.7k O 机电学院电气工程系 上一页下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 3.3 TTL逻辑门电路 一、TTL与非门的基本结构及工作原理 1.TTL与非门的基本结构 A B C L +V D D D 1 2 D D 3 1 R 2 3 CC(+5V) R1 Rc T 4 5 P 3kΩ 1kΩ 4.7kΩ +VCC (+5V) A B C T b1 R 1

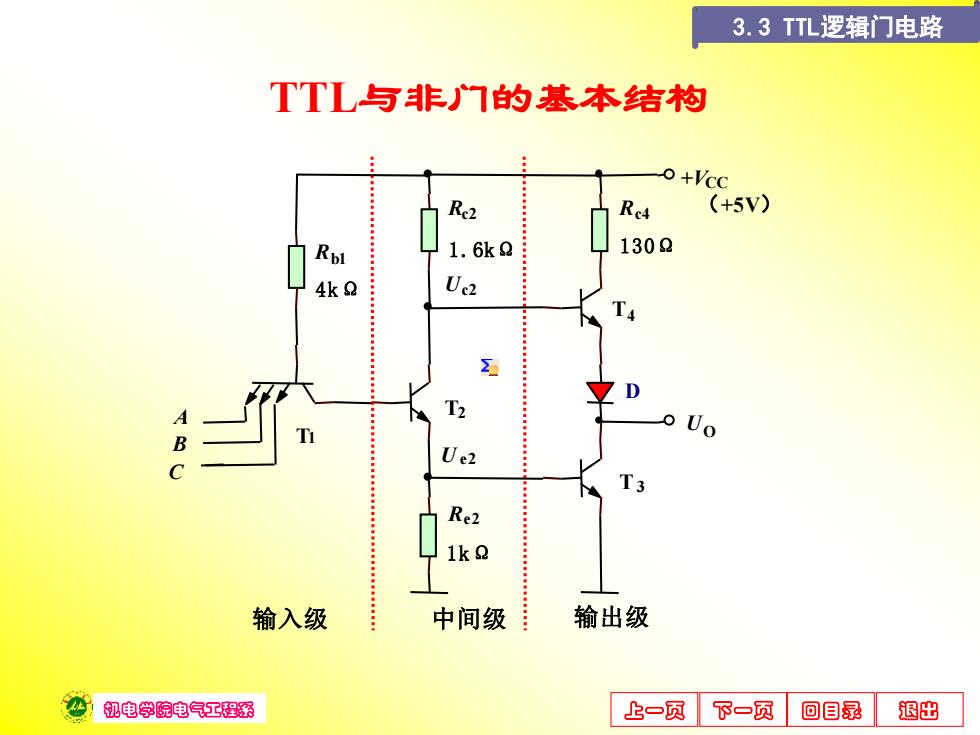

3.3TTL逻辑门电路 TTL与非门的基本结构 o+VCC Re2 Re4 (+5V) 1.6k2 1302 4k2 Ue D T2 B Ue2 Re2 1k2 输入级 中间级 输出级 机电学院电气工程系 上一页下一页 回目录 退出

机电学院电气工程系 上一页 下一页 回目录 退出 TTL与非门的基本结构 3.3 TTL逻辑门电路 (+5V) +V U 1 2 3 1 2 3 D 1 2 3 1 3 CC R 130Ω A B C T T T R T 4kΩ Rb1 1 2 4 3 c2 c4 Re2 U U c2 e2 输入级 中间级 输出级 1.6kΩ 1kΩ O