ΠΠΠΠΠΠΠΠΠΠΠ 图5-264位异步二进制加法计数器时序图 222o @@-@-@-@-@-@w-@ @@@-@@-四-@@ 图5-274位异步二进制加法计数器状态图 另外,从时序图可以看出,Q。、Q、Q、Q的周期分别是计数脉冲(CP)周期的2 倍、4倍、8倍、16倍,也就是说,Q。、Q、Q,分别对CP波形进行了二分频、 四分频、八分频、十六分频,因而计数器也可作为分频器。 异步二进制计数器结构简单,改变级联触发器的个数,可以很方便地改变二进制 计数器的位数,n个触发器构成n位二进制计数器或模2”计数器,或2”分频器。 2、异步二进制减法计数器 将图5-25所示电路中FF、FF、FE的时钟脉冲输入端改接到相邻低位触发器的 Q端就可构成二进制异步减法计数器。 图5-28所示是用4个上升沿触发的D触发器组成的4位异步二进制减法计数器 的逻辑图。 CR清零脉冲 Cp计数脉冲 图5-28D触发器组成的4位异步二进制减法计数器的逻辑图 该电路的时序波形图如图5-29所示,状态图如图5-30所示

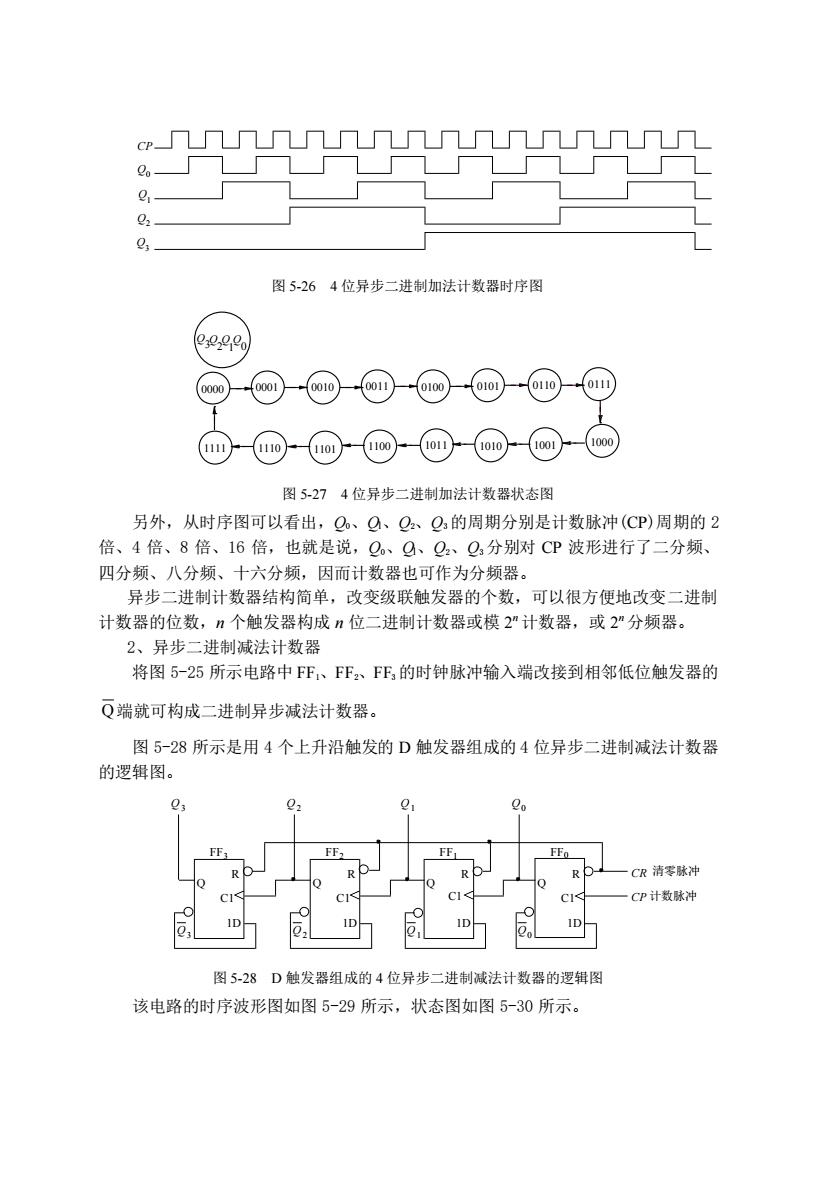

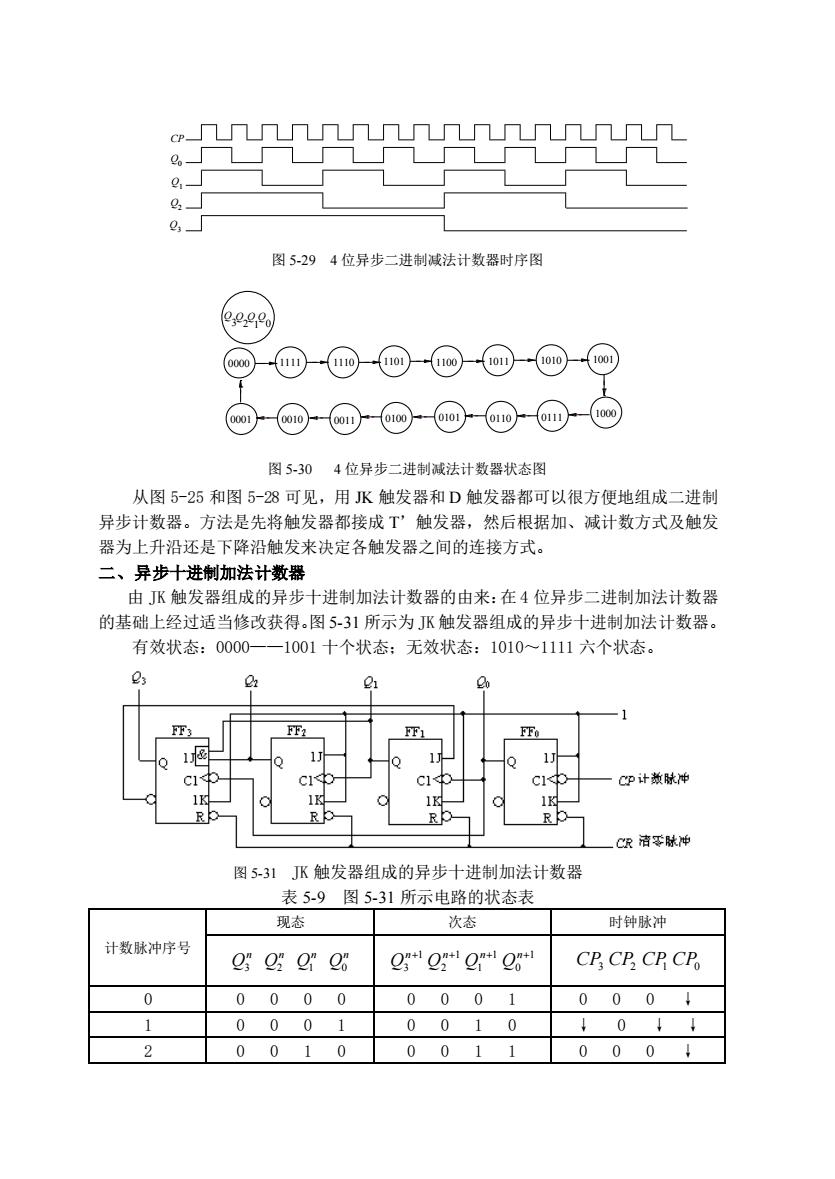

CP Q0 Q1 Q2 Q3 图 5-26 4 位异步二进制加法计数器时序图 3 2 1 0 Q Q Q Q 0000 0001 0010 0011 0100 0101 0110 0111 1000 1100 1011 1010 1001 1111 1110 1101 图 5-27 4 位异步二进制加法计数器状态图 另外,从时序图可以看出,Q0、Ql、Q2、Q3 的周期分别是计数脉冲(CP)周期的 2 倍、4 倍、8 倍、16 倍,也就是说,Q0、Ql、Q2、Q3 分别对 CP 波形进行了二分频、 四分频、八分频、十六分频,因而计数器也可作为分频器。 异步二进制计数器结构简单,改变级联触发器的个数,可以很方便地改变二进制 计数器的位数,n 个触发器构成 n 位二进制计数器或模 2 n 计数器,或 2 n 分频器。 2、异步二进制减法计数器 将图 5-25 所示电路中 FF1、FF2、FF3 的时钟脉冲输入端改接到相邻低位触发器的 Q 端就可构成二进制异步减法计数器。 图 5-28 所示是用 4 个上升沿触发的 D 触发器组成的 4 位异步二进制减法计数器 的逻辑图。 C1 CP FF3 1D ∧ Q3 计数脉冲 Q R Q3 1D Q Q2 FF2 C1 ∧ R Q2 1D Q Q1 FF1 C1 ∧ R Q1 1D Q Q0 FF0 C1 ∧ R Q0 CR 清零脉冲 图 5-28 D 触发器组成的 4 位异步二进制减法计数器的逻辑图 该电路的时序波形图如图 5-29 所示,状态图如图 5-30 所示

g☐ 图5-294位异步二进制减法计数器时序图 29 @-四-@@@@-⊙@ @-@-@-⊙-@@@@ 图5-304位异步二进制减法计数器状态图 从图5-25和图5-28可见,用K触发器和D触发器都可以很方便地组成二进制 异步计数器。方法是先将触发器都接成T'触发器,然后根据加、减计数方式及触发 器为上升沿还是下降沿触发来决定各触发器之间的连接方式。 二、异步十进制加法计数器 由JK触发器组成的异步十进制加法计数器的由来:在4位异步二进制加法计数器 的基础上经过适当修改获得.图5-31所示为JK触发器组成的异步十进制加法计数器。 有效状态:0000一一1001十个状态:无效状态:1010~1111六个状态。 2 CP计数脉冲 C欧洁零脉冲 图5-31JK触发器组成的异步十进制加法计数器 表5-9图5-31所示电路的状态表 现春 次态 时钟脉冲 计数脉冲序号 oo:o"O OOO CPCPCP CP 0 0000 0001 000↓ 0 00 0 0 10 0 0 01 0 001 000

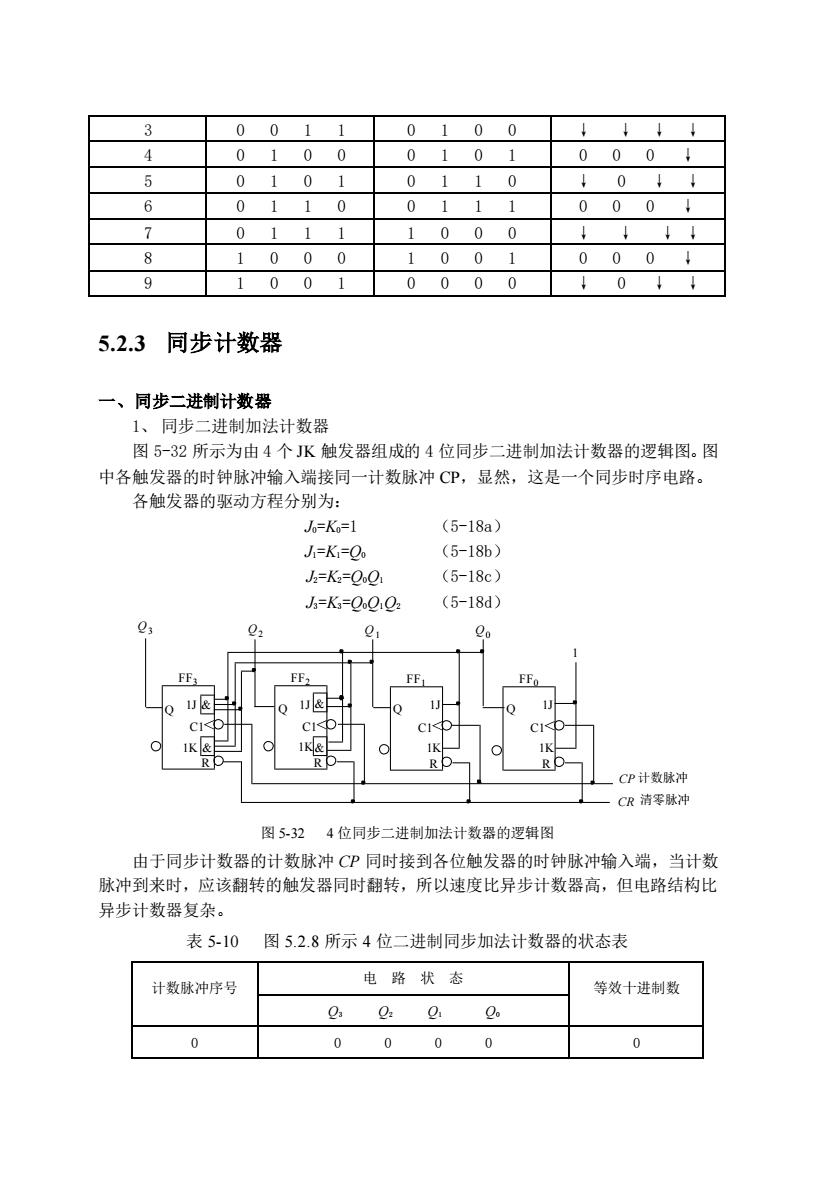

Q CP Q0 Q 2 1 Q 3 图 5-29 4 位异步二进制减法计数器时序图 3 2 1 0 Q Q Q Q 0000 1111 1110 1101 1100 1011 1010 1001 1000 0100 0101 0110 0111 0001 0010 0011 图 5-30 4 位异步二进制减法计数器状态图 从图 5-25 和图 5-28 可见,用 JK 触发器和 D 触发器都可以很方便地组成二进制 异步计数器。方法是先将触发器都接成 T’触发器,然后根据加、减计数方式及触发 器为上升沿还是下降沿触发来决定各触发器之间的连接方式。 二、异步十进制加法计数器 由 JK 触发器组成的异步十进制加法计数器的由来:在 4 位异步二进制加法计数器 的基础上经过适当修改获得。图 5-31 所示为 JK 触发器组成的异步十进制加法计数器。 有效状态:0000——1001 十个状态;无效状态:1010~1111 六个状态。 图 5-31 JK 触发器组成的异步十进制加法计数器 表 5-9 图 5-31 所示电路的状态表 计数脉冲序号 现态 次态 时钟脉冲 3 n Q 2 n Q 1 n Q 0 n Q 1 3 n Q + 1 2 n Q + 1 1 n Q + 1 0 n Q + CP3 CP2 CP1 CP0 0 0 0 0 0 0 0 0 1 0 0 0 ↓ 1 0 0 0 1 0 0 1 0 ↓ 0 ↓ ↓ 2 0 0 1 0 0 0 1 1 0 0 0 ↓

3 0011 0100 ↓↓↓ 4 0 1 00 010 0 0 0 5 0 0 01 1 0 0 0 1 0 0 1 00 0 00 0 8 0 0 0 0 1 0 0 0 00 0 0 5.2.3同步计数器 一、同步二进制计数器 1、同步二进制加法计数器 图5-32所示为由4个JK触发器组成的4位同步二进制加法计数器的逻辑图。图 中各触发器的时钟脉冲输入端接同一计数脉冲CP,显然,这是一个同步时序电路。 各触发器的驱动方程分别为: =K=1 (5-18a) J1=K=O。 (5-18b) J=K=O.O (5-18c) =K3=0010: (5-18d) 0 FF R● CP计数脉河 CR清零脉冲 图5324位同步二进制加法计数器的逻辑图 由于同步计数器的计数脉冲CP同时接到各位触发器的时钟脉冲输入端,当计数 脉冲到来时,应该翻转的触发器同时翻转,所以速度比异步计数器高,但电路结构比 异步计数器复杂。 表5-10图5.2.8所示4位二进制同步加法计数器的状态表 计数脉冲序号 电路状态 等效十进制数 es O:0 0. 0 0 0 0 0 0

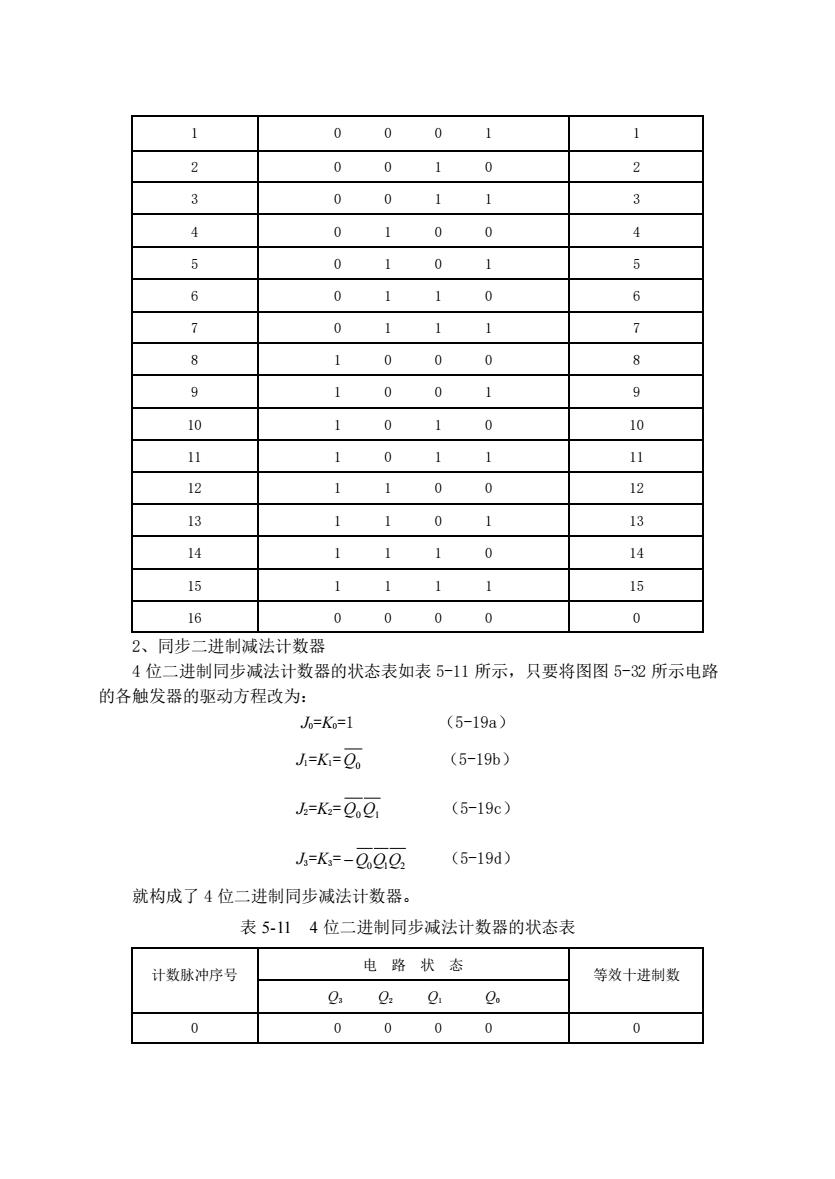

3 0 0 1 1 0 1 0 0 ↓ ↓ ↓ ↓ 4 0 1 0 0 0 1 0 1 0 0 0 ↓ 5 0 1 0 1 0 1 1 0 ↓ 0 ↓ ↓ 6 0 1 1 0 0 1 1 1 0 0 0 ↓ 7 0 1 1 1 1 0 0 0 ↓ ↓ ↓ ↓ 8 1 0 0 0 1 0 0 1 0 0 0 ↓ 9 1 0 0 1 0 0 0 0 ↓ 0 ↓ ↓ 5.2.3 同步计数器 一、同步二进制计数器 1、 同步二进制加法计数器 图 5-32 所示为由 4 个 JK 触发器组成的 4 位同步二进制加法计数器的逻辑图。图 中各触发器的时钟脉冲输入端接同一计数脉冲 CP,显然,这是一个同步时序电路。 各触发器的驱动方程分别为: J0=K0=1 (5-18a) J1=K1=Q0 (5-18b) J2=K2=Q0Q1 (5-18c) J3=K3=Q0Q1Q2 (5-18d) Q Q 1K R 1J 2 Q C1 0 C1 ∧ 1 1J FF R Q 计数脉冲 CR 清零脉冲 ∧ 0 ∧ 1J Q R FF Q 1 1K ∧ C1 3 FF 1K R FF C1 CP 2 Q Q1 1K 1J 3 & & & & 图 5-32 4 位同步二进制加法计数器的逻辑图 由于同步计数器的计数脉冲 CP 同时接到各位触发器的时钟脉冲输入端,当计数 脉冲到来时,应该翻转的触发器同时翻转,所以速度比异步计数器高,但电路结构比 异步计数器复杂。 表 5-10 图 5.2.8 所示 4 位二进制同步加法计数器的状态表 计数脉冲序号 电 路 状 态 等效十进制数 Q3 Q2 Q1 Q0 0 0 0 0 0 0

0 0 0 1 1 2 0 0 1 0 2 3 0 0 1 1 4 0 1 0 0 4 5 0 0 1 5 6 0 1 0 6 7 0 1 1 1 R 1 00 0 8 9 0 0 1 10 0 0 10 1 0 1 1 11 12 0 0 12 13 1 0 1 13 14 1 1 0 14 15 1 15 16 0. 0 0 0 0 2、同步二进制减法计数器 4位二进制同步减法计数器的状态表如表5-11所示,只要将图图5-32所示电路 的各触发器的驱动方程改为: J=K=1 (5-19a) J=K=00 (5-19b) J=K:=000 (5-19c) =K3=-000. (5-19d) 就构成了4位二进制同步减法计数器。 表5-114位二进制同步减法计数器的状态表 计数脉冲序号 电路状态 等效十进制数 2,Q:2. 0 0 0 0 0 0

1 0 0 0 1 1 2 0 0 1 0 2 3 0 0 1 1 3 4 0 1 0 0 4 5 0 1 0 1 5 6 0 1 1 0 6 7 0 1 1 1 7 8 1 0 0 0 8 9 1 0 0 1 9 10 1 0 1 0 10 11 1 0 1 1 11 12 1 1 0 0 12 13 1 1 0 1 13 14 1 1 1 0 14 15 1 1 1 1 15 16 0 0 0 0 0 2、同步二进制减法计数器 4 位二进制同步减法计数器的状态表如表 5-11 所示,只要将图图 5-32 所示电路 的各触发器的驱动方程改为: J0=K0=1 (5-19a) J1=K1= Q0 (5-19b) J2=K2= Q0Q1 (5-19c) J3=K3= −Q0Q1Q2 (5-19d) 就构成了 4 位二进制同步减法计数器。 表 5-11 4 位二进制同步减法计数器的状态表 计数脉冲序号 电 路 状 态 等效十进制数 Q3 Q2 Q1 Q0 0 0 0 0 0 0