数字化仪器发展的限制 ▣高带宽/高响应速度 高采样率 口高精度 ▣高集成度 高分辨位数 采样率与分辨位数是一对矛盾 采样率 分辨位数 MAXIM:MAX1337 6GSa/s 8Bit NS:ADC083000 3GSa/s 8Bit MAXIM:MAX1320 2GSa/s 14Bit AD:AD7643 1.25GSa/s 18Bit TI:ADS1217 780Sa/s 24Bit 解决思路之一:TIADC

数字化仪器发展的限制 采样率 分辨位数 MAXIM:MAX1337 6GSa/s 8Bit NS:ADC083000 3GSa/s 8Bit MAXIM: MAX1320 2GSa/s 14Bit AD:AD7643 1.25GSa/s 18Bit TI:ADS1217 780Sa/s 24Bit 采样率与分辨位数是一对矛盾 高采样率 高分辨位数 解决思路之一:TIADC 高带宽/高响应速度 高精度 高集成度

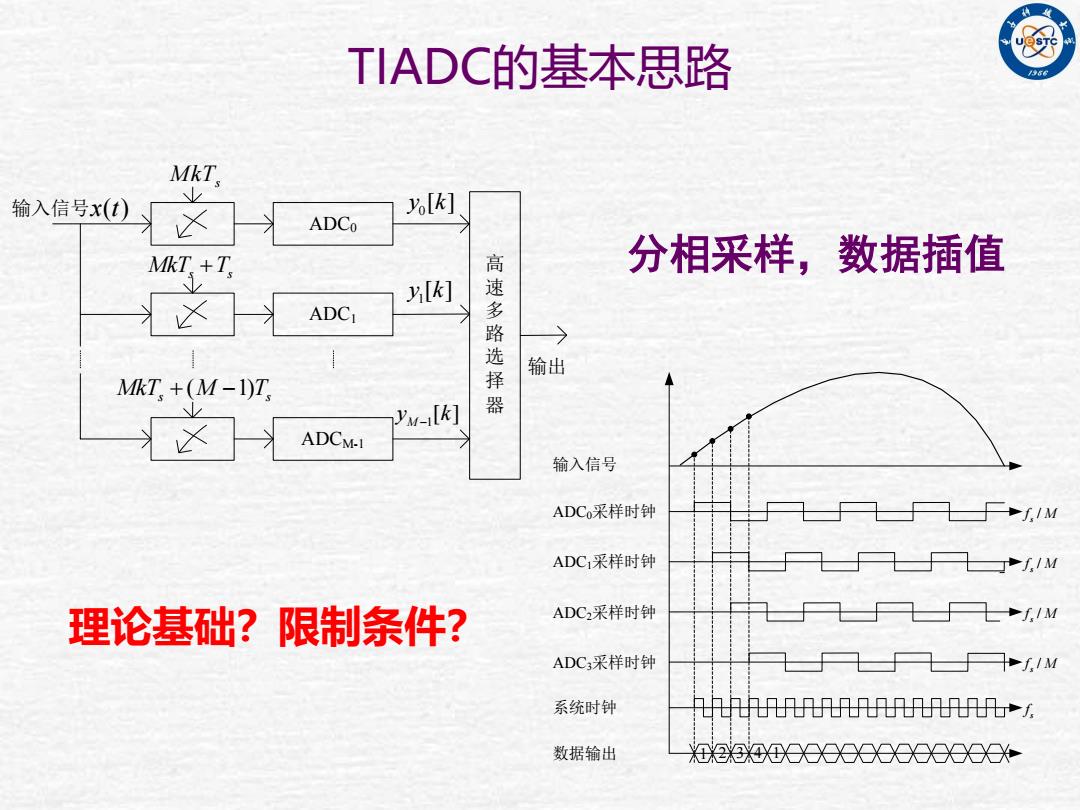

TIADC的基本思路 MkT, 输入信号x(t) [k] ADCo MkT+T, 分相采样,数据插值 y[k] X ADCI 速多路 选择器 输出 MkT,+(M-1)T, Yv-[k] ADCM-1 输入信号 ADCo采样时钟 f/M ADC1采样时钟 ∫1M 理论基础?限制条件? ADC2采样时钟 -f/M ADC3采样时钟 系统时钟 数据输出 知a3知00OO8O00000O0:

TIADC的基本思路 ADC1 输入信号 MkT T s s x t( ) ADC0 MkTs ADCM-1 ( 1) MkT M T s s 高 速 多 路 选 择 器 输出 0 y k[ ] 1 y k[ ] 1[ ] M y k 输入信号 ADC0采样时钟 ADC1采样时钟 ADC2采样时钟 ADC3采样时钟 系统时钟 数据输出 1 2 3 4 1 sf / sf M/ sf M/ sf M/ sf M 理论基础?限制条件? 分相采样,数据插值

抽样率变换的其它一些应用 ▣基带信号产生 一降低滤波器设计难度 ▣实时信号处理 一通过并行处理提高速度 ▣多路DAC并行一提高DAC的采样率 ■■■■■■

抽样率变换的其它一些应用 基带信号产生 —— 降低滤波器设计难度 实时信号处理 —— 通过并行处理提高速度 多路DAC并行 —— 提高DAC的采样率 ……

例 问题思考 ▣可以用什么方法来改变采样率?

问题思考 可以用什么方法来改变采样率?

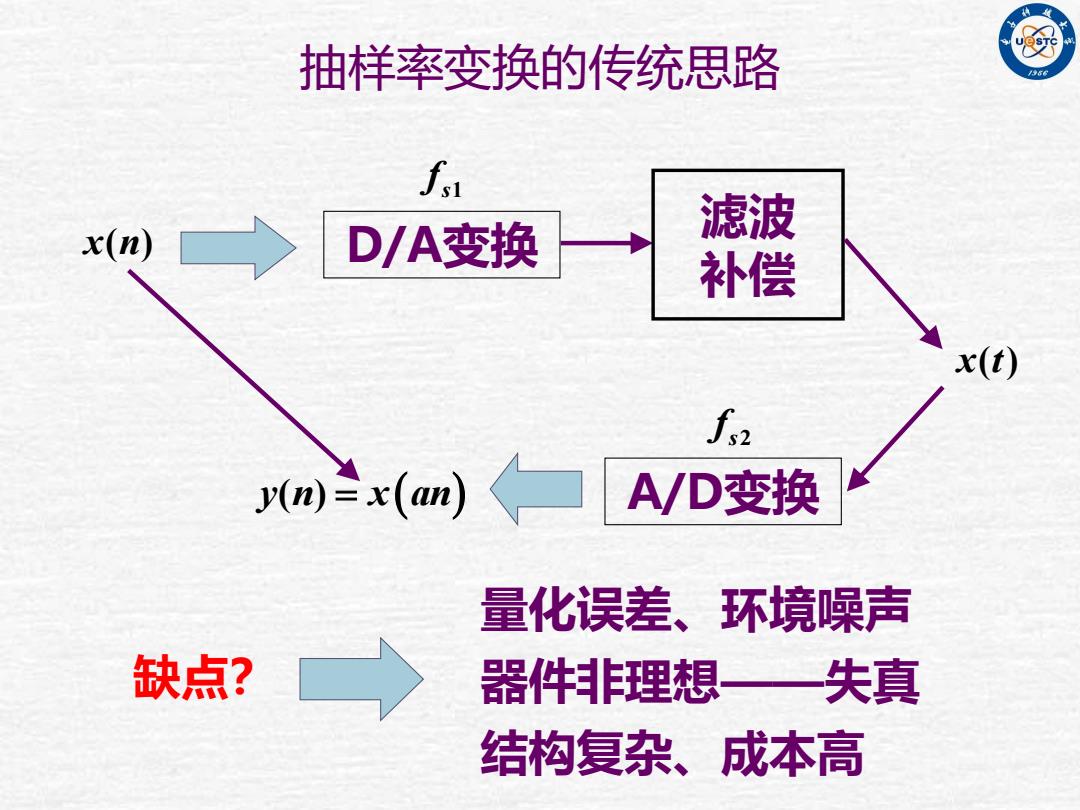

抽样率变换的传统思路 fa x(n) D/A变换 滤波 补偿 x(t) ym)=x(m)〈☐ AVD变换 量化误差、环境噪声 缺点? 器件非理想 失真 结构复杂、成本高

抽样率变换的传统思路 x n( ) 滤波 补偿 x t( ) y n x an ( ) 缺点? 量化误差、环境噪声 器件非理想——失真 结构复杂、成本高 D/A变换 s1 f A/D变换 s2 f