高精度、低功耗流水线型模数转换器的研究与设计 [59]Katsufumi Nakamura,Masao Hotta,L.Richard Carley,and David J.Allstot.An 85 mW,10b,40 Msample/s CMOS parallel-pipelined ADC [J].IEEE Journal of Solid-State Circuits,March 1995,30:173-183. [60]David William Cline.Noise,Speed,and Power Trade-offs in Pipelined Analog to Digital Converters[D].Ph.D thesis,UC,Berkeley 1995. [61]Paul C.Yu and Hae-Seung Lee.A 2.5V 12b 5Msample/s pipelined CMOS ADC [J]. IEEE International Solid-State Circuits Conference,February 1996,XXXIX:314- 315. [62]Hui Pan,Masahiro Segami,Michael Choi,Jing Cao,Fumitoshi Hatori,and Asad Abidi.A 3.3V,12b,50Msample/s A/D converter in 0.6um CMOS with over 80dB SFDR [J].IEEE International Solid-State Circuits Conference,February 2000,XLIII: 40-41. [63]Klaas Bult and Aaron Buchwald.An embedded 240-mW 10-b 50-MS/s CMOS ADC in 1-mm2[J].IEEE Journal of Solid-State Circuits,December 1997,32:1887-1895. [64]Andrew M.Abo and Paul R.Gray.A 1.5-V,10-bit,14.3-MS/s CMOS pipeline analog-to-digital converter [J].IEEE Journal of Solid-State Circuits,May 1999,34: 599-606. [65]Lauri Sumanen,Mikko Waltari,and Kari A.I.Halonen.A 10-bit 200-MS/s CMOS parallel pipeline A/D converter [J].IEEE Journal of Solid-State Circuits,July 2001,36: 1048-1055. [66]Jong-Bum Park,Sang-Min Yoo,Se-Won Kim,Young-Jae Cho,Seung-Hoon.A 10-b 150-MSample/s 1.8-V 123-mW CMOS A/D converter with 400-MHz input bandwidth [J].IEEE Journal of Solid-State Circuits,Aug.2004,39:1335-1337. [67]Jipeng Li,Un-Ku Moon.A 1.8-V 67-mW 10-bit 100-MS/s pipelined ADC using time-shifted CDS technique [J].IEEE Journal of Solid-State Circuits,Sept.2004,39: 1468-1476. [68]Xiaoyue Wang,Hurst,P.J.,Lewis,S.H..A 12-bit 20-Msample/s pipelined analog-to-digital converter with nested digital background calibration [J].IEEE Journal of Solid-State Circuits,Oct.2004,39:1799-1808. 8

高精度、低功耗流水线型模数转换器的研究与设计 8 [59] Katsufumi Nakamura, Masao Hotta, L. Richard Carley, and David J. Allstot. An 85 mW, 10b, 40 Msample/s CMOS parallel-pipelined ADC [J]. IEEE Journal of Solid-State Circuits, March 1995, 30: 173 – 183. [60] David William Cline. Noise, Speed, and Power Trade-offs in Pipelined Analog to Digital Converters[D]. Ph.D thesis, UC, Berkeley 1995. [61] Paul C. Yu and Hae-Seung Lee. A 2.5V 12b 5Msample/s pipelined CMOS ADC [J]. IEEE International Solid-State Circuits Conference, February 1996, XXXIX: 314 – 315. [62] Hui Pan, Masahiro Segami, Michael Choi, Jing Cao, Fumitoshi Hatori, and Asad Abidi. A 3.3V, 12b, 50Msample/s A/D converter in 0.6μm CMOS with over 80dB SFDR [J]. IEEE International Solid-State Circuits Conference, February 2000, XLIII: 40 – 41. [63] Klaas Bult and Aaron Buchwald. An embedded 240-mW 10-b 50-MS/s CMOS ADC in 1-mm2 [J]. IEEE Journal of Solid-State Circuits, December 1997, 32: 1887-1895. [64] Andrew M. Abo and Paul R. Gray. A 1.5-V, 10-bit, 14.3-MS/s CMOS pipeline analog-to-digital converter [J]. IEEE Journal of Solid-State Circuits, May 1999, 34: 599 – 606. [65] Lauri Sumanen, Mikko Waltari, and Kari A. I. Halonen. A 10-bit 200-MS/s CMOS parallel pipeline A/D converter [J]. IEEE Journal of Solid-State Circuits, July 2001, 36: 1048 – 1055. [66] Jong-Bum Park, Sang-Min Yoo, Se-Won Kim, Young-Jae Cho, Seung-Hoon. A 10-b 150-MSample/s 1.8-V 123-mW CMOS A/D converter with 400-MHz input bandwidth [J]. IEEE Journal of Solid-State Circuits, Aug. 2004, 39: 1335 – 1337. [67] Jipeng Li, Un-Ku Moon. A 1.8-V 67-mW 10-bit 100-MS/s pipelined ADC using time-shifted CDS technique [J]. IEEE Journal of Solid-State Circuits, Sept. 2004, 39: 1468 – 1476. [68] Xiaoyue Wang, Hurst, P.J., Lewis, S.H.. A 12-bit 20-Msample/s pipelined analog-to-digital converter with nested digital background calibration [J]. IEEE Journal of Solid-State Circuits, Oct. 2004, 39: 1799- 1808

第二章模数转换器概述 第二章模数转换器概述 本章首先介绍了模数转换器的基本原理。然后,给出评价模数转换器性能各 个指标参数的说明和计算方法,分析了模数转换器的测试原理和方法。最后,对 常见的各种模数转换器类型进行了简单的介绍和对比。 2.1理想的模数转换器 一个理想的模数转换器对信号的处理包括两个过程:一个是定时,一个是定 量,如图2.1所示。定时的工作一般被称为采样保持,此操作将输入的模拟信 号,以一定的时间间隔进行采集,并把采集好的信号保持一定的时间,供后续定 量处理:而定量的操作通常是由与一个己知的量进行比较来完成,实现的方法可 以是电压比较、电流比较、电荷比较以及时间比较等等。 01110101 10010100 00110100 01001001 S/H Quantization 图2.1模数转换器的功能 分辨率(Resolution)是衡量一个模数转换器进行定量操作的能力,以比特位 (bit)来表示,一个N-bit的ADC,具有可以分辨输入信号变化为1LSB(Least Significant Bit)的能力,其中1LSB=VFs2N,VFs为满幅输入信号。图2.2就是 一个理想3-bt模数转换器的量化特性,输入信号以横坐标表示,而数字输出以 二进制的形式用纵坐标表示。可以看到,输入信号每变化一个LSB,会使得数 字输出码改变一位,因此LSB也被称为量化步长,表示在这个步长内所有的模 拟输入信号都对应同一个数字输出。 9

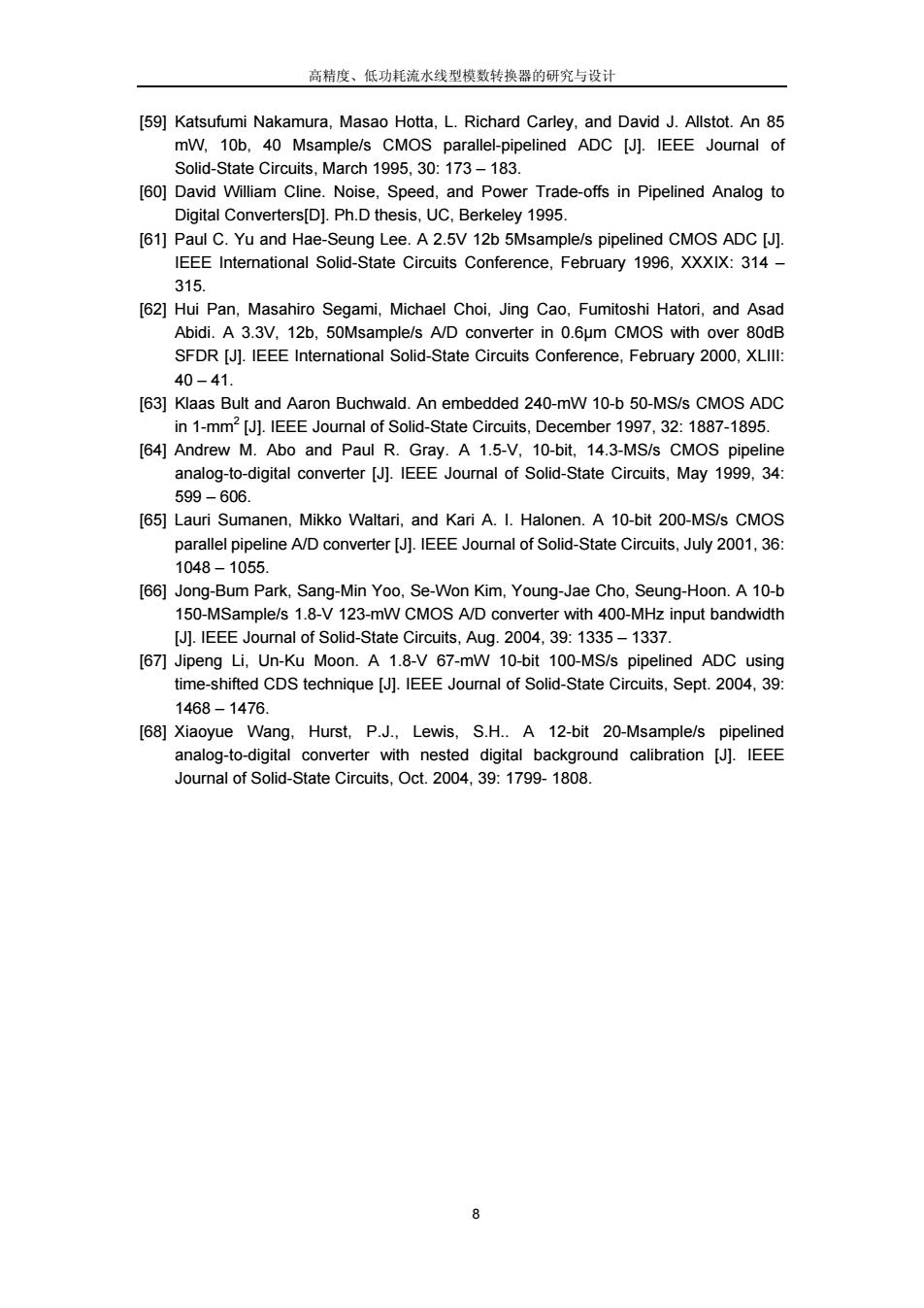

第二章 模数转换器概述 9 第二章 模数转换器概述 本章首先介绍了模数转换器的基本原理。然后,给出评价模数转换器性能各 个指标参数的说明和计算方法,分析了模数转换器的测试原理和方法。最后,对 常见的各种模数转换器类型进行了简单的介绍和对比。 2.1 理想的模数转换器 一个理想的模数转换器对信号的处理包括两个过程:一个是定时,一个是定 量,如图 2.1 所示。定时的工作一般被称为采样保持,此操作将输入的模拟信 号,以一定的时间间隔进行采集,并把采集好的信号保持一定的时间,供后续定 量处理;而定量的操作通常是由与一个已知的量进行比较来完成,实现的方法可 以是电压比较、电流比较、电荷比较以及时间比较等等。 图 2.1 模数转换器的功能 分辨率(Resolution)是衡量一个模数转换器进行定量操作的能力,以比特位 (bit)来表示,一个 N-bit 的 ADC,具有可以分辨输入信号变化为 1LSB(Least Significant Bit)的能力,其中 1 LSB=VFS/2N,VFS为满幅输入信号。图 2.2 就是 一个理想 3-bit 模数转换器的量化特性,输入信号以横坐标表示,而数字输出以 二进制的形式用纵坐标表示。可以看到,输入信号每变化一个 LSB,会使得数 字输出码改变一位,因此 LSB 也被称为量化步长,表示在这个步长内所有的模 拟输入信号都对应同一个数字输出

高精度、低功耗流水线型模数转换器的研究与设计 Dout 111 110 LSB 101 100 011 010 001 000, 0 FS/2 FS 图2.2理想3 bit ADC量化特性 2.2模数转换器相关指标和参数 在实际电路中,由于各种非理想因素的存在,导致了各种各样的误差,因此 不可能设计出完全理想的模数转换器。而且不同的应用领域对模数转换器有着不 同的要求,在设计和应用模数转换器之前首先需要做的就是了解衡量模数转换器 性能效率等规格的指标和参数,使得设计的模数转换器的各项性能可以满足如数 字视频和音频等应用的数字信号处理的系统需求。 2.2.1静态参数 (a积分非线性和微分非线性 积分非线性(Integral Nonlinearity,INL)是传输函数偏离理想直线的一种量 度标准,而微分非线性(Differential Nonlinearity,DNL)则是各码偏离理想值的步 长偏差,通常在评价模数转换器性能时则取其绝对值的最大值,以LSB为单位。 如图23所示,虚折线为理想量化曲线,实折线为非理想量化曲线。 INL与DNL的关系为 NL=DNL (2.1) i=1 10

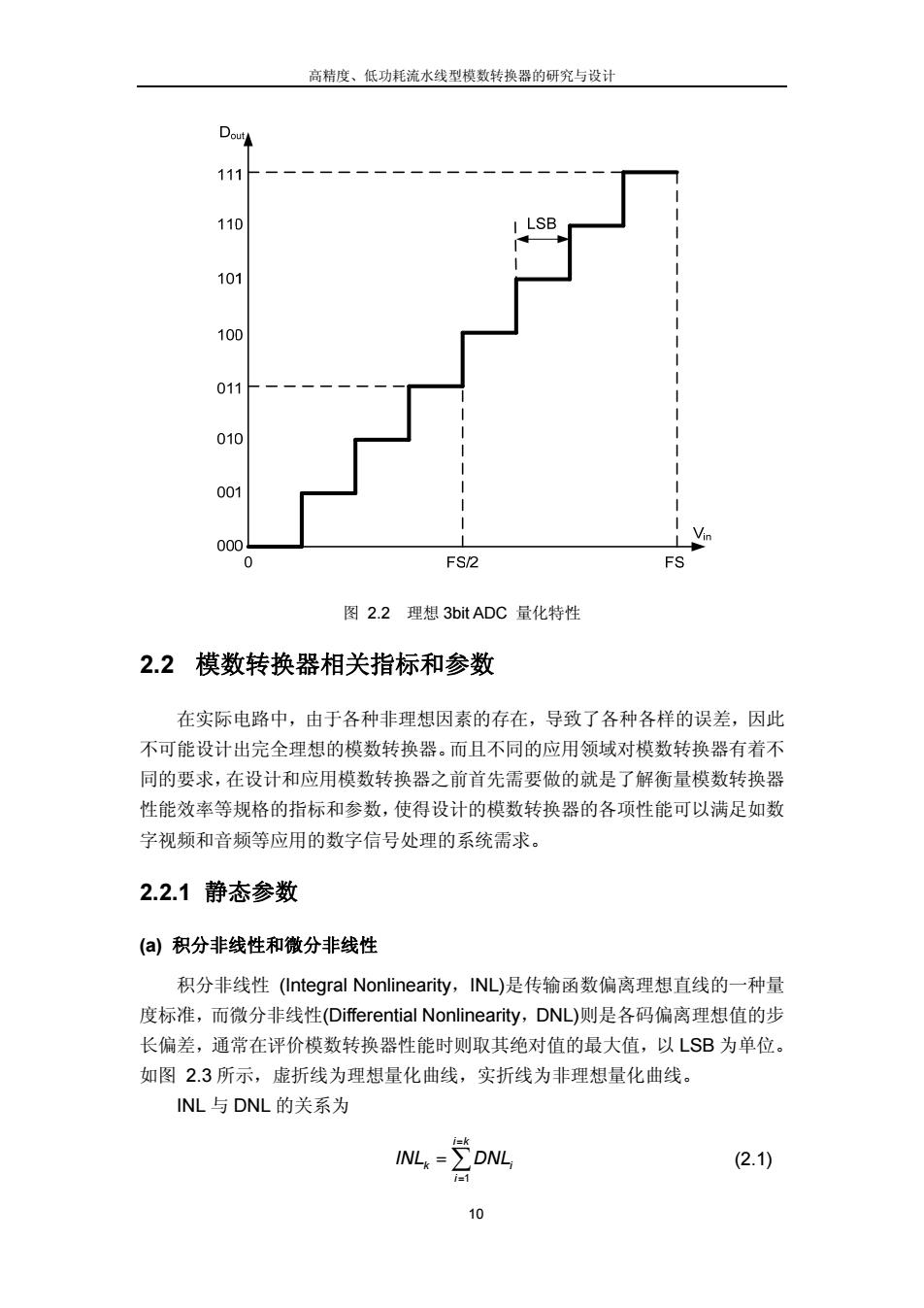

高精度、低功耗流水线型模数转换器的研究与设计 10 图 2.2 理想 3bit ADC 量化特性 2.2 模数转换器相关指标和参数 在实际电路中,由于各种非理想因素的存在,导致了各种各样的误差,因此 不可能设计出完全理想的模数转换器。而且不同的应用领域对模数转换器有着不 同的要求,在设计和应用模数转换器之前首先需要做的就是了解衡量模数转换器 性能效率等规格的指标和参数,使得设计的模数转换器的各项性能可以满足如数 字视频和音频等应用的数字信号处理的系统需求。 2.2.1 静态参数 (a) 积分非线性和微分非线性 积分非线性 (Integral Nonlinearity,INL)是传输函数偏离理想直线的一种量 度标准,而微分非线性(Differential Nonlinearity,DNL)则是各码偏离理想值的步 长偏差,通常在评价模数转换器性能时则取其绝对值的最大值,以 LSB 为单位。 如图 2.3 所示,虚折线为理想量化曲线,实折线为非理想量化曲线。 INL 与 DNL 的关系为 1 i k k i i INL DNL (2.1)

第二章模数转换器概述 111 0.7LSB (INL=0.7LSB) 110 101 100 2LSB 011 (DNL=1LSB) 010 001 000 0 FS/2 图2.33 bit ADC非线性特性 (b)单调性和失码 模数转换器的单调性是指在增大(或减小)输入值时,输出代码总是保持恒定 或增加(恒定或减小)。若输入值从一定值提高到另一值时,输出代码反而降低, 则系统就不是单调的。在应用中与实际的系统中时,系统会错误地认为己通过目 标点,并随即开始回转,而且系统会始终保持局部极小值,并且不可能到达所需 的目标点。 而失码则表示模数转换器的输出永远不能取得某一个或几个数字码,对于一 些系统(比如闭环控制系统正在搜索某个位置)来说,这些误差可能是灾难性的。 在失码的情形下,该系统将会无休止地一直搜索某个点。对模数转换器通常都会 要求单调且没有失码,因此DNL需要小于0.5LSB。 2.2.2动态参数 动态参数是指在频域中测量得到的参数。通常要得到动态参数需要在频域中 通过对测试输出的数字码进行快速傅立叶变换(FFT)来测量和计算。衡量动态参 数的主要指标有信噪比、信号与噪声谐波比、总谐波失真、无杂散动态范围和有 效位。 11

第二章 模数转换器概述 11 图 2.3 3bit ADC 非线性特性 (b) 单调性和失码 模数转换器的单调性是指在增大(或减小)输入值时,输出代码总是保持恒定 或增加(恒定或减小)。若输入值从一定值提高到另一值时,输出代码反而降低, 则系统就不是单调的。在应用中与实际的系统中时,系统会错误地认为已通过目 标点,并随即开始回转,而且系统会始终保持局部极小值,并且不可能到达所需 的目标点。 而失码则表示模数转换器的输出永远不能取得某一个或几个数字码,对于一 些系统(比如闭环控制系统正在搜索某个位置)来说,这些误差可能是灾难性的。 在失码的情形下,该系统将会无休止地一直搜索某个点。对模数转换器通常都会 要求单调且没有失码,因此 DNL 需要小于 0.5 LSB。 2.2.2 动态参数 动态参数是指在频域中测量得到的参数。通常要得到动态参数需要在频域中 通过对测试输出的数字码进行快速傅立叶变换(FFT)来测量和计算。衡量动态参 数的主要指标有信噪比、信号与噪声谐波比、总谐波失真、无杂散动态范围和有 效位

高精度、低功耗流水线型模数转换器的研究与设计 (a信噪比(Signal-to-Noise Ratio,SNR) SNR是ADC输出端信号能量与总噪声的能量之比,有 SNR =10lg Signal Power Total Noise Power (2.2) 由于量化存在一定的分辨率,所以SNR存在一个上限,为信号功率与量化噪声 的比值,其中量化噪声(ms)为 A.Irms]=Ase=AneE √122Wx√12 (2.3) 其中N为ADC分辨率。 根据上式,可以得到模数转换器SNR的上限为 SNRmax =101g AREE/212 AREE/2N 12 20g2 (2.4) =6.02N+1.76(dB) 以10位模数转换器为例,其所能达到的最高SNR为61.96dB。 (b)信号与噪声谐波比(Signa-to-Noise and Distortion Ratio,SINAD) SINAD(也写作SNDR)是ADC输出端信号功率与噪声、谐波功率和之比。 SNAD也就是信号能量和其余所有非信号能量的功率之比,因此是衡量一个 ADC精度最重要的指标。 SINAD =10lg Signal Power (2.5) Noise Distortion Power (c)无杂散动态范围(Spurious-Free Dynamic Range,SFDR) SFDR是信号的能量与最大的谐波或者杂波能量的比值,有 SFDR=10lg Signal Power (2.6) Largest Spurious Power 可以看到,SFDR实际上表示的是ADC的动态范围。 (d)总谐波失真(Total Harmonic Distortion,THD) THD是指在ADC输出信号频谱中,总谐波能量与信号能量的比值。有 12

高精度、低功耗流水线型模数转换器的研究与设计 12 (a) 信噪比 (Signal-to-Noise Ratio,SNR) SNR 是 ADC 输出端信号能量与总噪声的能量之比,有 10lg Signal Power SNR Total Noise Power (2.2) 由于量化存在一定的分辨率,所以 SNR 存在一个上限,为信号功率与量化噪声 的比值,其中量化噪声(rms)为 [ ] 12 2 12 LSB REF N A A A rms (2.3) 其中 N 为 ADC 分辨率。 根据上式,可以得到模数转换器 SNR 的上限为 2 max 2 2 10lg 2 12 3 20lg(2 ) 2 6.02 1.76 ( ) REF N REF N A SNR A N dB (2.4) 以 10 位模数转换器为例,其所能达到的最高 SNR 为 61.96 dB。 (b) 信号与噪声谐波比 (Signal-to-Noise and Distortion Ratio,SINAD) SINAD(也写作 SNDR)是 ADC 输出端信号功率与噪声、谐波功率和之比。 SINAD 也就是信号能量和其余所有非信号能量的功率之比,因此是衡量一个 ADC 精度最重要的指标。 10lg Signal Power SINAD Noise Distortion Power (2.5) (c) 无杂散动态范围 (Spurious-Free Dynamic Range,SFDR) SFDR 是信号的能量与最大的谐波或者杂波能量的比值,有 10lg arg Signal Power SFDR L est Spurious Power (2.6) 可以看到,SFDR 实际上表示的是 ADC 的动态范围。 (d) 总谐波失真 (Total Harmonic Distortion,THD) THD 是指在 ADC 输出信号频谱中,总谐波能量与信号能量的比值。有