K康还科技 7.1顺序语句 7.1.7WAIT语句 【例7-10】 (a)WAT_UNTL结构 (b)WAIT_ON结构 . LOOP Wait until enable ='1'; Wait on enable; EXIT WHEN enable ='1'; END LOOP;

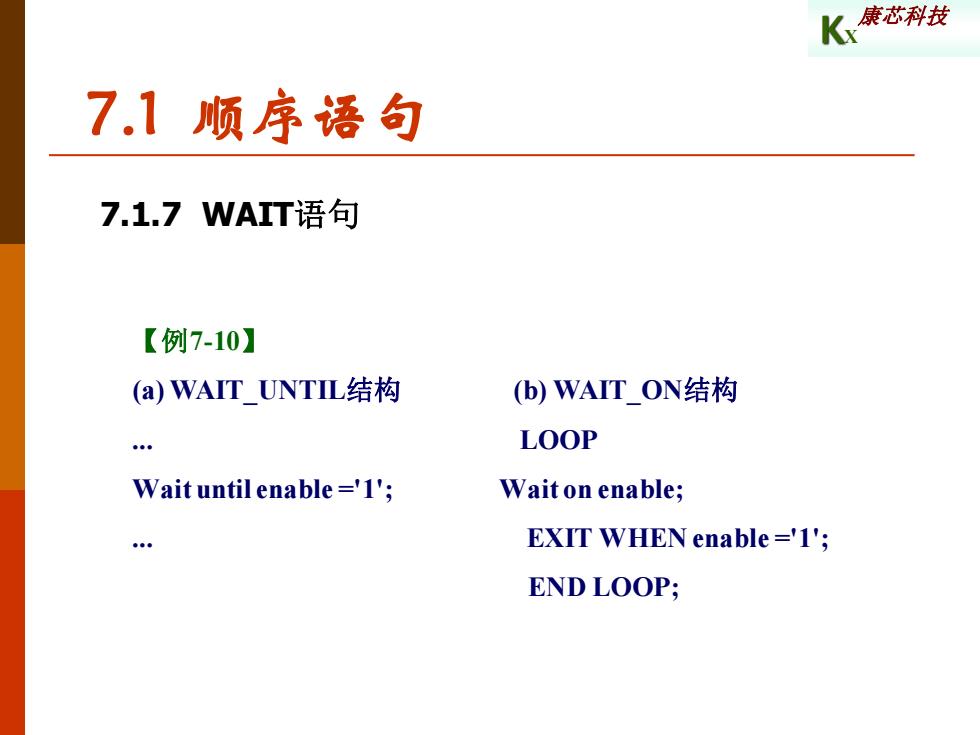

KX 康芯科技 7.1 顺序语句 7.1.7 WAIT语句 【例7-10】 (a) WAIT_UNTIL结构 (b) WAIT_ON结构 . LOOP Wait until enable ='1'; Wait on enable; . EXIT WHEN enable ='1'; END LOOP;

K能芯科骏 7.1顺序语句 7.1.7WAIT语句 WAIT UNTIL信号=Value; -(10 WAIT UNTIL信号'EVENT AND信号-Value; -(2) WAIT UNTIL NOT信号'STABLE AND信号=Value;-(③) WAIT UNTIL clock='1'; WAIT UNTIL rising_edge(clock); WAIT UNTILNOT clock'STABLE AND clock='1'; WAIT UNTIL clock='1'AND clock'EVENT;

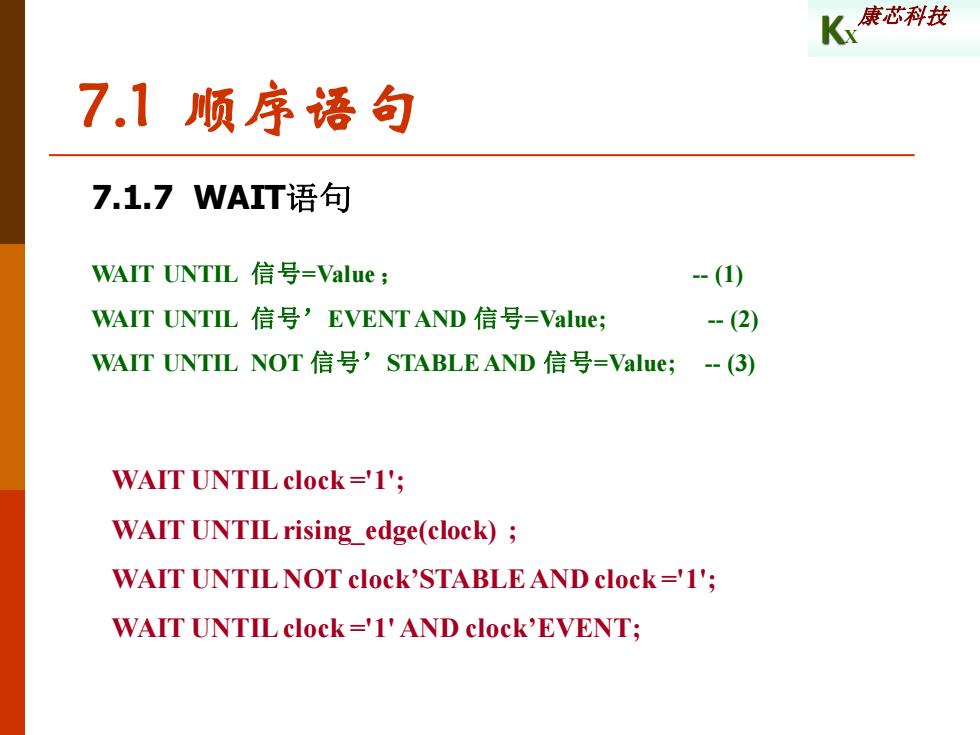

KX 康芯科技 7.1 顺序语句 7.1.7 WAIT语句 WAIT UNTIL 信号=Value ; - (1) WAIT UNTIL 信号’EVENTAND 信号=Value; - (2) WAIT UNTIL NOT 信号’STABLE AND 信号=Value; - (3) WAIT UNTILclock ='1'; WAIT UNTILrising_edge(clock) ; WAIT UNTIL NOT clock’STABLE AND clock ='1'; WAIT UNTILclock ='1' AND clock’EVENT;

K康科技 7.1顺序语句 7.1.7WAIT语句 【例7-11】 PROCESS BEGIN WAIT UNTIL clk ='1; ave <=a; WAIT UNTIL clk ='1; ave <=ave a; WAIT UNTIL clk =1; ave <ave +ai WAIT UNTIL clk ='1; ave <(ave a)/4 END PROCESS

KX 康芯科技 7.1 顺序语句 7.1.7 WAIT语句 【例7-11】 PROCESS BEGIN WAIT UNTIL clk ='1'; ave <= a; WAIT UNTIL clk ='1'; ave <= ave + a; WAIT UNTIL clk ='1'; ave <= ave + a; WAIT UNTIL clk ='1'; ave <= (ave + a)/4 ; END PROCESS ;

K康苏科数 7.1顺序语句 7.1.7 WAIT语句 【例7-12】 PROCESS BEGIN rst_loop:LOOP WAIT UNTIL clock='I'AND clock'EVENT;:-等待时钟信号 NEXT rst loop WHEN (rst='1'); -检测复位信号rst X<=a; -无复位信号,执行赋值操作 WAIT UNTIL clock='I'AND clock'EVENT;:-等待时钟信号 NEXT rst_loop When (rst='1'); -检测复位信号rst y<=b; -无复位信号,执行赋值操作 END LOOPrs

KX 康芯科技 7.1 顺序语句 7.1.7 WAIT语句 【例7-12】 PROCESS BEGIN rst_loop : LOOP WAIT UNTIL clock ='1' AND clock’EVENT; - 等待时钟信号 NEXT rst_loop WHEN (rst='1'); - 检测复位信号rst x <= a ; - 无复位信号,执行赋值操作 WAIT UNTIL clock ='1' AND clock’EVENT; - 等待时钟信号 NEXT rst_loop When (rst='1'); - 检测复位信号rst y <= b ; - 无复位信号,执行赋值操作 END LOOP rs

K康芯科技 【例7-13】 LIBRARY IEEE; USE IEEE.STD LOGIC 1164.ALL; ENTITY shifter IS PORT data IN STD LOGIC VECTOR (7 DOWNTO 0); shift left:IN STD LOGIC; shift right:IN STD LOGIC; clk:IN STD LOGIC; reset IN STD LOGIC; mode:IN STD LOGIC VECTOR (1 DOWNTO 0); qout BUFFER STD LOGIC VECTOR (7 DOWNTO 0)); END shifter; ARCHITECTURE behave OF shifter IS SIGNAL enable:STD LOGIC; BEGIN PROCESS BEGIN IT UNTIL(RISING EDGE(cIk));-等待时钟上升沿 IF (reset '1')THEN qout <="00000000"; ELSE CASE mode IS WHEN "01"=>qout<=shift right qout (7 DOWNTO 1); -右移 WHEN "10"=>qout<=gout(6 DOWNTO 0)shift left; -左移 WHEN "11"=>qout <data; - 并行加载 WHEN OTHERS =NULL; END CASE; END IF; END PROCESS; END behave;

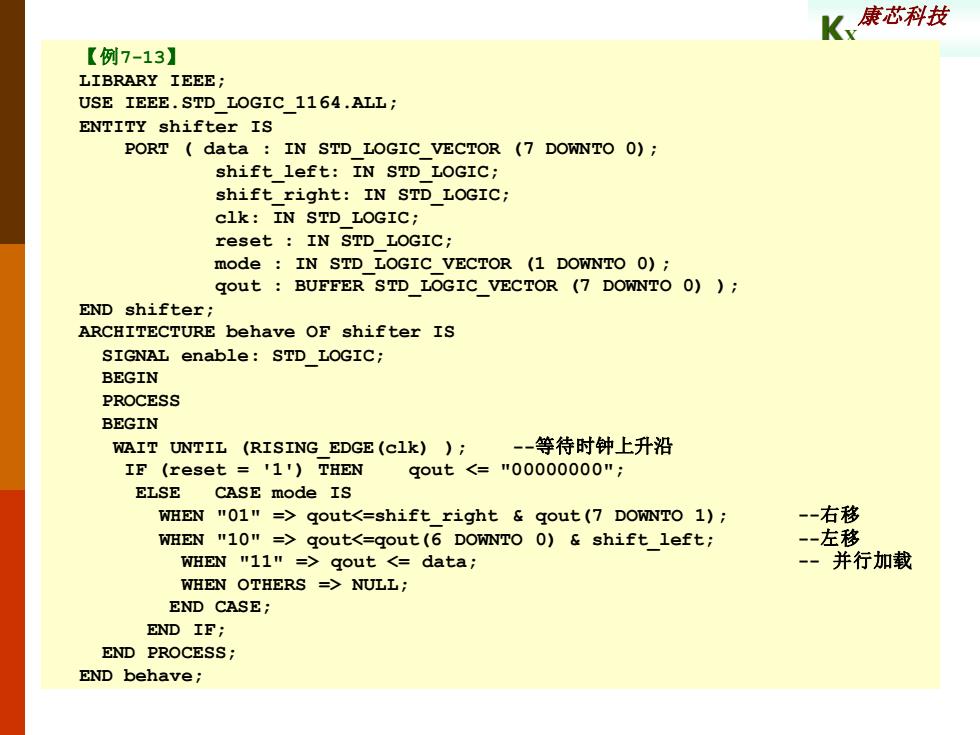

KX 康芯科技 【例7-13】 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY shifter IS PORT ( data : IN STD_LOGIC_VECTOR (7 DOWNTO 0); shift_left: IN STD_LOGIC; shift_right: IN STD_LOGIC; clk: IN STD_LOGIC; reset : IN STD_LOGIC; mode : IN STD_LOGIC_VECTOR (1 DOWNTO 0); qout : BUFFER STD_LOGIC_VECTOR (7 DOWNTO 0) ); END shifter; ARCHITECTURE behave OF shifter IS SIGNAL enable: STD_LOGIC; BEGIN PROCESS BEGIN WAIT UNTIL (RISING_EDGE(clk) ); -等待时钟上升沿 IF (reset = '1') THEN qout <= "00000000"; ELSE CASE mode IS WHEN "01" => qout<=shift_right & qout(7 DOWNTO 1); -右移 WHEN "10" => qout<=qout(6 DOWNTO 0) & shift_left; -左移 WHEN "11" => qout <= data; - 并行加载 WHEN OTHERS => NULL; END CASE; END IF; END PROCESS; END behave;