以康芯科技 【例8-4】 LIBRARY IEEE; -程序包首 USE IEEE.std logic 1164.all USE IEEE.std logic arith.all PACKAGE STD LOGIC UNSIGNED is function+ (L STD LOGIC VECTOR R:INTEGER) return STD_LOGIC _VECTOR function "+(L INTEGER;R STD LOGIC VECTOR) return STD LOGIC VECTOR function "+(L STD LOGIC VECTOR R STD LOGIC return STD LOGIC VECTOR function SHR (ARG STD LOGIC VECTOR COUNT STD LOGIC VECTOR return STD LOGIC VECTOR end STD LOGIC UNSIGNED LIBRARY IEEE; - 程序包体 use IEEE.std logic 1164.all use IEEE.std logic arith.all package body STD LOGIC UNSIGNED is function maximum (L,R INTEGER)return INTEGER is begin if L>R then return L; else return R; end if; end; function "+"(L:STD LOGIC VECTOR R INTEGER) return STD LOGIC VECTOR is Variable result STD LOGIC VECTOR (L'range); Begin result :UNSIGNED(L)+R return std logic vector (result); end end STD_LOGIC_UNSIGNED

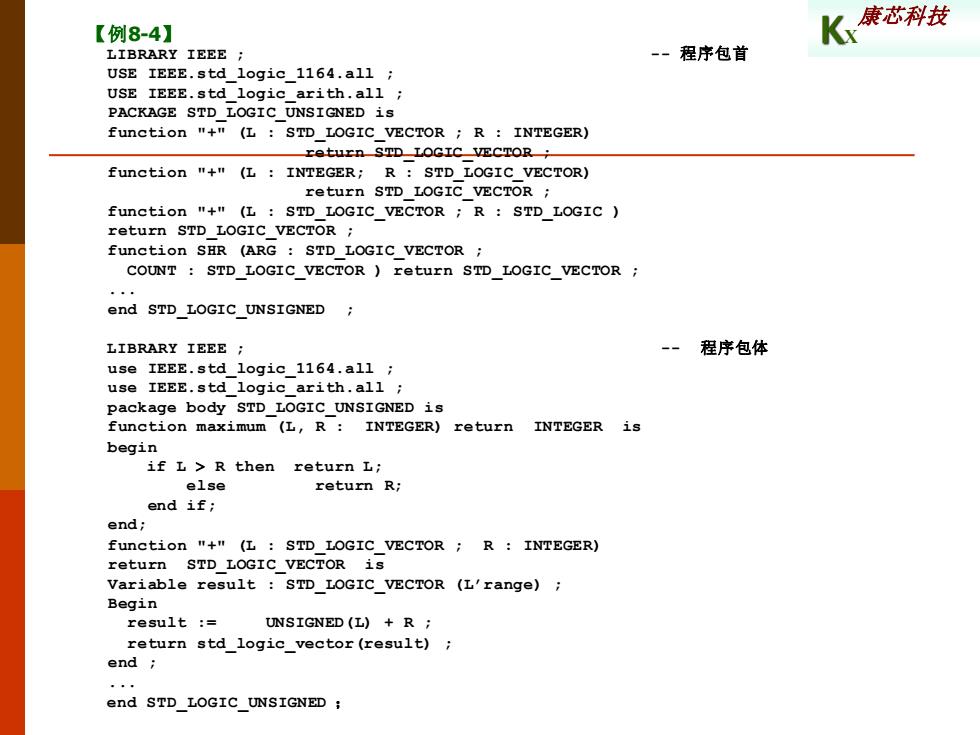

KX 康芯科技 【例8-4】 LIBRARY IEEE ; - 程序包首 USE IEEE.std_logic_1164.all ; USE IEEE.std_logic_arith.all ; PACKAGE STD_LOGIC_UNSIGNED is function "+" (L : STD_LOGIC_VECTOR ; R : INTEGER) return STD_LOGIC_VECTOR ; function "+" (L : INTEGER; R : STD_LOGIC_VECTOR) return STD_LOGIC_VECTOR ; function "+" (L : STD_LOGIC_VECTOR ; R : STD_LOGIC ) return STD_LOGIC_VECTOR ; function SHR (ARG : STD_LOGIC_VECTOR ; COUNT : STD_LOGIC_VECTOR ) return STD_LOGIC_VECTOR ; . end STD_LOGIC_UNSIGNED ; LIBRARY IEEE ; - 程序包体 use IEEE.std_logic_1164.all ; use IEEE.std_logic_arith.all ; package body STD_LOGIC_UNSIGNED is function maximum (L, R : INTEGER) return INTEGER is begin if L R then return L; else return R; end if; end; function "+" (L : STD_LOGIC_VECTOR ; R : INTEGER) return STD_LOGIC_VECTOR is Variable result : STD_LOGIC_VECTOR (L’range) ; Begin result := UNSIGNED(L) + R ; return std_logic_vector(result) ; end ; . end STD_LOGIC_UNSIGNED ; KX 康芯科技

K康还科技 8.3VHDL子程序 8.3.3VHDL转换函数 表8-1IEEE库类型转换函数表 函数名 功能 程序包:STD_L0GIC_1164 to_stdlogicvector(A) 由bit_vector类型的A转换为std_logic_.vector to_bitvector(A) 由std_logic_vector转换为bit_vector to_stdlogic(A) 由bit转换成std_logic to_bit(A) 由std_logic转换成bit 程序包:STD_LOGIC_ARITH conv_std logic_vector(A,位长) 将整数integer转换成std_logic_vector类型,A是整数 conv_integer(A) 将std_logic_.vector转换成整数integer 程序包:STD_LOGIC_UNSIGNED conv_integer(A) 由std_logic_vector转换成integer

KX 康芯科技 8.3 VHDL子程序 8.3.3 VHDL转换函数 函数名 功能 程序包: STD_LOGIC_1164 to_stdlogicvector(A) 由bit_vector类型的A转换为std_logic_vector to_bitvector(A) 由std_logic _vector转换为bit_vector to_stdlogic (A) 由bit转换成std_logic to_bit(A) 由std_logic转换成bit 程序包: STD_LOGIC_ARITH conv_std_logic_vector(A, 位长) 将整数integer转换成std_logic_vector类型,A是整数 conv_integer(A) 将std_logic_vector转换成整数integer 程序包: STD_LOGIC_UNSIGNED conv_integer(A) 由std_logic_vector转换成integer 表8-1 IEEE库类型转换函数表

K康芯科拉 8.3VHDL子程序 8.3.3VHDL转换函数 【例8-5】 LIBRARY IEEE; USE IEEE.std logic 1164.ALL; ENTITY exg IS PORT (a,b in bit vector(3 downto 0); q out std_logic_vector(3 downto 0)); end architecture rtl of exg is begin q<=to_stdlogicvector(a and b);-将位矢量数据类型转换成标准逻辑位矢量数据 end;

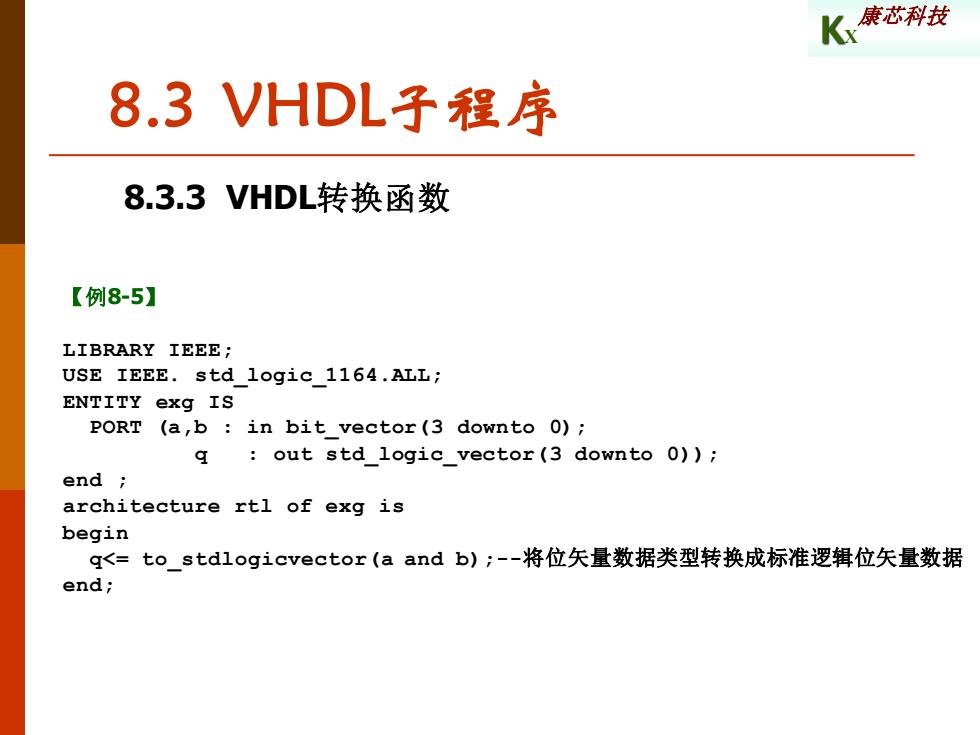

KX 康芯科技 8.3 VHDL子程序 8.3.3 VHDL转换函数 【例8-5】 LIBRARY IEEE; USE IEEE. std_logic_1164.ALL; ENTITY exg IS PORT (a,b : in bit_vector(3 downto 0); q : out std_logic_vector(3 downto 0)); end ; architecture rtl of exg is begin q<= to_stdlogicvector(a and b);-将位矢量数据类型转换成标准逻辑位矢量数据 end;

K康还科技 8.3VHDL子程序 8.3.3VHDL转换函数 【例8-6】 LIBRARY IEEE; USE IEEE.STD LOGIC 1164.ALL; USE IEEE.STD LOGIC ARITH.ALL;-注意使用了此程序包 ENTITY axamp Is PORT(a,b,c IN integer range 0 to 15 q OUT std logic vector(3 downto 0)); END; ARCHITECTURE bhv OF axamp IS BEGIN q <=conv std logic vector(a,4)when conv integer(c)=8 else conv_std logic vector(b,4); END;

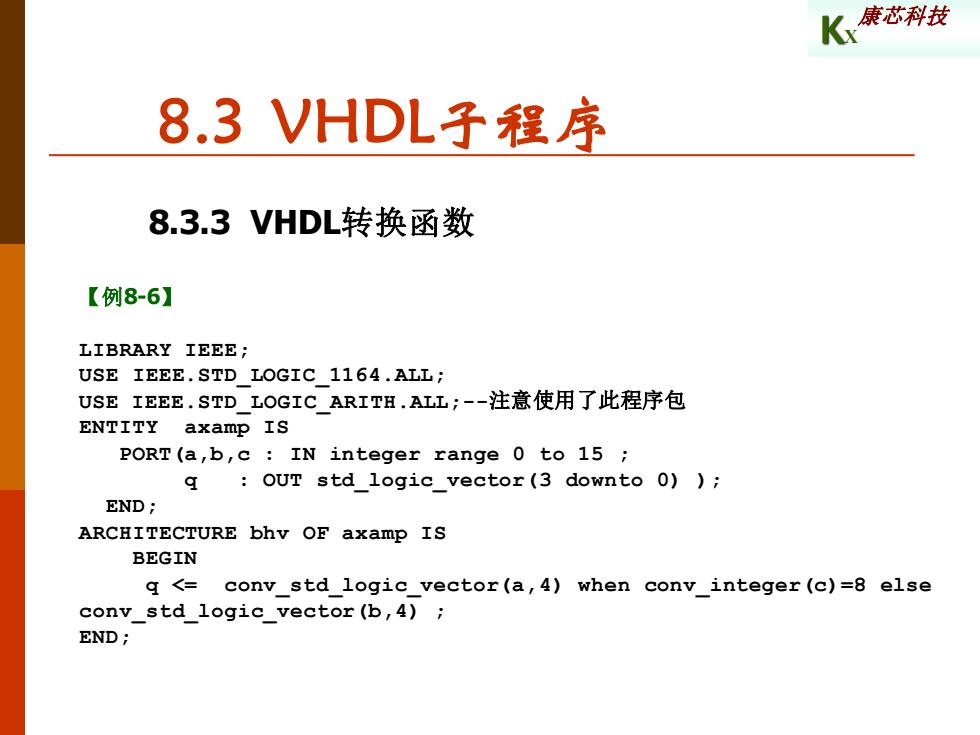

KX 康芯科技 8.3 VHDL子程序 8.3.3 VHDL转换函数 【例8-6】 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL;-注意使用了此程序包 ENTITY axamp IS PORT(a,b,c : IN integer range 0 to 15 ; q : OUT std_logic_vector(3 downto 0) ); END; ARCHITECTURE bhv OF axamp IS BEGIN q <= conv_std_logic_vector(a,4) when conv_integer(c)=8 else conv_std_logic_vector(b,4) ; END;

【例8-7】 LIBRARY IEEE; USE IEEE.STD LOGIC 1164.ALL; PACKAGE n_pack IS SUBTYPE nat Is Integer range 0 to 255; -定义一个Integerl的子类型 TYPE Bit8 Is array(7 downto0)OF std_logic;-定义一个数据类型 FUNCTION nat to Bit8 (s:nat)RETURN Bit8; End n pack; PACKAGE BODY n_pack Is FUNCTION nat to Bit8 (s:nat)RETURN Bit8 IS VARIABLE Din:Integer range 255 downto 0; VARIABLE Rut:Bit8; VARIABLE Rig:Integer =2**7; BEGIN Din :=s; FOR I in 7 downto 0 LOOP IF Din/Rig 1 THEN Rut(i):1';Din :Din-Rig; ELSE Rut (i):=0';END IF; Rig :Rig 2; END LOOP; RETURN Rut; END nat to Bit8; END n pack; LIBRARY IEEE; -一用户定义转换函数应用实例 USE IEEE.STD LOGIC 1164.ALL; USE WORK.n pack.ALL ENTITY axamp IS PORT(dat IN nat; -注意数据类型的定义 ou OUT Bit8); -一注意数据类型的定义 END: ARCHITECTURE bhv OF axamp IS BEGIN ou <nat to Bit8(dat); END;

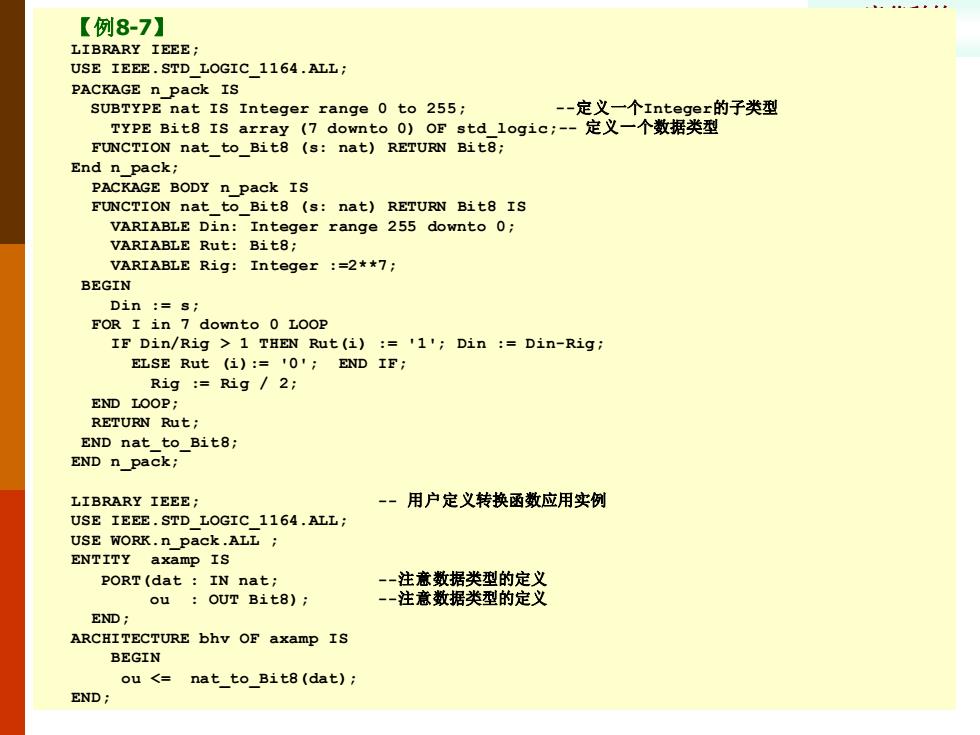

KX 康芯科技 【例8-7】 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; PACKAGE n_pack IS SUBTYPE nat IS Integer range 0 to 255; -定义一个Integer的子类型 TYPE Bit8 IS array (7 downto 0) OF std_logic;- 定义一个数据类型 FUNCTION nat_to_Bit8 (s: nat) RETURN Bit8; End n_pack; PACKAGE BODY n_pack IS FUNCTION nat_to_Bit8 (s: nat) RETURN Bit8 IS VARIABLE Din: Integer range 255 downto 0; VARIABLE Rut: Bit8; VARIABLE Rig: Integer :=2**7; BEGIN Din := s; FOR I in 7 downto 0 LOOP IF Din/Rig > 1 THEN Rut(i) := '1'; Din := Din-Rig; ELSE Rut (i):= '0'; END IF; Rig := Rig / 2; END LOOP; RETURN Rut; END nat_to_Bit8; END n_pack; LIBRARY IEEE; - 用户定义转换函数应用实例 USE IEEE.STD_LOGIC_1164.ALL; USE WORK.n_pack.ALL ; ENTITY axamp IS PORT(dat : IN nat; -注意数据类型的定义 ou : OUT Bit8); -注意数据类型的定义 END; ARCHITECTURE bhv OF axamp IS BEGIN ou <= nat_to_Bit8(dat); END;