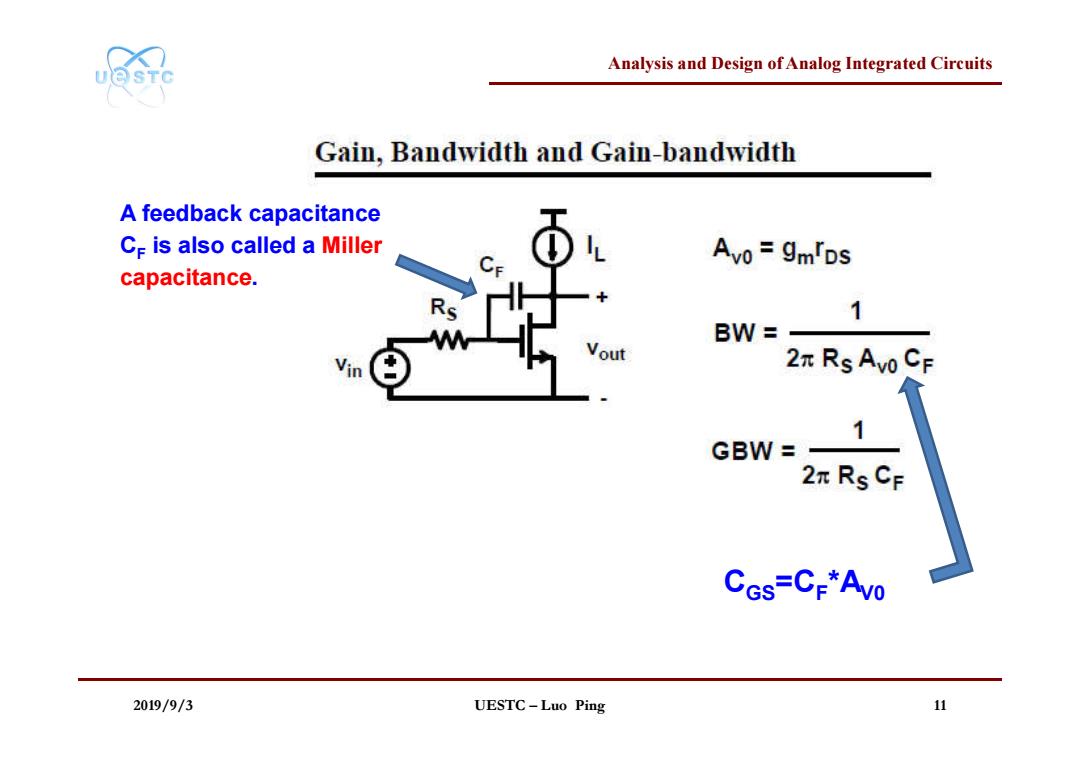

Analysis and Design of Analog Integrated Circuits UQSTC Gain,Bandwidth and Gain-bandwidth A feedback capacitance C is also called a Miller Avo=9mTDs capacitance. 1 BW= out 2元Rs Avo CF 1 GBW= 2πRsCF CGs=CF*Avo 2019/9/3 UESTC-Luo Ping 11

Analysis and Design of Analog Integrated Circuits 2019/9/3 UESTC – Luo Ping 11 CGS=CF*AV0 A feedback capacitance CF is also called a Miller capacitance

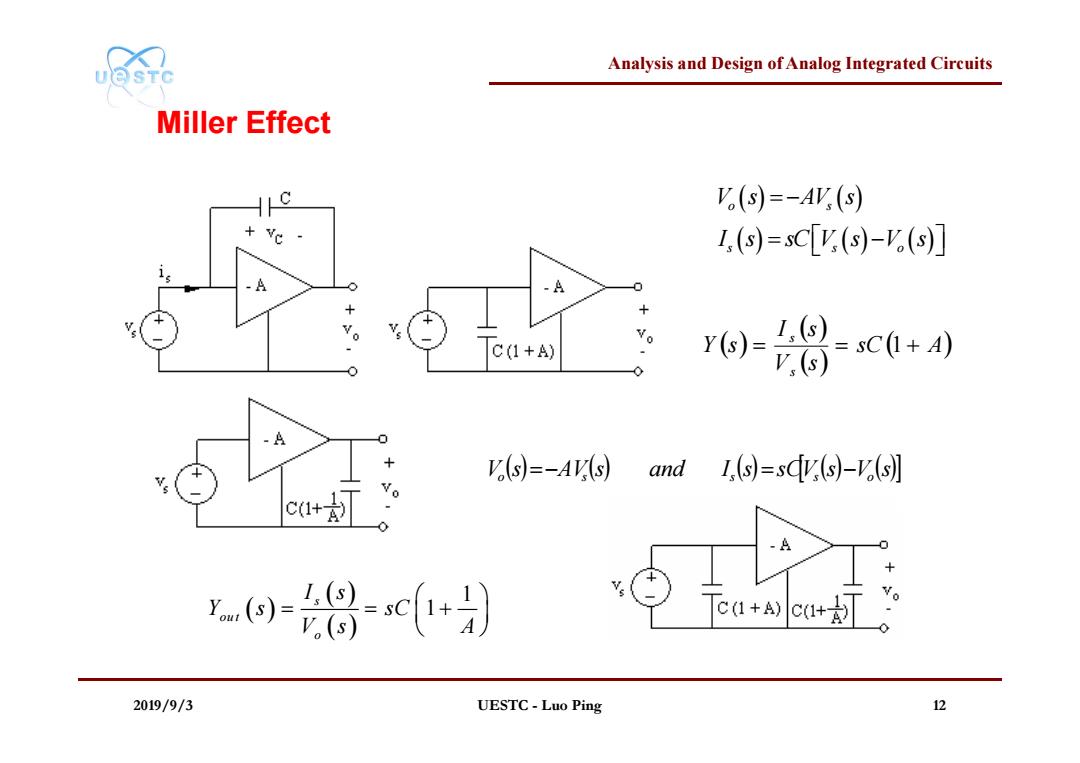

Analysis and Design of Analog Integrated Circuits UQSTC Miller Effect '(S)=-AY(s) I,(s)=sC[(s)-(] A 0 C(1+A) ro)8c0+ + V(s)=-4L(s) and I,(s)=sAVs(s)-V(s)] -A )8c+》 Ca+c+灯 2019/9/3 UESTC-Luo Ping 12

Analysis and Design of Analog Integrated Circuits 2019/9/3 12 Miller Effect o s s s o V s AV s I s sC V s V s sC A V s I s Y s s s 1 UESTC - Luo Ping V s AVs and I s sCV s V s o s s s o 1 1 s ou t o I s Y s sC V s A

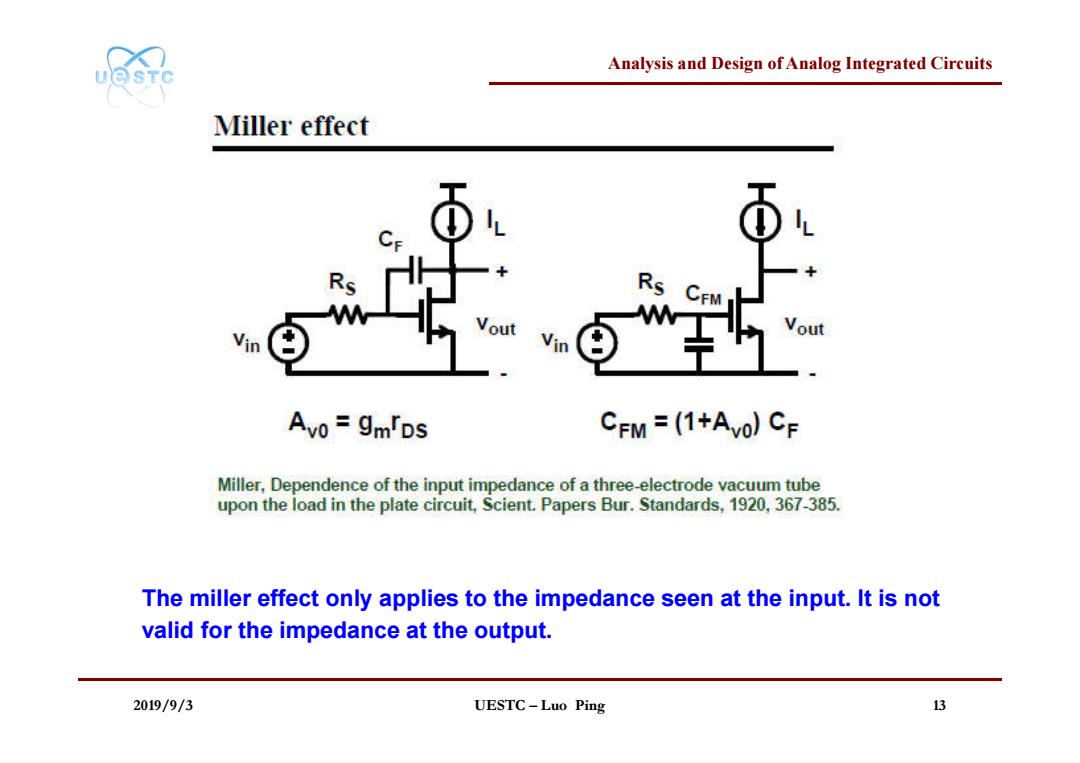

Analysis and Design of Analog Integrated Circuits UQSTC Miller effect Vout Vout Avo =9mTDs CFM=(1+Ayo)CE Miller,Dependence of the input impedance of a three-electrode vacuum tube upon the load in the plate circuit,Scient.Papers Bur.Standards,1920,367-385 The miller effect only applies to the impedance seen at the input.It is not valid for the impedance at the output. 2019/9/3 UESTC-Luo Ping 13

Analysis and Design of Analog Integrated Circuits 2019/9/3 UESTC – Luo Ping 13 The miller effect only applies to the impedance seen at the input. It is not valid for the impedance at the output

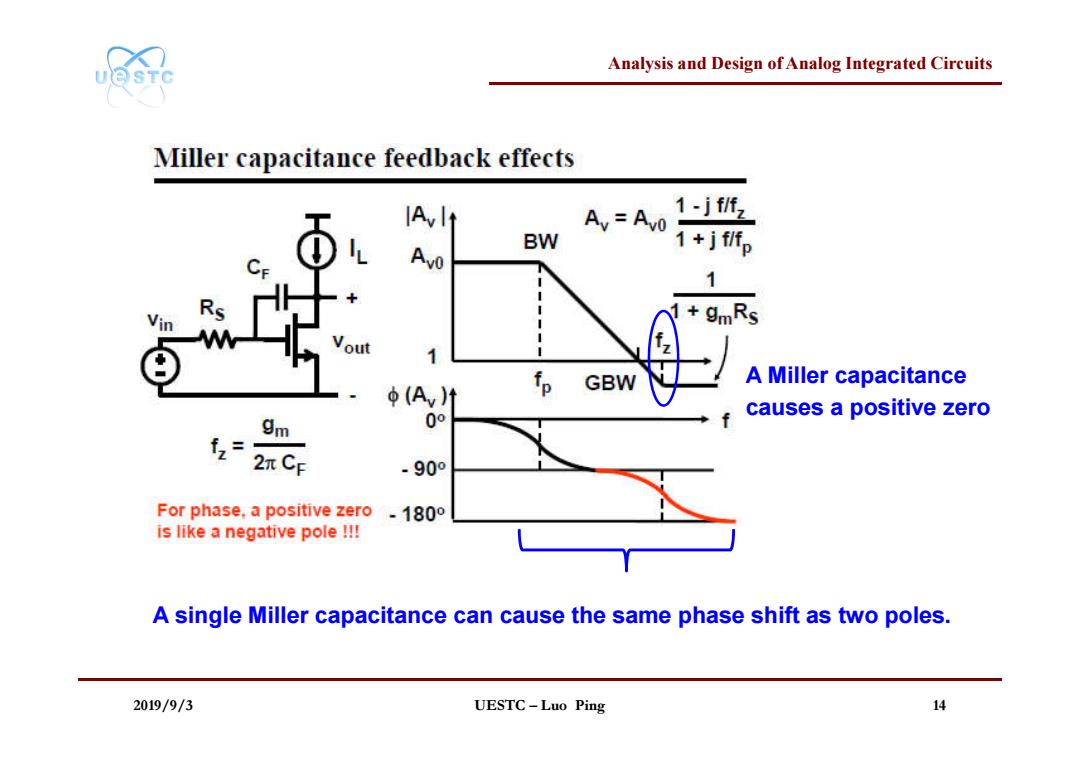

Analysis and Design of Analog Integrated Circuits UQSTC Miller capacitance feedback effects IAv It Ay=Av0 1-jf2 Av0 BW 1+jflfp 1 gmRs Vout 1 φ(Avf GBW A Miller capacitance 0° causes a positive zero 9m 2xCF -90° For phase,a positive zero -1800 is like a negative pole !! A single Miller capacitance can cause the same phase shift as two poles. 2019/9/3 UESTC-Luo Ping 14

Analysis and Design of Analog Integrated Circuits 2019/9/3 UESTC – Luo Ping 14 A Miller capacitance causes a positive zero A single Miller capacitance can cause the same phase shift as two poles

Analysis and Design of Analog Integrated Circuits U@STC Miller Effects in Frequency Response Vou =[(Vin-Vou)C1s-gmVin lras (1-SC)8 Yout A= out二一 gml 乳 Vin (sC's1+1) 祖 8m1V泳 /T1 6 There is a right-hand plane zero and a left-hand plane pole. 2019/9/3 UESTC-Luo Ping 15

Analysis and Design of Analog Integrated Circuits Miller Effects in Frequency Response There is a right-hand plane zero and a left-hand plane pole. 2019/9/3 15 1 1 1 [( ) ] out in out m in ds v v v C s g v r 1 1 1 1 1 1 (1 ) ( 1) m ds out m V in ds sC g r v g A v sC r UESTC - Luo Ping