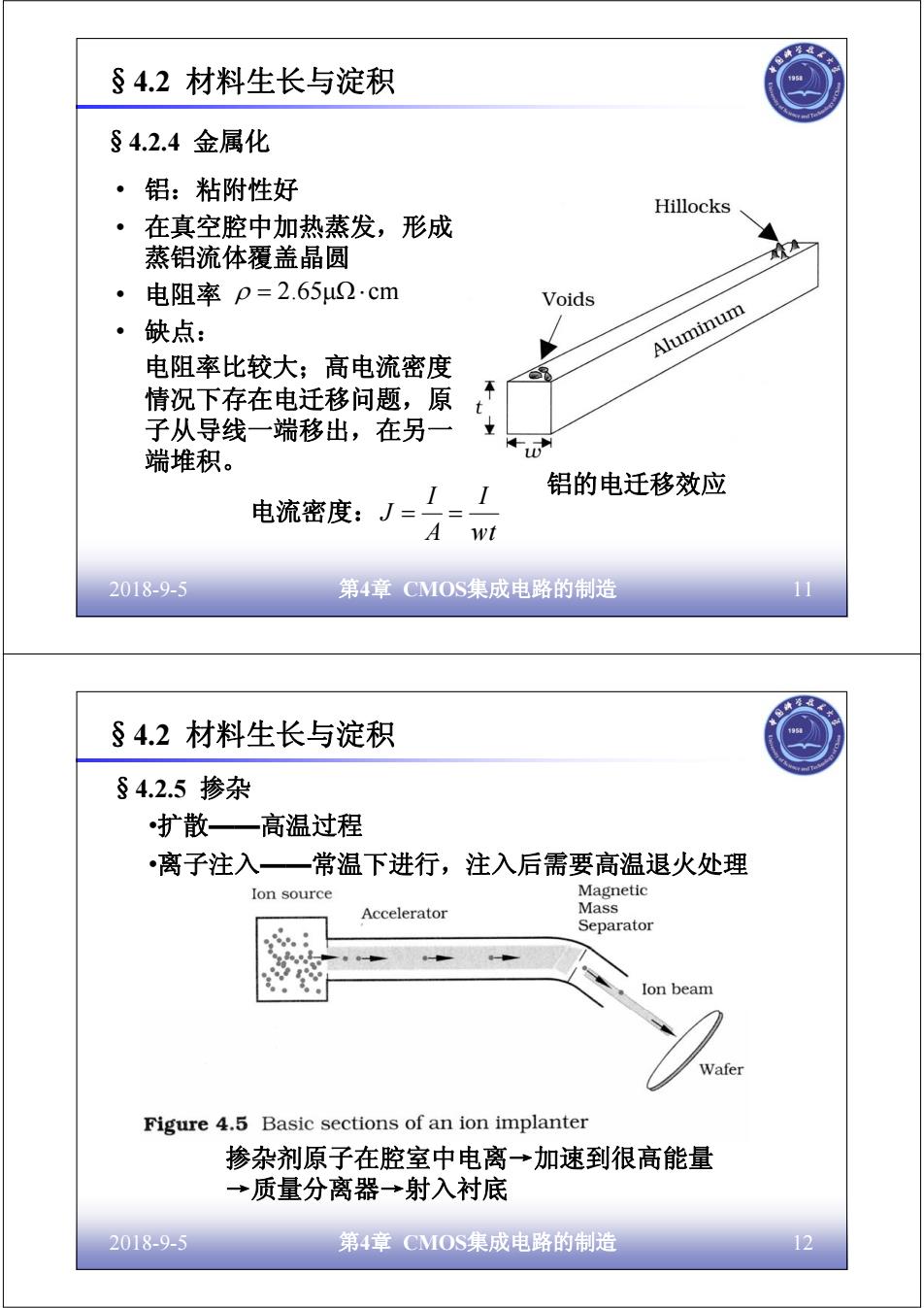

§4.2材料生长与淀积 §4.2.4金属化 ·铝:粘附性好 Hillocks ·在真空腔中加热蒸发,形成 蒸铝流体覆盖晶圆 ·电阻率p=2.65μ2cm Voids ·缺点: Aluminum 电阻率比较大;高电流密度 情况下存在电迁移问题,原 子从导线一端移出,在另 一 端堆积。 I 铝的电迁移效应 电流密度:J= A wt 2018-9-5 第4章CMOS集成电路的制造 §4.2材料生长与淀积 §4.2.5掺杂 扩散一高温过程 ·离子注入一常温下进行,注入后需要高温退火处理 Ion source Magnetic Accelerator Mass Separator Ion beam Wafer Figure 4.5 Basic sections of an ion implanter 掺杂剂原子在腔室中电离→加速到很高能量 →质量分离器→射入衬底 2018-9-5 第4章CMOS集成电路的制造 12

2018-9-5 第4章 CMOS集成电路的制造 11 §4.2 材料生长与淀积 §4.2.4 金属化 wt I A I 电流密度:J = = • 铝:粘附性好 • 在真空腔中加热蒸发,形成 蒸铝流体覆盖晶圆 • 电阻率 • 缺点: 电阻率比较大;高电流密度 情况下存在电迁移问题,原 子从导线一端移出,在另一 端堆积。 ρ = 2.65μΩ ⋅ cm 铝的电迁移效应 2018-9-5 第4章 CMOS集成电路的制造 12 §4.2 材料生长与淀积 §4.2.5 掺杂 •扩散——高温过程 •离子注入——常温下进行,注入后需要高温退火处理 掺杂剂原子在腔室中电离→加速到很高能量 →质量分离器→射入衬底

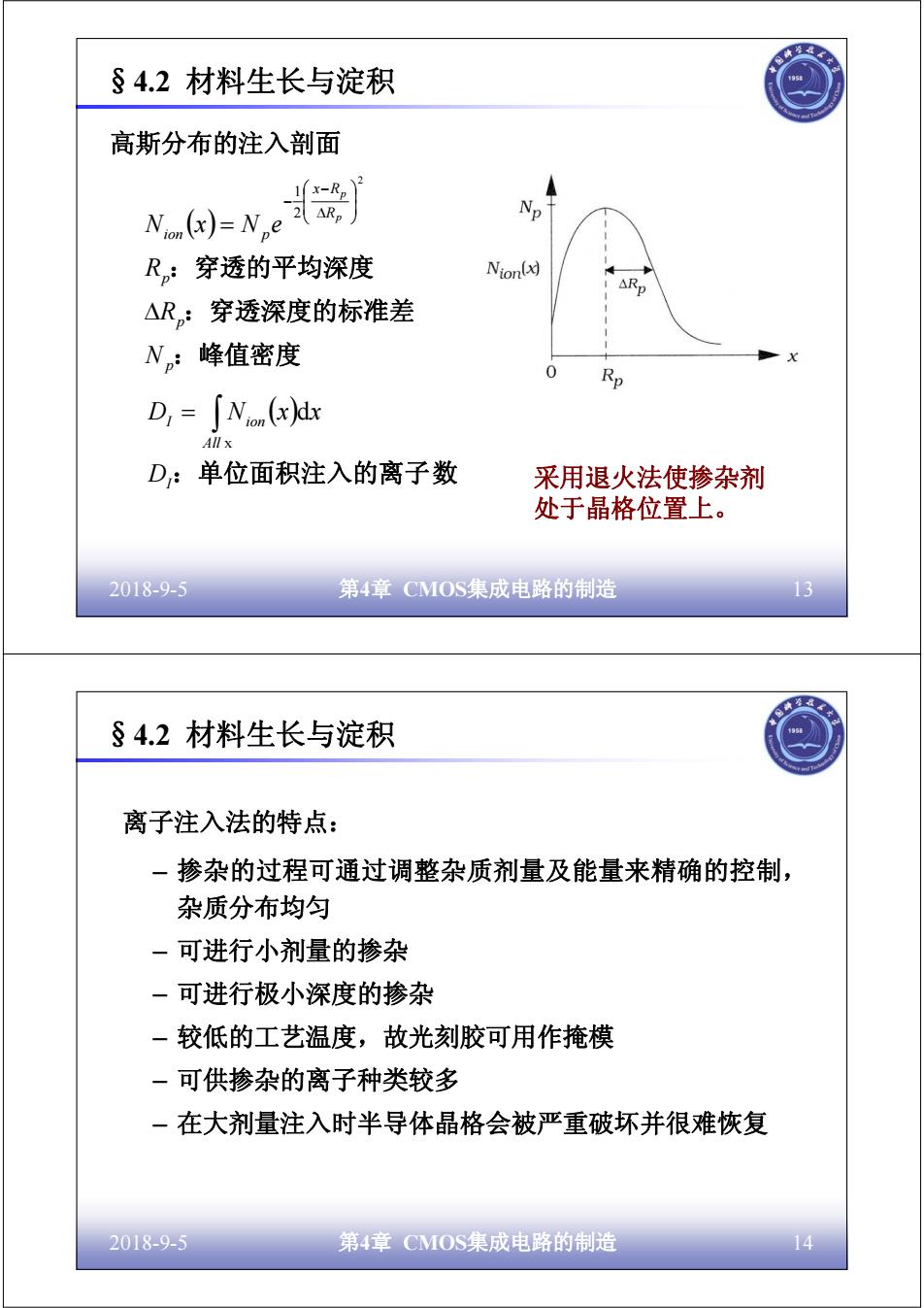

§4.2材料生长与淀积 高斯分布的注入剖面 -R2 No(x)=Ne 2△R。 Np R。:穿透的平均深度 Nion(x) ARp △R:穿透深度的标准差 N,:峰值密度 Rp D,=∫Na(xdx All x D 单位面积注入的离子数 采用退火法使掺杂剂 处于晶格位置上。 2018-9-5 第4章CMOS集成电路的制造 13 §4.2材料生长与淀积 离子注入法的特点: 一掺杂的过程可通过调整杂质剂量及能量来精确的控制, 杂质分布均匀 可进行小剂量的掺杂 一可进行极小深度的掺杂 一较低的工艺温度,故光刻胶可用作掩模 一可供掺杂的离子种类较多 一在大剂量注入时半导体晶格会被严重破坏并很难恢复 2018-9-5 第4章CMOS集成电路的制造 14

2018-9-5 第4章 CMOS集成电路的制造 13 §4.2 材料生长与淀积 采用退火法使掺杂剂 处于晶格位置上。 高斯分布的注入剖面 ( ) :峰值密度 :穿透深度的标准差 :穿透的平均深度 p p p R x R ion p N R R N x N e p p Δ = ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ Δ − − 2 2 1 ( ) I :单位面积注入的离子数 All I ion D D N x x ∫ = x d 2018-9-5 第4章 CMOS集成电路的制造 14 §4.2 材料生长与淀积 离子注入法的特点: – 掺杂的过程可通过调整杂质剂量及能量来精确的控制, 杂质分布均匀 – 可进行小剂量的掺杂 – 可进行极小深度的掺杂 – 较低的工艺温度,故光刻胶可用作掩模 – 可供掺杂的离子种类较多 – 在大剂量注入时半导体晶格会被严重破坏并很难恢复

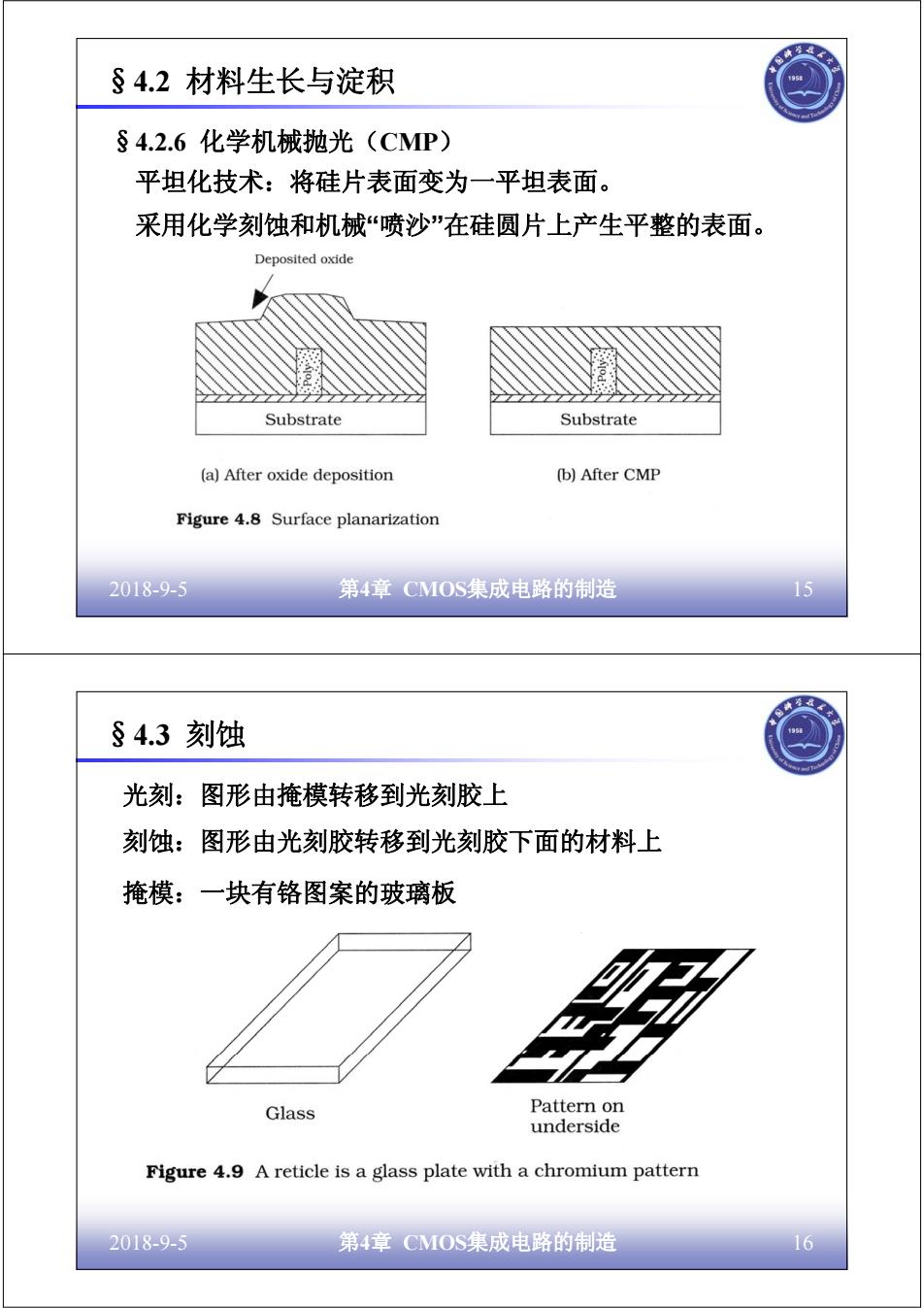

§4.2材料生长与淀积 §4.2.6化学机械抛光(CMP) 平坦化技术:将硅片表面变为一平坦表面。 采用化学刻蚀和机械“喷沙”在硅圆片上产生平整的表面。 Deposited oxide Substrate Substrate (a)After oxide deposition (b)After CMP Figure 4.8 Surface planarization 2018-9-5 第4章CMOS集成电路的制造 §4.3刻蚀 光刻:图形由掩模转移到光刻胶上 刻蚀:图形由光刻胶转移到光刻胶下面的材料上 掩模:一块有铬图案的玻璃板 Glass Pattern on underside Figure 4.9 A reticle is a glass plate with a chromium pattern 2018-9-5 第4章CMOS集成电路的制造 16

2018-9-5 第4章 CMOS集成电路的制造 15 §4.2 材料生长与淀积 §4.2.6 化学机械抛光(CMP) 采用化学刻蚀和机械“喷沙”在硅圆片上产生平整的表面。 平坦化技术:将硅片表面变为一平坦表面。 2018-9-5 第4章 CMOS集成电路的制造 16 §4.3 刻蚀 掩模:一块有铬图案的玻璃板 光刻:图形由掩模转移到光刻胶上 刻蚀:图形由光刻胶转移到光刻胶下面的材料上