8088处理器引脚 (9) 最小模式下的引线 INTR可屏蔽中断请求输入信号,高电平有效。CPU在每条 指令的最后一个周期采样该信号,以决定是否进入中断响 应周期。这个引脚上的中断请求信号可用软件屏蔽 ● TEST测试信号输入引脚,低电平有效。当CPU执行WAIT 指令时,每隔5个时钟周期对此引脚进行一次测试。若为 高电平,CPU则继续处于空转状态进行等待,直到引脚变 为低电平,CPU才结束等待状态,继续执行下一条指令 i Lin University China CpTE型CIENCE AND T厘CHNDOLOGY

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8088处理器引脚 (9) 最小模式下的引线 • INTR 可屏蔽中断请求输入信号,高电平有效。CPU在每条 指令的最后一个周期采样该信号,以决定是否进入中断响 应周期。这个引脚上的中断请求信号可用软件屏蔽 • 测试信号输入引脚,低电平有效。当CPU执行WAIT 指令时,每隔5个时钟周期对此引脚进行一次测试。若为 高电平,CPU则继续处于空转状态进行等待,直到引脚变 为低电平,CPU才结束等待状态,继续执行下一条指令 TEST

8088处理器引脚 (10) 最小模式下的引线 NMT非屏蔽中断请求输入信号,上升沿触发。这 个引脚上的中断请求信号不能用软件屏蔽,CPU 在当前指令执行结束后就进入中断过程 。 NTA中断响应信号输出,低电平有效,是CPU对 中断请求信号INTR的响应。在响应过程中,CPU 在该引脚连续送出两个负脉冲,可用作外部中断 源中断向量码的读选通信号 Ji Lin University China COMPUTER SCIENCE AND TECHNOLOGY

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8088处理器引脚 (10) 最小模式下的引线 • NMI 非屏蔽中断请求输入信号,上升沿触发。这 个引脚上的中断请求信号不能用软件屏蔽,CPU 在当前指令执行结束后就进入中断过程 • 中断响应信号输出,低电平有效,是CPU对 中断请求信号INTR的响应。在响应过程中,CPU 在该引脚连续送出两个负脉冲,可用作外部中断 源中断向量码的读选通信号 INTA

8088处理器引脚 (11) 最小模式下的引线 RESET系统复位输入信号,高电平有效。为使 CPU完成内部复位过程,该信号至少要在4个时钟 周期内保持有效。复位后CPU内部寄存器的状态 如表,当RESET.返回低电平时, CPU将重新启动 内部寄存器 内容 内部寄存器 内容 CS FFFFH P 0000H DS 0000H FLAGS 0000H SS 0000H 其余寄存器 0000H ES 0000H 指令队列 空 Ji Lin University China COMPUTE型SCIENCE AND T室CHNDLOG

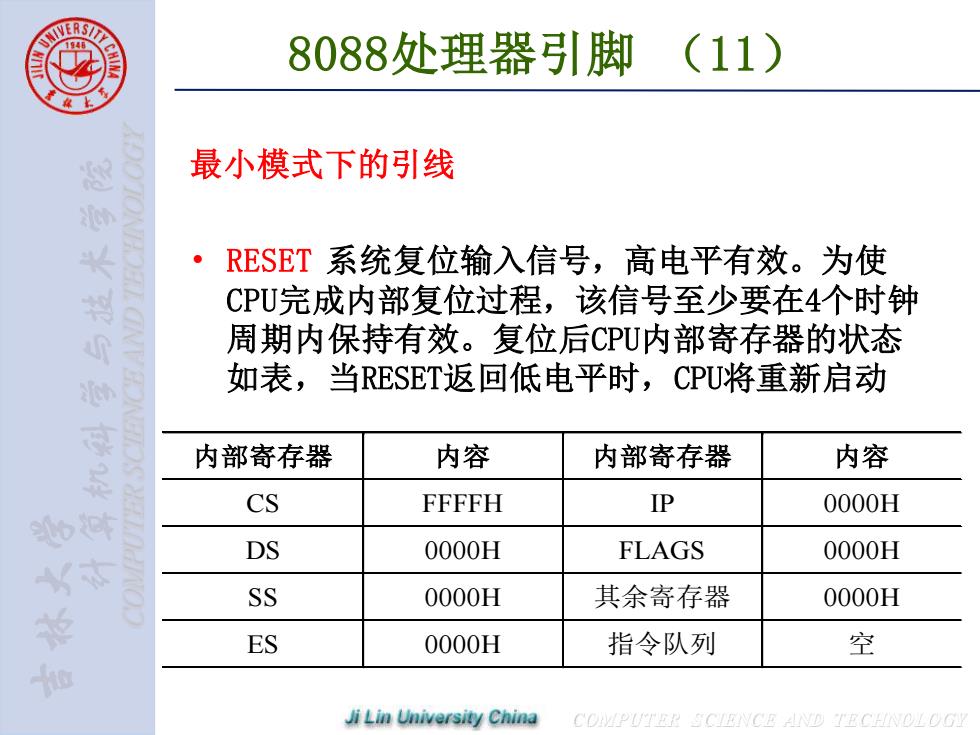

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8088处理器引脚 (11) 最小模式下的引线 • RESET 系统复位输入信号,高电平有效。为使 CPU完成内部复位过程,该信号至少要在4个时钟 周期内保持有效。复位后CPU内部寄存器的状态 如表,当RESET返回低电平时,CPU将重新启动 内部寄存器 内容 内部寄存器 内容 CS FFFFH IP 0000H DS 0000H FLAGS 0000H SS 0000H 其余寄存器 0000H ES 0000H 指令队列 空

8088处理器引脚 (12) 最小模式下的引线 H0LD总线保持请求信号输入,高电平有效。当 某一总线上主控设备要占用系统总线时,通过此 引脚向CPU提出请求 HLDA总线保持响应信号输出,高电平有效。这 是CPU对HOLD请求的响应信号,当CPU收到有效的 HOLD信号后,就会对其做出响应:一方面使CPU 的所有三态输出的地址信号、数据信号和相应的 控制信号变为高阻状态(浮动状态);同时还输 出一个有效的HLDA,表示处理器现在已放弃对总 线的控制。当CPU检测到HOLD信号变低后,就立 即使HLDA变低,同时恢复对总线的控制 Ji Lin University China COMPUTER SCIENCE AND TECHNOLOGY

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8088处理器引脚 (12) 最小模式下的引线 • HOLD 总线保持请求信号输入,高电平有效。当 某一总线上主控设备要占用系统总线时,通过此 引脚向CPU提出请求 • HLDA 总线保持响应信号输出,高电平有效。这 是CPU对HOLD请求的响应信号,当CPU收到有效的 HOLD信号后,就会对其做出响应:一方面使CPU 的所有三态输出的地址信号、数据信号和相应的 控制信号变为高阻状态(浮动状态);同时还输 出一个有效的HLDA,表示处理器现在已放弃对总 线的控制。当CPU检测到HOLD信号变低后,就立 即使HLDA变低,同时恢复对总线的控制

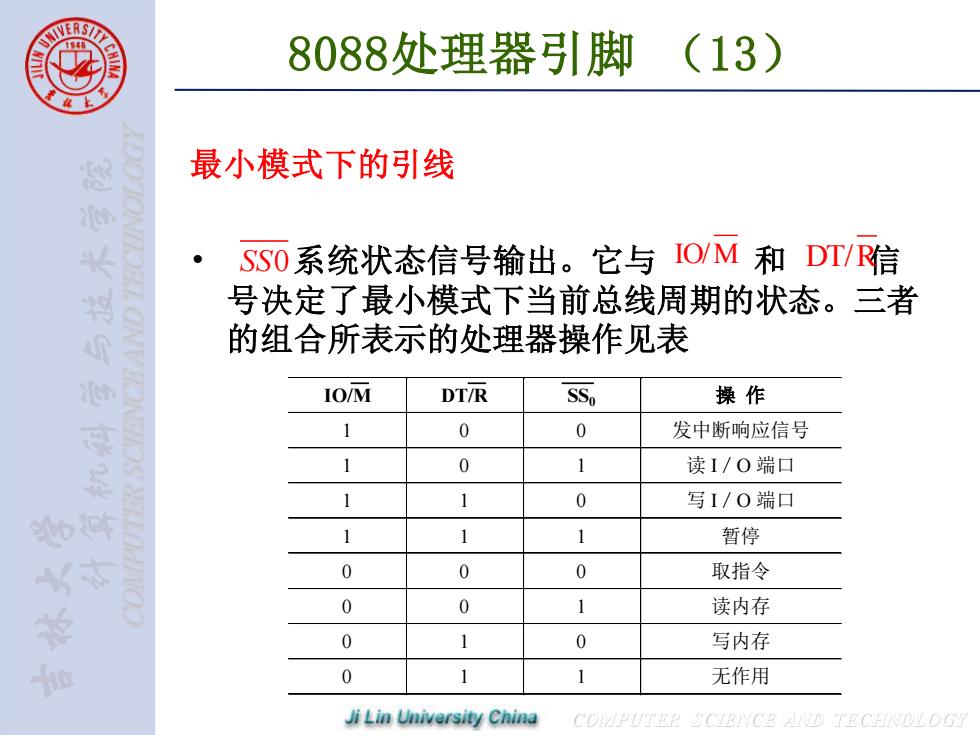

8088处理器引脚 (13) 最小模式下的引线 SSO系统状态信号输出。它与IO/M和DT/R信 号决定了最小模式下当前总线周期的状态。三者 的组合所表示的处理器操作见表 IO/M DT/R SSo 操作 1 0 0 发中断响应信号 1 0 1 读1/0端口 1 1 0 写1/0端口 1 1 1 暂停 0 0 0 取指令 0 0 1 读内存 0 1 0 写内存 0 1 1 无作用 JiLin University China CIENCE AND T里CG

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8088处理器引脚 (13) 最小模式下的引线 • 系统状态信号输出。它与 和 信 号决定了最小模式下当前总线周期的状态。三者 的组合所表示的处理器操作见表 SS0 IO/M DT/R IO/M DT/R SS0 操 作 1 0 0 发中断响应信号 1 0 1 读 I/O 端口 1 1 0 写 I/O 端口 1 1 1 暂停 0 0 0 取指令 0 0 1 读内存 0 1 0 写内存 0 1 1 无作用