8088处理器引脚 (14) 最小模式下的引线 CLK时钟信号输入引脚。8088的标准时钟频率为 4.77MHz,时钟的占空比为33% Vcc5V电源输入引脚 GND地线 Ji Lin University China COMPUTER SCIENCE AND TECHNOLOGY

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8088处理器引脚 (14) 最小模式下的引线 • CLK 时钟信号输入引脚。8088的标准时钟频率为 4.77MHz,时钟的占空比为33% • Vcc 5V电源输入引脚 • GND 地线

8088处理器引脚 (15) 最大模式下的引线 MN/MX-0) GND A14 ● 此时,除23引脚到 30引脚8个引脚外, A10 1234567 443938376 A A6/S A17/S4 A18/S A1/S 其他引线与最小模 54 SS HIGH As N/M区 式相同 AD, 89 AD AD 35213009 RD HOLD HLDA (RQ/GT。) AD WR (RQ/GT) AD IO/M (LOCK) AD, AD o NMI INTR 234567890 8732524321 DT/R S,) DEN ALE S0。 INTA (QSo) TEST (QS1) READY RESET Ji Lin University China COMPUTER SCIENCE山NDY室CHNOLOGY

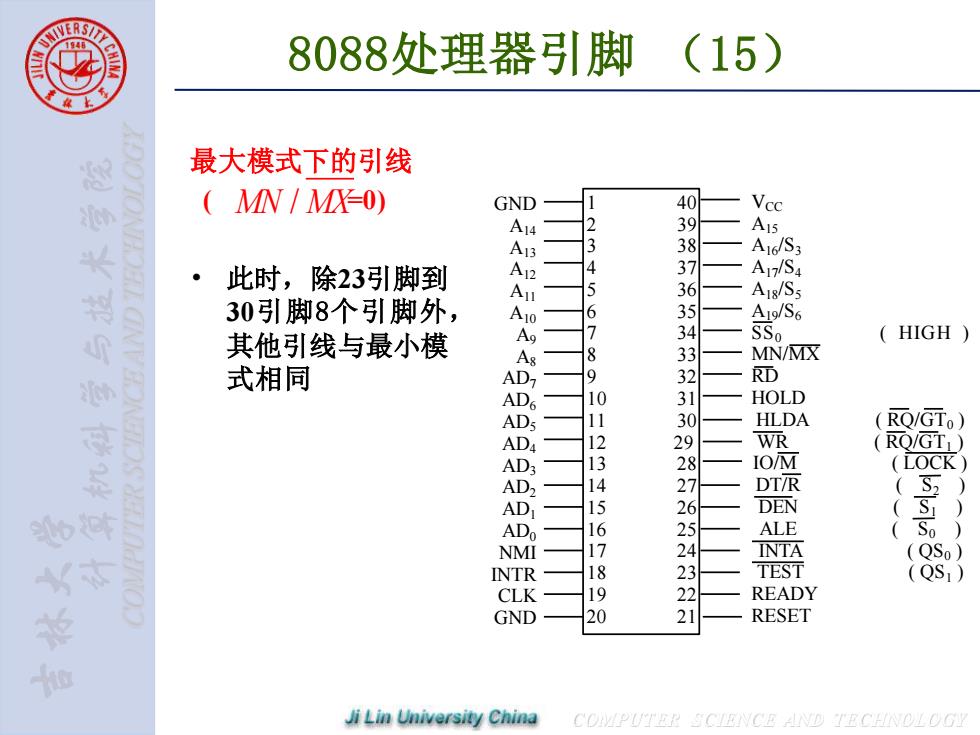

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8088处理器引脚 (15) 最大模式下的引线 ( =0) • 此时,除23引脚到 30引脚8个引脚外, 其他引线与最小模 式相同 1 40 2 39 3 38 4 37 5 36 6 35 7 34 8 33 9 32 10 31 11 30 12 29 13 28 14 27 15 26 16 25 17 24 18 23 19 22 20 21 GND A14 A13 A12 A11 A10 A9 A8 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 NMI INTR CLK GND VCC A15 A16/S3 A17/S4 A18/S5 A19/S6 S S0 ( HIGH ) MN/MX RD HOLD HLDA ( RQ/GT0 ) WR ( RQ/GT1 ) IO/M ( LOCK ) DT/R ( S2 ) DEN ( S1 ) ALE ( S0 ) INTA ( QS0 ) TEST ( QS1 ) READY RESET MN / MX

8088处理器引脚 (16) 最大模式下的引线 S2、S1、S0总线周期状态信号输出,低电平有 效,三态。这3个信号连接到总线控制器8288的 输入端,8288对它们译码后可以产生系统总线所 需要的各种控制信号。三个信号的代码组合以及 对应的操作见表 S2、Si、S0 对应的操作 S2、S1、S0 对应的操作 0 0 0 发中断响应信号 00 取指令 0 0 1 读1/0端口 1 0 1 读内存 0 1 0 写1/0端口 1 1 0 写内存 0 11 暂停 11 无作用 Ji Lin University China COMPUTER SCIENCE AND TECHNOLOGY

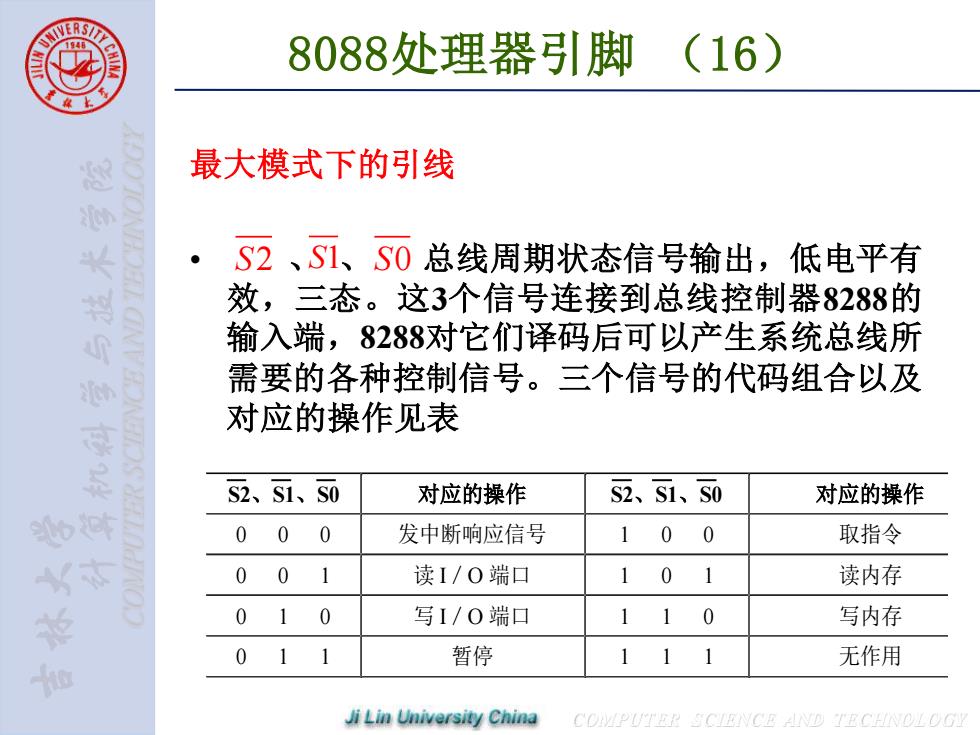

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8088处理器引脚 (16) 最大模式下的引线 • 、 、 总线周期状态信号输出,低电平有 效,三态。这3个信号连接到总线控制器8288的 输入端,8288对它们译码后可以产生系统总线所 需要的各种控制信号。三个信号的代码组合以及 对应的操作见表 S2 S1 S0 S2、S1、S0 对应的操作 S2、S1、S0 对应的操作 0 0 0 发中断响应信号 1 0 0 取指令 0 0 1 读 I/O 端口 1 0 1 读内存 0 1 0 写 I/O 端口 1 1 0 写内存 0 1 1 暂停 1 1 1 无作用

8088处理器引脚 (17) 最大模式下的引线 RQ/GT1、RQ/GT0总线请求/总线响应信号引脚。 每一个引脚都具有双向功能,既是总线请求输入 也是总线响应输出。但是 比OGT0具有更高的优先权。这些引脚内部都有 上拉电阻,所以在未使用时可以悬空 LOCK总线封锁信号输出,低电平有效。该信 号有效时,CPU锁定总线,不允许其他的总线控 制设备申请使用系统总线 i Lin University China CpTE型CIENCE AND T厘CHNDOLOGY

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8088处理器引脚 (17) 最大模式下的引线 • 、 总线请求/总线响应信号引脚。 每一个引脚都具有双向功能,既是总线请求输入 也是总线响应输出。但是 比 具有更高的优先权。这些引脚内部都有 上拉电阻,所以在未使用时可以悬空 • 总线封锁信号输出,低电平有效。该信 号有效时,CPU锁定总线,不允许其他的总线控 制设备申请使用系统总线 RQ/GT1 RQ/GT0 LOCK RQ/GT0

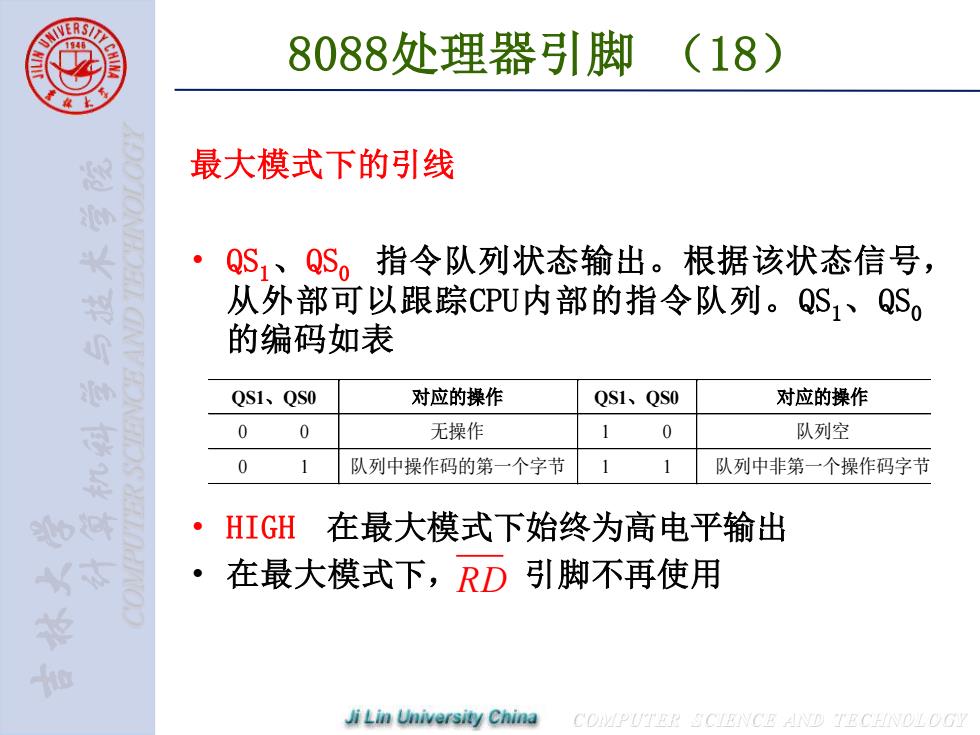

8088处理器引脚 (18) 最大模式下的引线 QS1、 QS。指令队列状态输出。根据该状态信号, 从外部可以跟踪CPU内部的指令队列。QS1、QS。 的编码如表 QS1、QS0 对应的操作 QS1、QS0 对应的操作 0 0 无操作 1 队列空 0 队列中操作码的第一个字节 队列中非第一个操作码字节 HIGH 在最大模式下始终为高电平输出 在最大模式下,RD 引脚不再使用 Ji Lin University China COMPUTER SCIENCE AND TECHNOLOGY

COMPUTER SCIENCE AND TECHNOLOGY COMPUTER SCIENCE AND TECHNOLOGY 8088处理器引脚 (18) 最大模式下的引线 • QS1、QS0 指令队列状态输出。根据该状态信号, 从外部可以跟踪CPU内部的指令队列。QS1、QS0 的编码如表 • HIGH 在最大模式下始终为高电平输出 • 在最大模式下, 引脚不再使用 QS1、QS0 对应的操作 QS1、QS0 对应的操作 0 0 无操作 1 0 队列空 0 1 队列中操作码的第一个字节 1 1 队列中非第一个操作码字节 RD