并行和顺序逻辑关系的表示 >如在模块中逻辑功能由下面三个语句块组成: assign cs=(a0&~a1&~a2);∥--1 and2 and_inst qout,a,b); ∥---2 always@(posedge clk or posedge clr)∥--3 begin if (clr)q<=0;else if (en)g<=d; end >1、2、3三条语句是并行的,它们产生独立的逻辑电路 >而在always块中:begin与end之间是顺序执行的。 菌州支通大学

并行和顺序逻辑关系的表示 如在模块中逻辑功能由下面三个语句块组成 : assign cs = ( a0 & ~a1 & ~a2 ) ; // -----1 and2 and_inst ( qout, a, b); // -----2 always @ (posedge clk or posedge clr) //-----3 begin if (clr) q<= 0; else if (en) q<= d; end 1、2、3三条语句是并行的,它们产生独立的逻辑电路 ; 而在 always 块中: begin与end之间是顺序执行的

行为级模块描述语句 —赋值语句 >门基元赋值语句 >连续赋值语句(assign) 针对组和逻辑 >过程赋值语句(只出现在always语句中) >阻塞赋值语句(=) >首先计算右边的值,然后立即赋给左边 >顺序块内的语句依次执行,并行块内语句并行执行 >多用于行为仿真和时序仿真 >非阻塞赋值语句(<=) >在begin..end顺序块中,语句间并发执行 >仿真中,先计算右边的值,在时钟沿统一赋值 凿州道大挚

行为级模块描述语句——赋值语句 门基元赋值语句 连续赋值语句(assign)——针对组和逻辑 过程赋值语句(只出现在always语句中 ) 阻塞赋值语句(=) 首先计算右边的值,然后立即赋给左边 顺序块内的语句依次执行,并行块内语句并行执行 多用于行为仿真和时序仿真 非阻塞赋值语句(<=) 在begin…end顺序块中,语句间并发执行 仿真中,先计算右边的值,在时钟沿统一赋值给左边

Verilog中两种不同的赋值语句 >非阻塞(non-blocking)赋值语句: always @(posedge clk) begin b<= a cl c<=b; k end DF DF 菌州克通大学

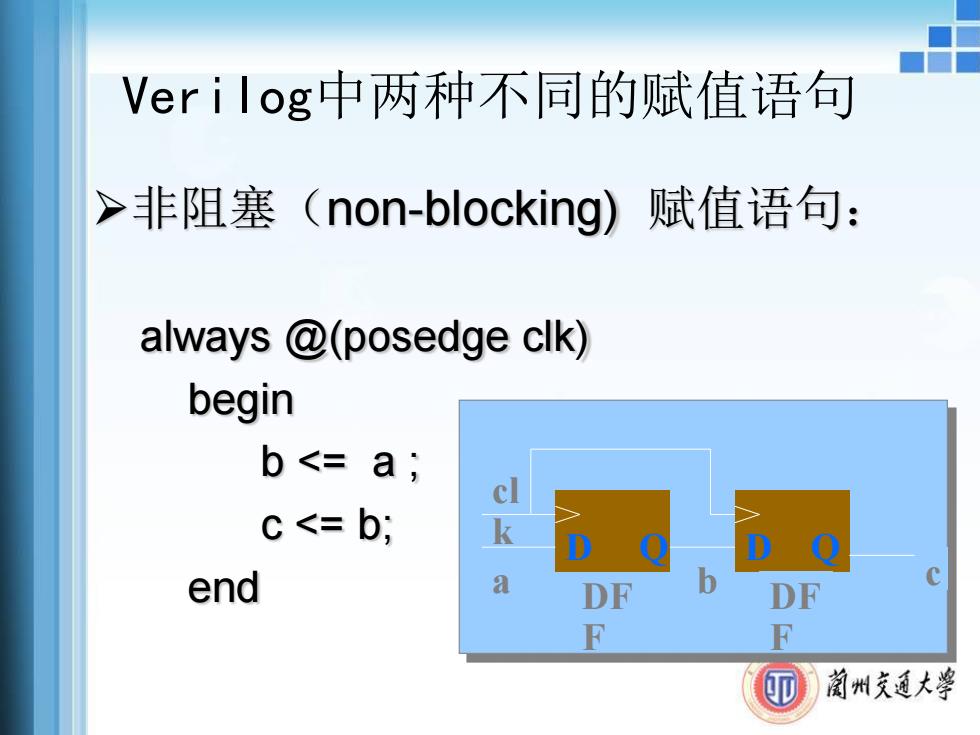

Verilog中两种不同的赋值语句 非阻塞(non-blocking) 赋值语句: always @(posedge clk) begin b <= a ; c <= b; end cl k DF F c D Q D Q a b DF F