EDA方法(设计)及实验 国家级电工电子实验教学示范中心

EDA方法(设计)及实验 国家级电工电子实验教学示范中心

第4章Verilog语言 ⑩ 菌州克通大婆

第4章 Verilog语言

4.1 Verilog HDL Verilog HDL也是目前应用最为广泛的硬件描述语言 ,并被EEE采纳为IEEE#1064-1995(即Verilog-.1995)标 准,并于2001和2005分别升级为Veri1og-2001和 SysemVerilog-2005标准。Verilog HDL可以用来进行各种 层次的逻辑设计,也可以进行数字系统的逻辑综合、仿真 验证和时序分析。Verilog HDL适合算法级(Algorithm) 、寄存器传输级(RTL)逻辑级(Logic)、门级(Gate) 和版图级(Layout)等各个层次的电路设计和描述。 2015/7/3 菌州发通濘

2015/7/3 3 4.1 Verilog HDL Verilog HDL也是目前应用最为广泛的硬件描述语言 ,并被IEEE采纳为IEEE#1064-1995(即Verilog-1995)标 准,并于2001和2005分别升级为Verilog-2001和 SysemVerilog-2005标准。Verilog HDL可以用来进行各种 层次的逻辑设计,也可以进行数字系统的逻辑综合、仿真 验证和时序分析。Verilog HDL适合算法级(Algorithm) 、寄存器传输级(RTL)逻辑级(Logic)、门级(Gate) 和版图级(Layout)等各个层次的电路设计和描述

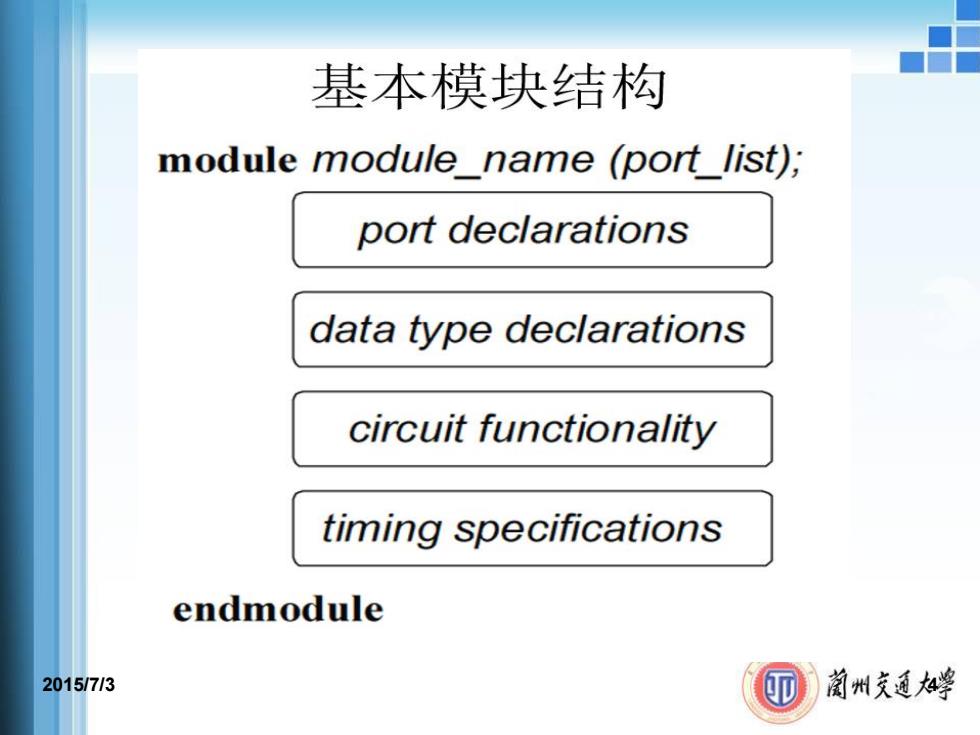

基本模块结构 module module name (port list); port declarations data type declarations circuit functionality timing specifications endmodule 2015/7/3 菌州克通婷

2015/7/3 4

有哪几种硬件描述语言? 各有什么特点? >Verilog HDL >较多的第三方工具的支持 >语法结构比VHDL简单 >学习起来比VHDL容易 >仿真工具比较好使 >测试激励模块容易编写 ⑩ 菌州克通大学

有哪几种硬件描述语言? 各有什么特点? Verilog HDL 较多的第三方工具的支持 语法结构比VHDL简单 学习起来比VHDL容易 仿真工具比较好使 测试激励模块容易编写