EDA方法(设计)及实验 国家级电工电子实验教学示范中心

EDA方法(设计)及实验 国家级电工电子实验教学示范中心

第3章EDA开发 ⑩ 菌州克通大婆

第3章 EDA开发

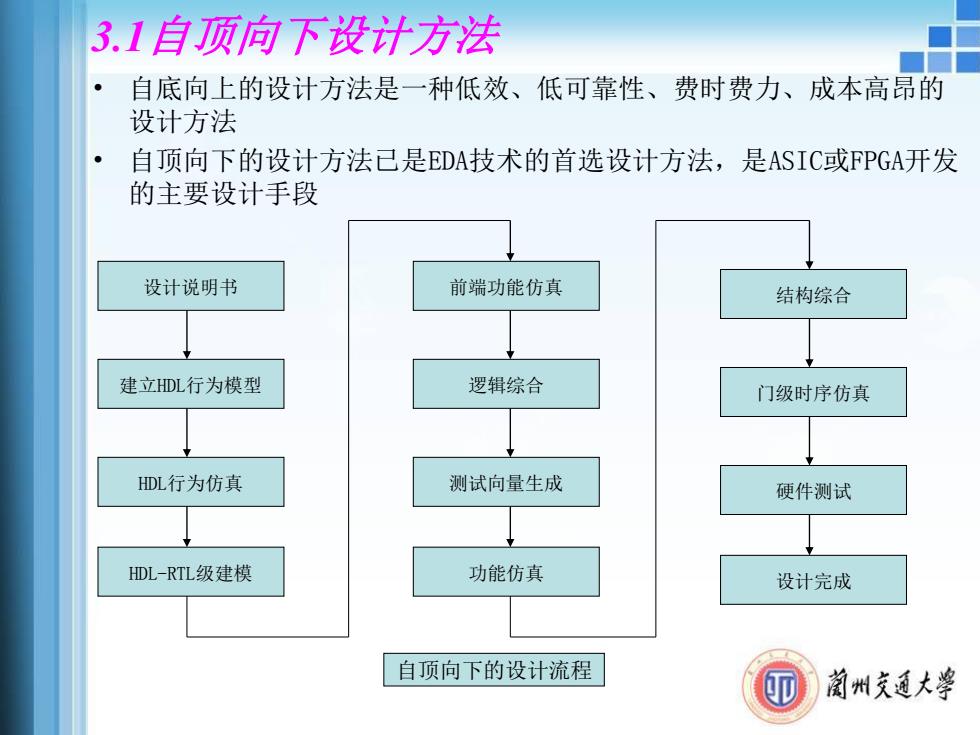

3.1自顶向下设计方法 自底向上的设计方法是一种低效、低可靠性、费时费力、成本高昂的 设计方法 自顶向下的设计方法己是EDA技术的首选设计方法,是ASIC或FPGA开发 的主要设计手段 设计说明书 前端功能仿真 结构综合 建立HDL行为模型 逻辑综合 门级时序仿真 HDL行为仿真 测试向量生成 硬件测试 HDL-RTL级建模 功能仿真 设计完成 自顶向下的设计流程 菌州克通大粤

3.1自顶向下设计方法 • 自底向上的设计方法是一种低效、低可靠性、费时费力、成本高昂的 设计方法 • 自顶向下的设计方法已是EDA技术的首选设计方法,是ASIC或FPGA开发 的主要设计手段 设计说明书 建立HDL行为模型 HDL行为仿真 HDL-RTL级建模 前端功能仿真 逻辑综合 测试向量生成 功能仿真 结构综合 门级时序仿真 硬件测试 设计完成 自顶向下的设计流程

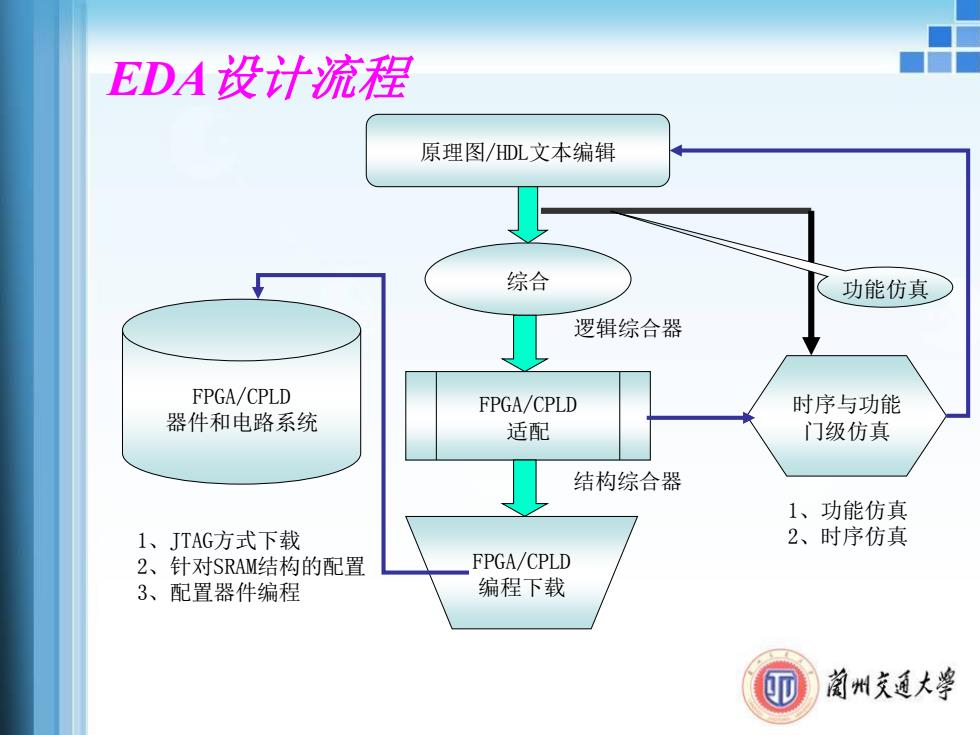

EDA设计流程 原理图/DL文本编辑 综合 功能仿真 逻辑综合器 FPGA/CPLD FPGA/CPLD 时序与功能 器件和电路系统 适配 门级仿真 结构综合器 1、功能仿真 1、JTAG方式下载 2、时序仿真 2、针对SRAM结构的配置 FPGA/CPLD 3、配置器件编程 编程下载 菌州克通大等

EDA设计流程 原理图/HDL文本编辑 综合 FPGA/CPLD 适配 FPGA/CPLD 编程下载 FPGA/CPLD 器件和电路系统 时序与功能 门级仿真 1、功能仿真 2、时序仿真 逻辑综合器 结构综合器 1、JTAG方式下载 2、针对SRAM结构的配置 3、配置器件编程 功能仿真

按是否考虑硬件延时等(时序仿真与功能仿真) 是直接对VHDL、原理图描述或其他 描述形式的逻辑功能进行测试模拟,以了解 功能仿真 其实现的功能是否满足原设计的要求的过程, 仿真过程不涉及任何具体器件的硬件特性。 就是接近真实器件运行特性的仿真, 时序仿真 仿真文件中己包含了器件硬件特性参数, 因而,仿真精度高。 通常首先进行功能仿真,待确认设计文件所表达的功 能满足设计者的意图时,再进行综合适配和时序仿真,以 便更了解目标器件工作的功能时序。 菌州克通大学

按是否考虑硬件延时等(时序仿真与功能仿真) 时序仿真 功能仿真 就是接近真实器件运行特性的仿真, 仿真文件中己包含了器件硬件特性参数, 因而,仿真精度高。 是直接对VHDL、原理图描述或其他 描述形式的逻辑功能进行测试模拟,以了解 其实现的功能是否满足原设计的要求的过程, 仿真过程不涉及任何具体器件的硬件特性。 通常首先进行功能仿真,待确认设计文件所表达的功 能满足设计者的意图时,再进行综合适配和时序仿真,以 便更了解目标器件工作的功能时序