Ver i log HDL的建模方式 >即:模块的描述方式: >行为级建模 >模块内部只包括过程块和连续赋值语句,而不包 括实例调用语句和基本元件实例调用语句。 >RTL级属于行为级 >结构级建模 >模块内部只包括实例调用语句。 >包括门级和开关级 >行为级与结构级混合建模 >两者兼而有之 ⑩ 菌州克通大粤

Verilog HDL 的建模方式 即:模块的描述方式: 行为级建模 模块内部只包括过程块和连续赋值语句,而不包 括实例调用语句和基本元件实例调用语句。 RTL级属于行为级 结构级建模 模块内部只包括实例调用语句。 包括门级和开关级 行为级与结构级混合建模 两者兼而有之

Verilog HDL的抽象级别 >语言本身提供了各种层次抽象的表述,可以用 详细程度有很大差别的的多层次模块组合来描 述一个电路系统。 >行为级:技术指标和算法的Verilog描述 >RTL级:逻辑功能的Verilog描述 >门级:逻辑结构的Verilog描述 >开关级:具体的晶体管物理器件的描述 菌州克通大学

Verilog HDL 的抽象级别 语言本身提供了各种层次抽象的表述,可以用 详细程度有很大差别的的多层次模块组合来描 述一个电路系统。 行为级:技术指标和算法的Verilog描述 RTL级:逻辑功能的Verilog描述 门级:逻辑结构的Verilog描述 开关级:具体的晶体管物理器件的描述

Verilog HDL的抽象级别 >行为级:有关行为和技术指标模块,容易理解 >RTL级:有关逻辑执行步骤的模块,较难理解 >门级:有关逻辑部件互相连接的模块,很难理 解 >开关级:有关物理形状和布局参数的模块,非 常难理解 菌州克通大等

Verilog HDL 的抽象级别 行为级:有关行为和技术指标模块,容易理解 RTL级:有关逻辑执行步骤的模块,较难理解 门级:有关逻辑部件互相连接的模块,很难理 解 开关级:有关物理形状和布局参数的模块,非 常难理解

抽象级别和综合与仿真的关系 >行为仿真:行为的验证和验证模块分割的合理性 >前仿真:即RTL级仿真,检查有关模块逻辑执行 步骤是否正确。 >逻辑综合:把RTL级模块转换成门级。 >后仿真:用门级模型做验证,检查门的互连逻辑 其功能是否正确。 >布局布线:在门级模型的基础上加上了布线延时 >布局布线后仿真:与真实的电路最接近的验证。 菌州克通大学

抽象级别和综合与仿真的关系 行为仿真:行为的验证和验证模块分割的合理性 前仿真:即RTL级仿真,检查有关模块逻辑执行 步骤是否正确。 逻辑综合:把RTL级模块转换成门级。 后仿真:用门级模型做验证,检查门的互连逻辑 其功能是否正确。 布局布线:在门级模型的基础上加上了布线延时 布局布线后仿真:与真实的电路最接近的验证

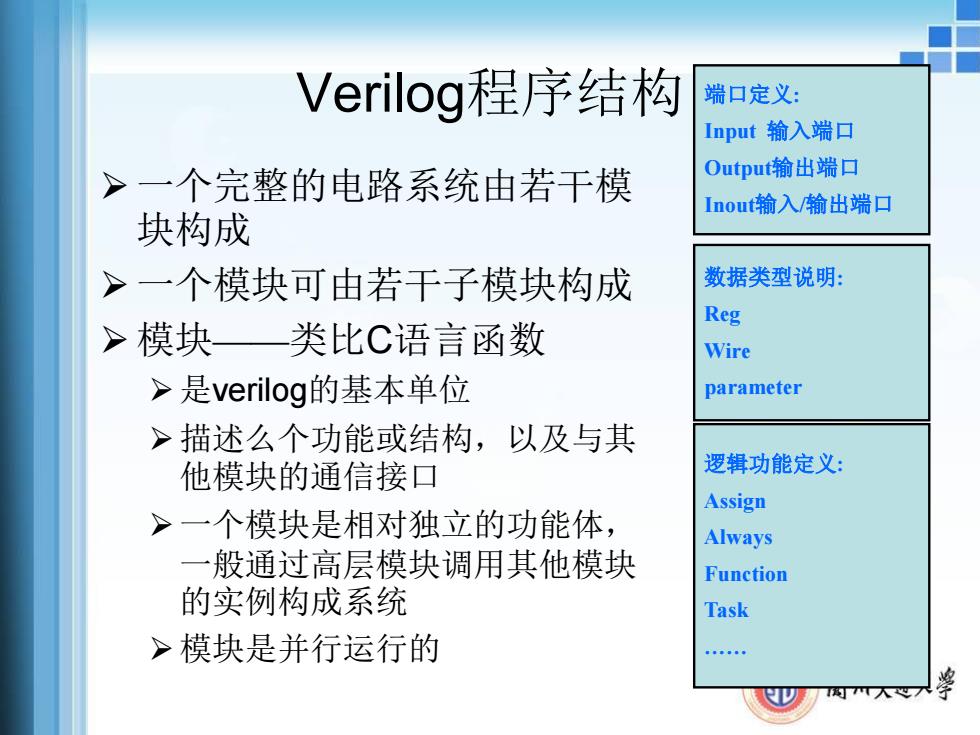

Verilog程序结构 端口定义: Input输入端口 一个完整的电路系统由若干模 Output输出端口 Inout输入/输出端口 块构成 >一个模块可由若干子模块构成 数据类型说明: Reg >模块—类比C语言函数 Wire >是verilog的基本单位 parameter >描述么个功能或结构,以及与其 他模块的通信接口 逻辑功能定义: Assign >一个模块是相对独立的功能体, Always 一 般通过高层模块调用其他模块 Function 的实例构成系统 Task >模块是并行运行的

Verilog程序结构 一个完整的电路系统由若干模 块构成 一个模块可由若干子模块构成 模块——类比C语言函数 是verilog的基本单位 描述么个功能或结构,以及与其 他模块的通信接口 一个模块是相对独立的功能体, 一般通过高层模块调用其他模块 的实例构成系统 模块是并行运行的 端口定义: Input 输入端口 Output输出端口 Inout输入/输出端口 数据类型说明: Reg Wire parameter 逻辑功能定义: Assign Always Function Task ……