第五章51单片机的外围模块及应用1、并行I/0口MCS-51共有4个8位的I/O口(PO、P1、P2、P3),以实现数据的并行输入/输出。2、定时/计数器8051共有两个16位的定时/计数器,以实现定时或计数功能,并以其定时或计数结果对计算机进行控制。3、串行口MCS-51单片机有一个全双工的串行口,以实现单片机和其它设备之间的串行数据传送。该串行口功能较强,既可作为全双工异步通信收发器使用,也可作为同步移位器使用。5.1并行口及其应用51单片机有4个1/O端口,每个端口都是8位准双向口,共占32根引脚。每个端口都包括一个锁存器(即专用寄存器PO~P3)、一个输出驱动器和输入缓冲器。通常把4个端口笼统地表示为PO~P3。I/O口引脚(1)PO(PO.0~PO.7):作为普通I/O口使用,须外接上拉电阻;作为与外部传送数据的8位数据总线(DO~D7);作为扩展外部存储器时的低8位地址总线(A0~A7)。(2)P1口(P1.0~P1.7):

第五章 51单片机的外围模块及应用 1、并行I/O口 MCS-51共有4个8位的I/O口(P0、P1、P2、P3),以实现数据的并行输 入/输出。 2、定时/计数器 8051共有两个16位的定时/计数器,以实现定时或计数功能,并以其定时 或计数结果对计算机进行控制。 3、串行口 MCS-51单片机有一个全双工的串行口,以实现单片机和其它设备之间的串 行数据传送。该串行口功能较强,既可作为全双工异步通信收发器使用,也可作 为同步移位器使用。 5.1 并行口及其应用 51单片机有4个I/O端口,每个端口都是8位准双向口,共占32根引脚。每个端 口都包括一个锁存器(即专用寄存器P0~P3)、一个输出驱动器和输入缓冲器。通常 把4个端口笼统地表示为P0~P3。 I/O口引脚 (1) P0口(P0.0~P0.7): 作为普通I/O口使用,须外接上拉电阻; 作为与外部传送数据的8位数据总线(D0~D7); 作为扩展外部存储器时的低8位地址总线(A0~A7)。 (2) P1口(P1.0~P1.7):

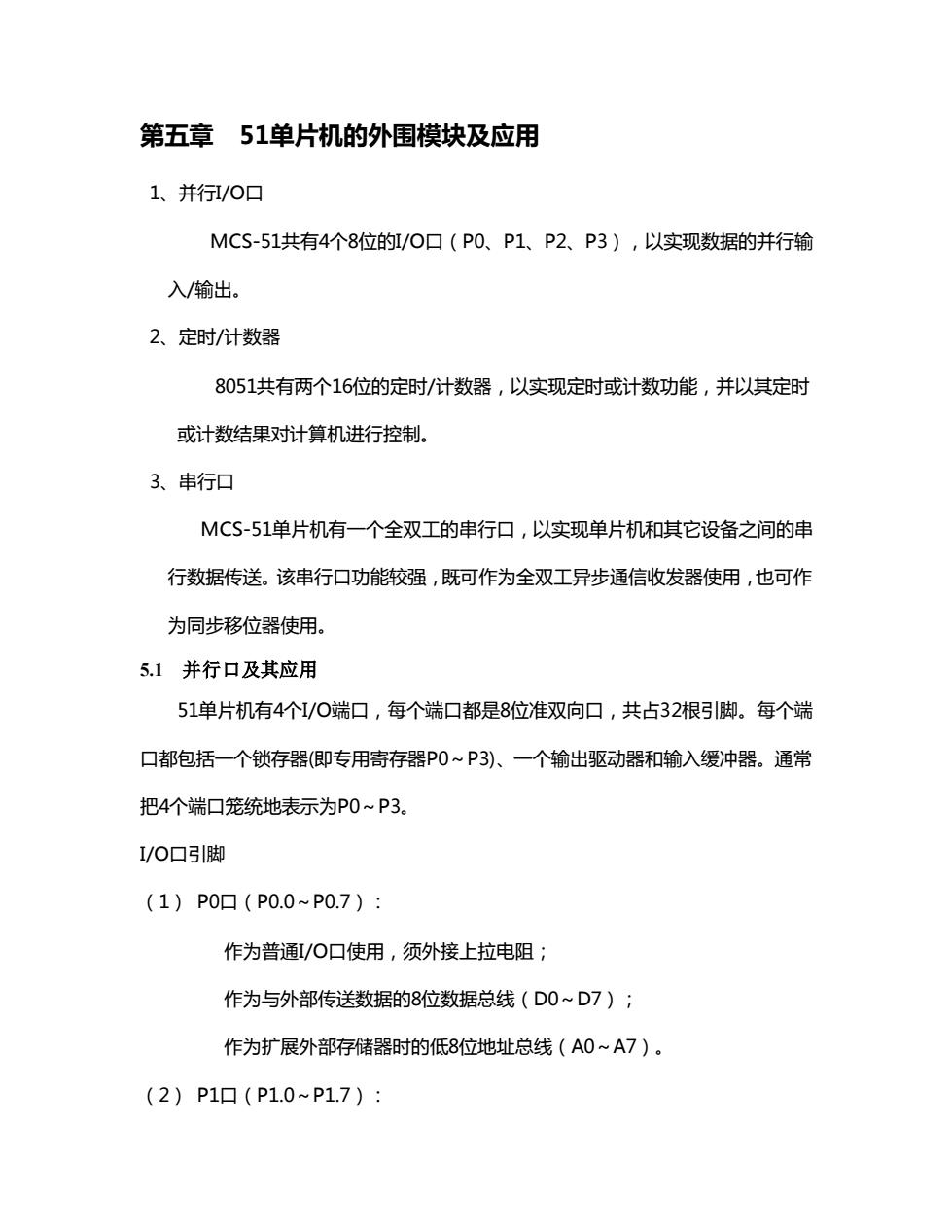

作为普通I/O口使用,无须外接上拉电阻(80C52的P1.0和P1.1还具有特殊功能见表2-1)。(3)P2(P2.0~P2.7):作为普通/O口使用,无须外接上拉电阻。作为扩展外部存储器时的高8位地址总线(A8~A15)。(4) P3(P3.0~P3.7):作为普通/O口使用,无须外接上拉电阻;每个引脚都具有第二功能。51系列单片机的并行口,按其特性可分为以下类型:单一的准双向口多种功能复用的准双向口;可作为地址总线输出口的准双向口;可作为地址/数据总线口的三态双向口。VCC读锁存器内部上拉电阻内部总线D锁存器写锁存器Q读引脚

作为普通I/O口使用,无须外接上拉电阻(80C52的P1.0和P1.1还具有特 殊功能见表2-1)。 (3) P2口(P2.0~P2.7): 作为普通I/O口使用,无须外接上拉电阻。 作为扩展外部存储器时的高8位地址总线(A8~A15)。 (4)P3口(P3.0~P3.7): 作为普通I/O口使用,无须外接上拉电阻; 每个引脚都具有第二功能。 51系列单片机的并行口,按其特性可分为以下类型: 单一的准双向口; 多种功能复用的准双向口; 可作为地址总线输出口的准双向口; 可作为地址/数据总线口的三态双向口。 锁存器 Q D Q 读锁存器 写锁存器 内部总线 读引脚 内部上拉电阻 T VCC

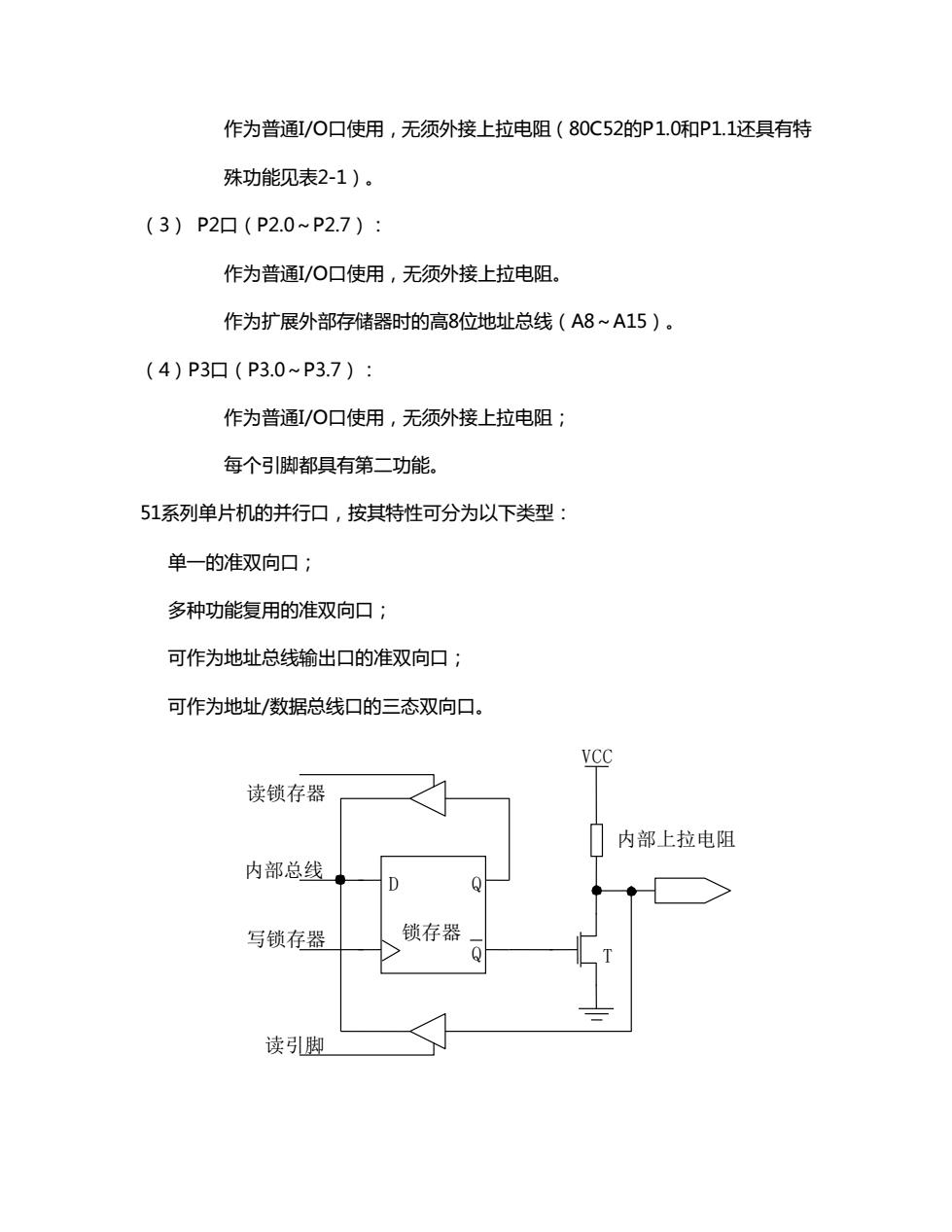

(a)单一功能准双向口VCC第二输出功能读锁存器内部上拉电阻内部总线-锁存器写锁存器Q读引脚第二输入功能(b)多功能准双向口VC控地读锁存内部上拉电内部总DQ锁存写锁存Q读引(c)可作为地址总线口的准双向口P2

(a)单一功能准双向口 (b)多功能准双向口 (c)可作为地址总线口的准双向口P2 . 锁存器 Q D Q 读锁存器 写锁存器 内部总线 读引脚 T VCC 第二输入功能 第二输出功能 内部上拉电阻 锁 存 器 Q D Q 读锁存 器 写锁存 器 内部总 线 读 引 脚 T VC C 地 址 控 制 内 部 上 拉 电 阻 MU X

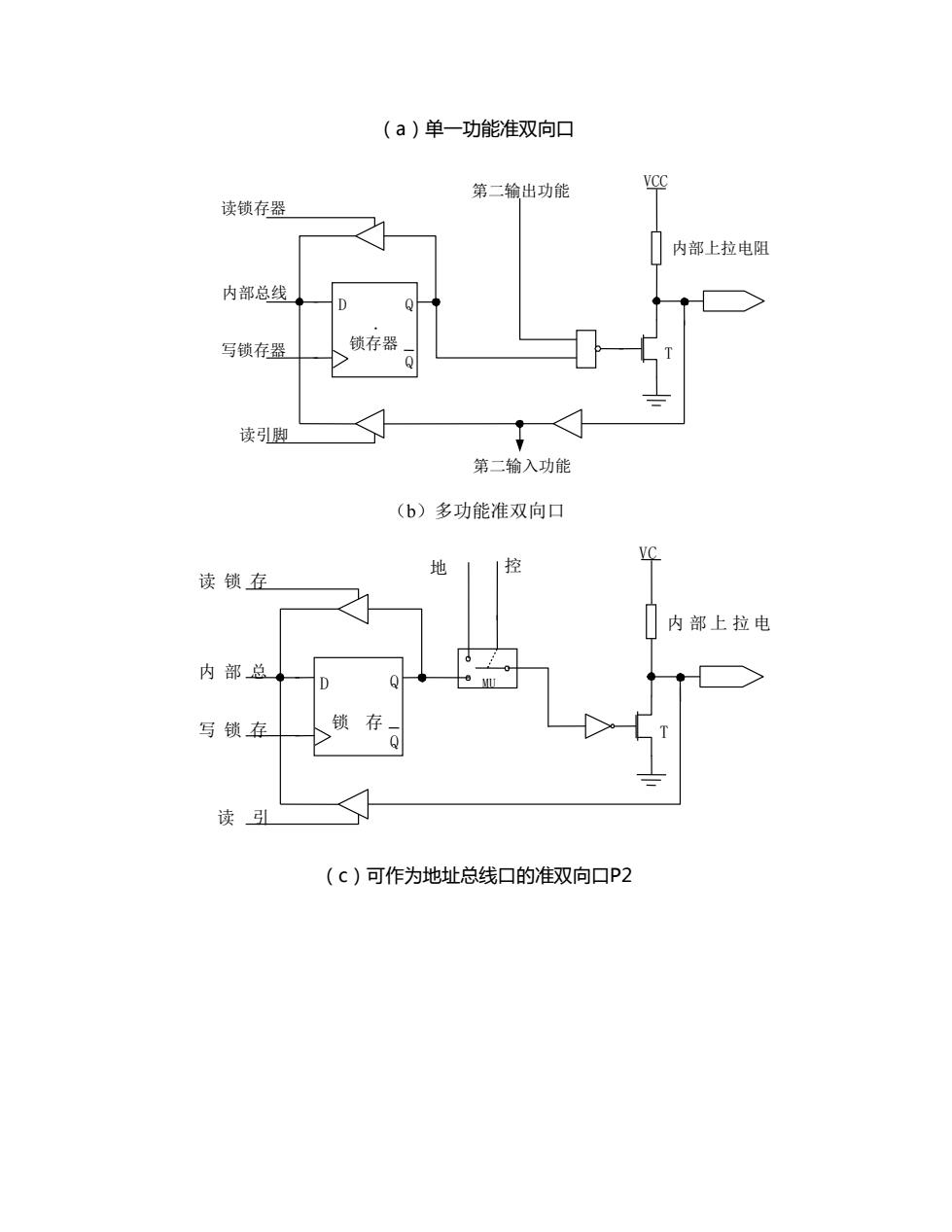

VO地址/数控读锁存内部总D锁存写锁存.Q读引(d)可作为地址/数据总线口的三态双向口PO读锁存器和读引脚指令当把PO~P3口作为输入引脚使用时,以I/O口作为源操作数的数据传送指令、算术/逻辑运算指令及位测试转移指令等均属读引脚指令。所有的“读一改一写”指令均读I/O口锁存器。结构组成:它由一个输出锁存器、两个三态输入缓冲器和输出驱动电路组成--准双向口。功能:作为通用1/O使用。VCC读锁存器内部上拉电阻内部总线DP1.nP1.n锁存器写锁存器读引脚

(d)可作为地址/数据总线口的三态双向口 P0 读锁存器和读引脚指令 当把 P0~P3 口作为输入引脚使用时,以 I/O 口作为源操作数的数据传送指 令、算术/逻辑运算指令及位测试转移指令等均属读引脚指令。 所有的“读—改—写”指令均读 I/O 口锁存器。 结构组成:它由一个输出锁存器、两个三态输入缓冲器和输出驱动电路组成- 准双向口。 功能:作为通用 I/O 使用。 P1.n 锁存器 P1.n Q D Q 读锁存器 写锁存器 内部总线 读引脚 内部上拉电阻 T VCC 锁 存 器 Q D Q 读锁存 器 写锁存 器 内部总 线 读 引 脚 T1 T2 VC C MU X 地 址 / 数 据 控 制

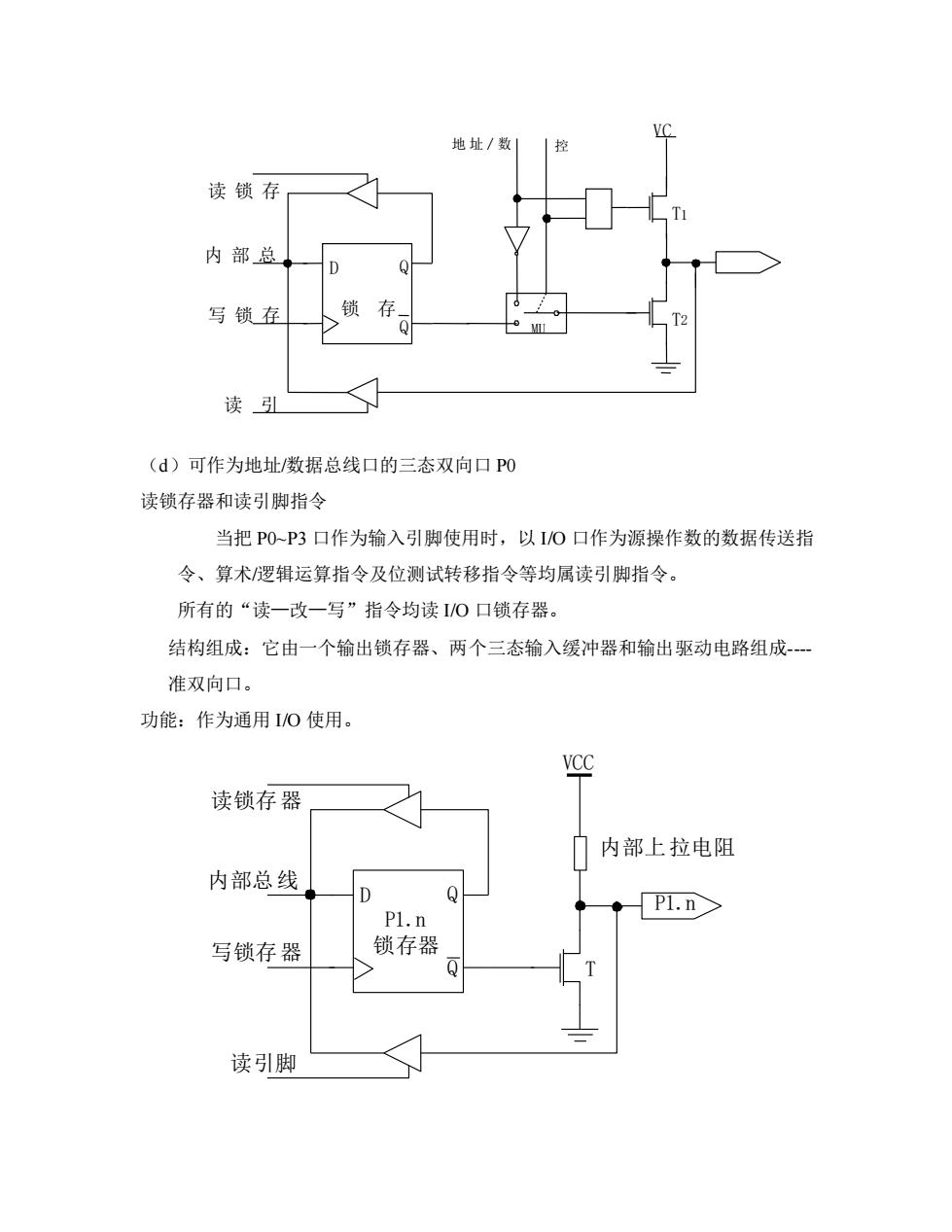

图5-1-1P1口的口线逻辑电路图5.1.1 P1 口结构组成:它由一个输出锁存器、两个三态输入缓冲器和输出驱动电路组成----准双向口。P1口作输出口时,内部数据经过锁存器送到P1.0---P1.7上。由于内部有上拉电阻,所以P1口作输出口使用时,不用外接上拉电阻。P1口作输入口时,P1.0一P1.7上的信号经过缓冲器送到内部数据总线上。在读引脚之前,要先将锁存器置1,否则总是读到0。CPU对I/O口的读操作有2种:读引脚和读锁存器。5.1.2 P3 功能:它除了可作为通用I/O端口外,还具有第二功能。作为通用I/O口使用时,与P2口类似。此时第二输出功能控制信号为1。VCC第二输出功能读锁存器内部上拉电阻内部总线DQP3.nP3. n锁存器写锁存器Q>读引脚第二输入功能图5-1-2P3口的口线逻辑电路图此时CPU自动向锁存器写1,引脚部分输入(第二输出功能控制信号为1),部分输出(从第二输出功能输出信号)。5.1.3P2口功能:作为通用1/O使用和高8位地址线

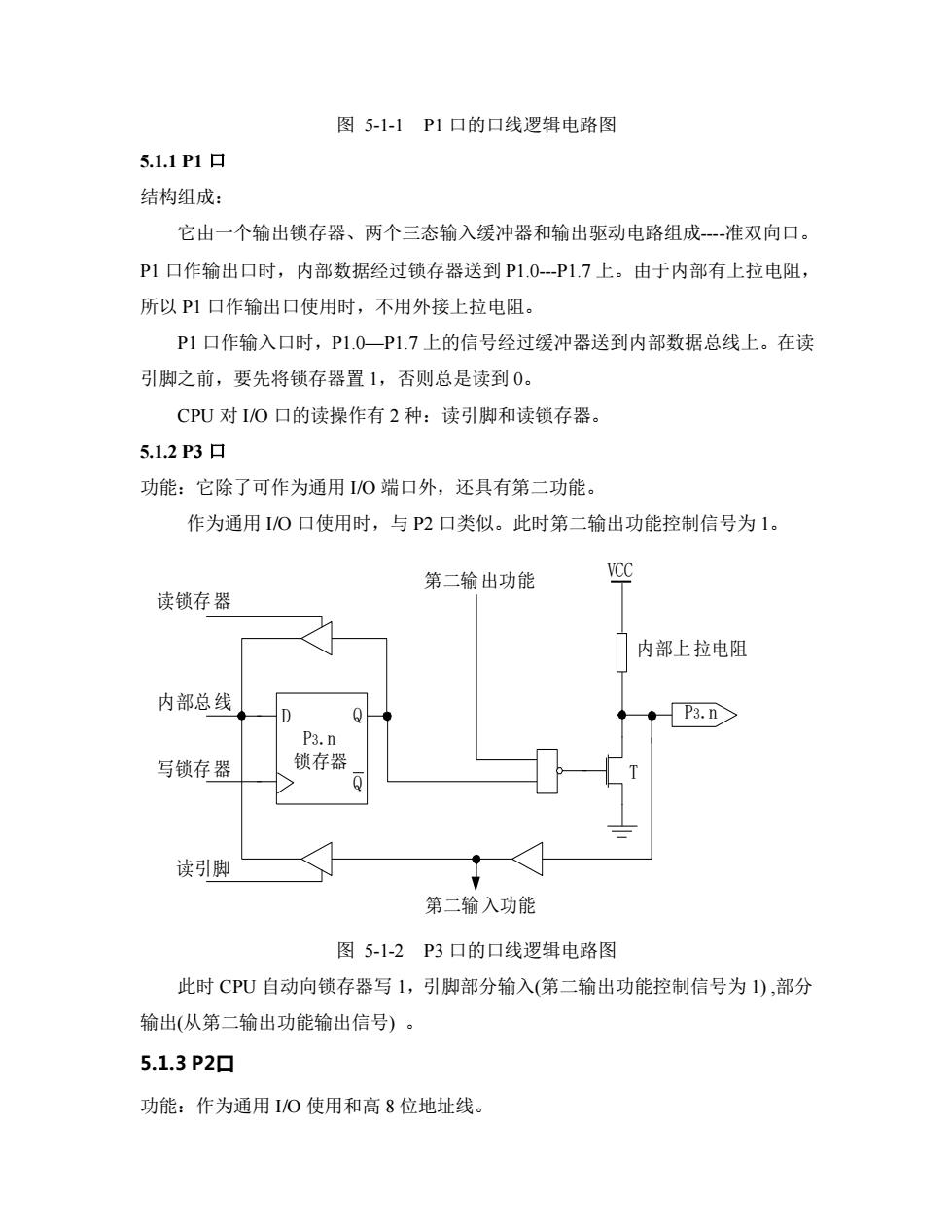

图 5-1-1 P1 口的口线逻辑电路图 5.1.1 P1 口 结构组成: 它由一个输出锁存器、两个三态输入缓冲器和输出驱动电路组成-准双向口。 P1 口作输出口时,内部数据经过锁存器送到 P1.0-P1.7 上。由于内部有上拉电阻, 所以 P1 口作输出口使用时,不用外接上拉电阻。 P1 口作输入口时,P1.0—P1.7 上的信号经过缓冲器送到内部数据总线上。在读 引脚之前,要先将锁存器置 1,否则总是读到 0。 CPU 对 I/O 口的读操作有 2 种:读引脚和读锁存器。 5.1.2 P3 口 功能:它除了可作为通用 I/O 端口外,还具有第二功能。 作为通用 I/O 口使用时,与 P2 口类似。此时第二输出功能控制信号为 1。 图 5-1-2 P3 口的口线逻辑电路图 此时 CPU 自动向锁存器写 1,引脚部分输入(第二输出功能控制信号为 1) ,部分 输出(从第二输出功能输出信号) 。 5.1.3 P2口 功能:作为通用 I/O 使用和高 8 位地址线。 P3.n 锁存器 P3.n Q D Q 读锁存器 写锁存器 内部总线 读引脚 T VCC 第二输入功能 第二输出功能 内部上拉电阻