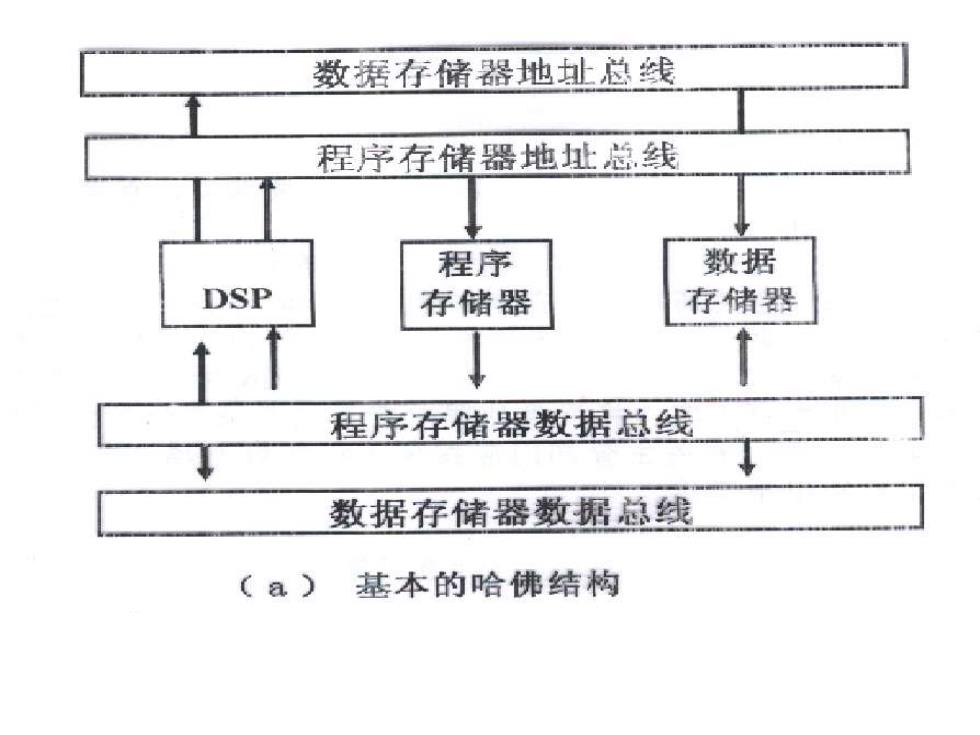

数据存储器地址总线 程序存储器地址总线 程序 数据 DSP 存储器 存储器 程序存储器数据总线 数据存储器数据总线 (a)基本的哈佛结构

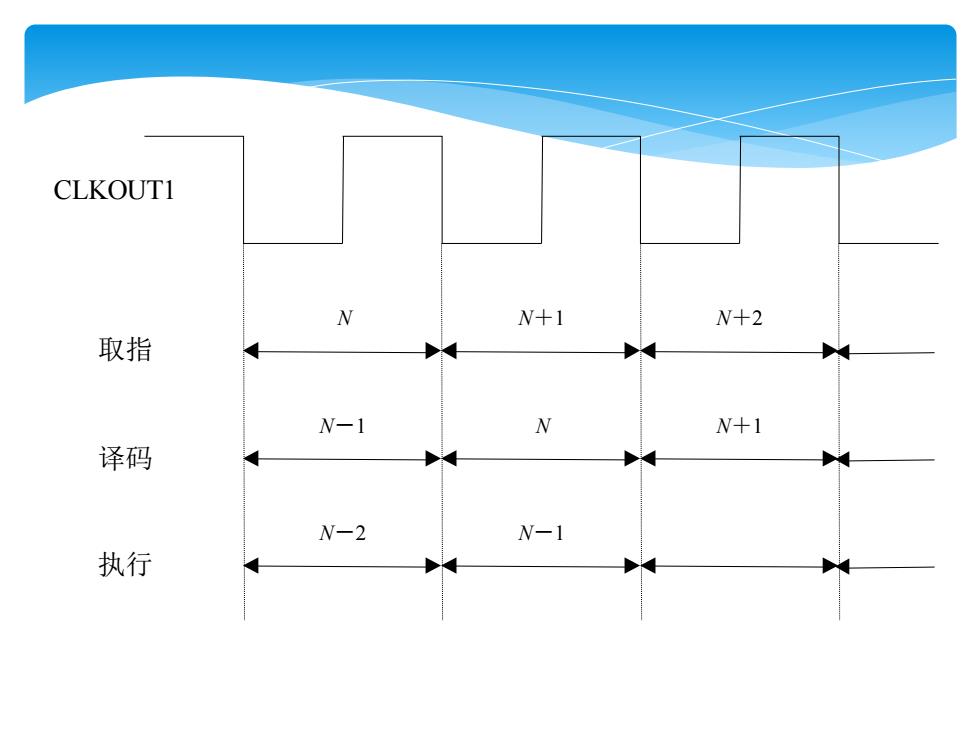

CLKOUTI N+1 N+2 取指 N-1 N+1 译码 N-2 N-1 执行

CLKOUT1 执行 译码 取指 N N - 1 N - 2 N + 1 N - 1 N + 2 N N + 1

2)具有高速阵列乘法器等专用硬件。精度 至少为16×16位定点,一些DSP的片内已含 有40X40位的浮,点乘法器。 3)具有高速的片内数据存储器和程序存储 器。 对于一些简单、单一的操作,例如卷积、 相关等,可以在片内完成,避免与外部的 低速存储器打交道。新近的DSP产品均为双 端口片内RAM

2)具有高速阵列乘法器等专用硬件。精度 至少为16×16位定点,一些DSP的片内已含 有40×40位的浮点乘法器。 3)具有高速的片内数据存储器和程序存储 器。 对于一些简单、单一的操作,例如卷积、 相关等,可以在片内完成,避免与外部的 低速存储器打交道。新近的DSP产品均为双 端口片内RAM

4)具有满足信号处理应用要求的一些特殊 指令。 乘法/累加指令 位反转寻址模式 数据移动操作 饱和溢出处理 重复指令

乘法/累加指令 位反转寻址模式 数据移动操作 饱和溢出处理 重复指令 4)具有满足信号处理应用要求的一些特殊 指令

5)具有高速的/0接口。 并行接口 串行接口 DMA 多处理器并行的链路接口 全局存储器的控制逻辑和接口

并行接口 串行接口 DMA 多处理器并行的链路接口 全局存储器的控制逻辑和接口 5)具有高速的I/O接口