K康科技 10.1F1R数字滤波器设计 2、4阶FIR滤波器节设计 Xin、hn0、hn1、hn2、hn3模块:(Altbus) 库:Altera DSP Builder中IO&Bus库 参数“Bus Type”设为“signed Integer” 参数“Node Type”设为“Input port” 参数“number of bits”设为“9” yn模块:(Altbus) 库:Altera DSP Builder中IO&Bus库 参数“Bus Type”设为“signed Integer'” 参数“Node Type”设为“Output port” 参数“number of bits”设为“20

KX 康芯科技 10.1 FIR数字滤波器设计 2、4阶FIR滤波器节设计 Xin、hn0、hn1、hn2、hn3模块:(Altbus) 库:Altera DSP Builder中IO & Bus库 参数“Bus Type”设为“signed Integer” 参数“Node Type”设为“Input port” 参数“number of bits”设为“9” yn模块:(Altbus) 库:Altera DSP Builder中IO & Bus库 参数“Bus Type”设为“signed Integer” 参数“Node Type”设为“Output port” 参数“number of bits”设为“20

K康芯科技 10.1F1R数字滤波器设计 2、4阶FIR滤波器节设计 xn4模块:(Altbus) 库:Altera DSP Builder中IO&Bus库 参数“Bus Type”设为“signed Integer, 参数“Node Type”设为“Output port” 参数“number of bits”设为“9” Parallel Adder Subtractor模块:(Parallel Adder Subtractor) 库:Altera DSP Builder中Arithmetic库 参数“Add(+)Sub(-)”设为“++++” 使用“Pipeline” 参数“Clock Phaese Selectioon”设为“1

KX 康芯科技 10.1 FIR数字滤波器设计 2、4阶FIR滤波器节设计 xn4模块:(Altbus) 库:Altera DSP Builder中IO & Bus库 参数“Bus Type”设为“signed Integer” 参数“Node Type”设为“Output port” 参数“number of bits”设为“9” Parallel Adder Subtractor模块:(Parallel Adder Subtractor) 库:Altera DSP Builder中Arithmetic库 参数“Add(+)Sub(-)”设为“++++” 使用“Pipeline” 参数“Clock Phaese Selectioon”设为“1

K康科技 10.1F1R数字滤波器设计 2、4阶FIR滤波器节设计 Delay、Delay1、Delay2、Delay3模块: (Delay) 库:Altera DSP Builder中Storage库 参数“Depth”设为“1” 参数“Clock Phase Selection”设为“I” Product模块:(Product) 库:Altera DSP Builder中Arithemtic库 参数“Pipeline”设为“2” 参数“Clock Phase Selection'设为“1” 不选择“Use LPM

KX 康芯科技 10.1 FIR数字滤波器设计 2、4阶FIR滤波器节设计 Delay、Delay1、Delay2、Delay3模块:(Delay) 库:Altera DSP Builder中Storage库 参数“Depth”设为“1” 参数“Clock Phase Selection”设为“1” Product模块:(Product) 库:Altera DSP Builder中Arithemtic库 参数“Pipeline”设为“2” 参数“Clock Phase Selection”设为“1” 不选择“Use LPM

K科拉 10.1F1R数字滤波器设计 3、16阶FIR滤波器模型设计 X >h2 >h3 x4 >h4 fir4tap4 图10-7fir4tap子系统

KX 康芯科技 10.1 FIR数字滤波器设计 3、16阶FIR滤波器模型设计 图10-7 fir4tap子系统

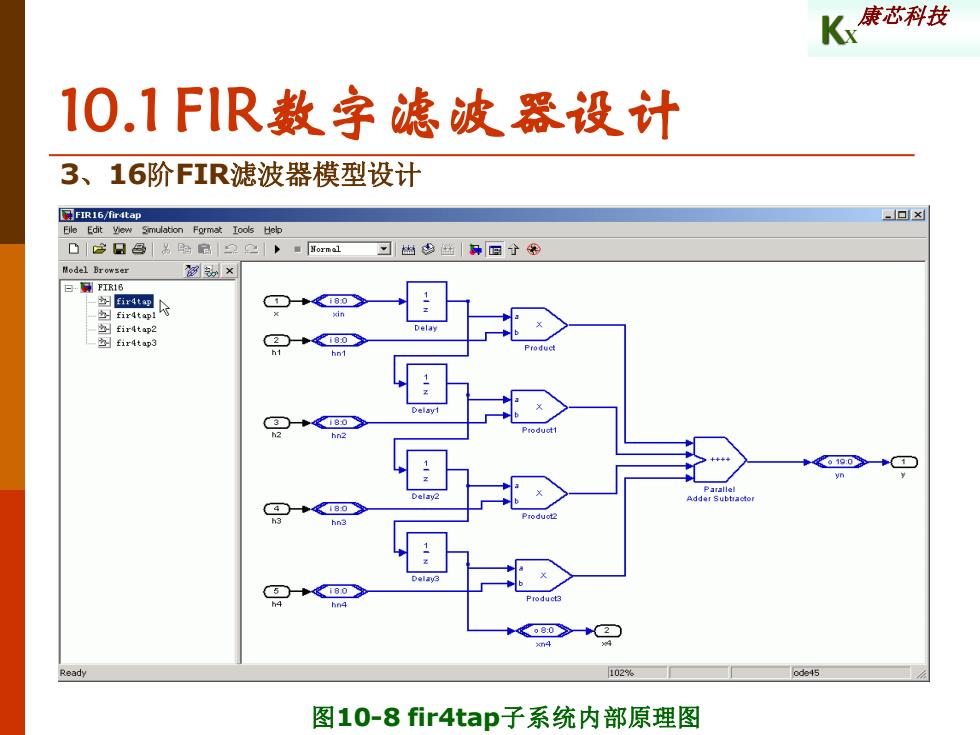

K 康芯科技 10.1F1R数字滤波器设计 3、16阶FIR滤波器模型设计 FIR16/fir4tap ▣x Eile Edit yew Smulation Format Iools Help D|含日马为的启≥|卜■m1可幽$地回8 odel Browser ☒动× FIR16 yEir4t fir4tap】 + fir4tap2 Delay fir4tap3 Delay Q+ hn2 0190 yn Delay2 Adder Subtractor Q+ 《80 +o0>+② Ready 102% d45 图10-8fir4tap子系统内部原理图

KX 康芯科技 10.1 FIR数字滤波器设计 3、16阶FIR滤波器模型设计 图10-8 fir4tap子系统内部原理图