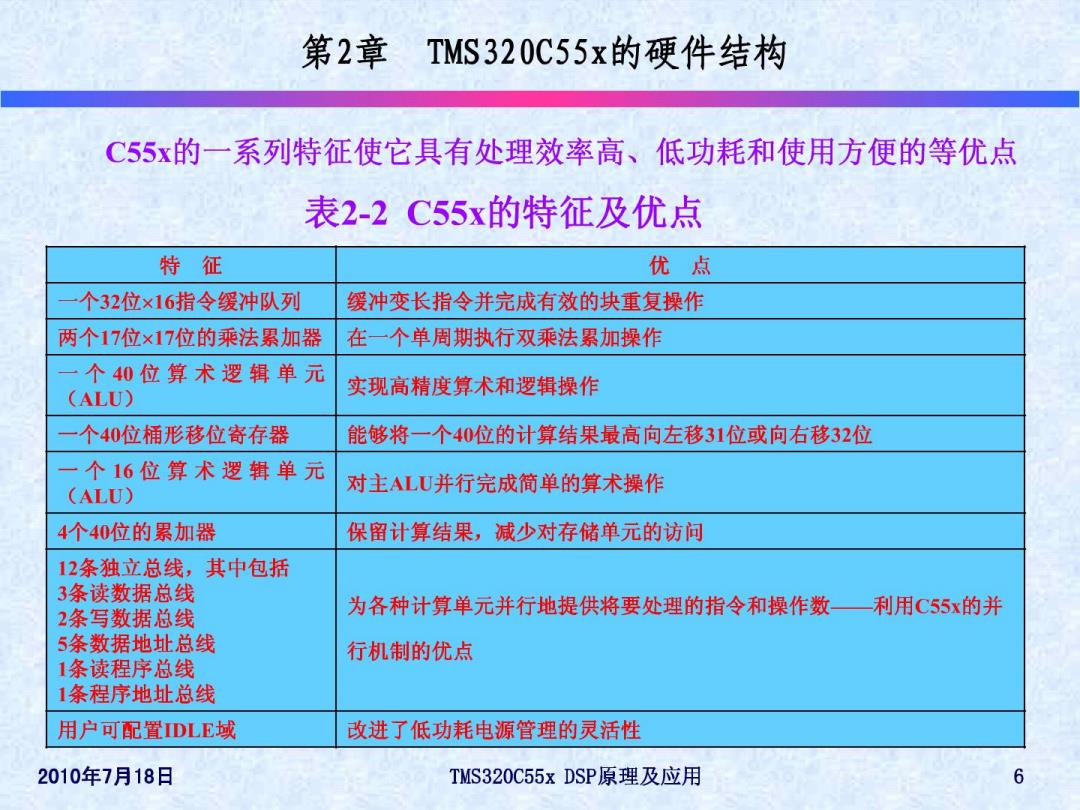

第2章 TMS320C55x的硬件结构 C55x的一系列特征使它具有处理效率高、低功耗和使用方便的等优点 表2-2C55x的特征及优点 特征 优点 一个32位×16指令缓冲队列 缓冲变长指令并完成有效的块重复操作 两个17位×17位的乘法累加器 在一个单周期执行双乘法累加操作 个40位算术逻辑单元 (ALU) 实现高精度算术和逻辑操作 一个40位桶形移位寄存器 能够将一个40位的计算结果最高向左移31位或向右移32位 一 个16位算术逻辑单元 (ALU) 对主ALU并行完成简单的算术操作 4个40位的累加器 保留计算结果,减少对存储单元的访问 12条独立总线,其中包括 3条读数据总线 2条写数据总线 为各种计算单元并行地提供将要处理的指令和操作数一利用C55x的并 5条数据地址总线 行机制的优点 1条读程序总线 1条程序地址总线 用户可配置DLE域 改进了低功耗电源管理的灵活性 2010年7月18日 TMS320C55xDSP原理及应用 6

第2章 TMS320C55x的硬件结构 2.1.1 C55x的CPU体系结构 C55x有1条32位的程序数据总线(PB),5条16位数据总 线 (BB、CB、DB、EB、FB)和1条24位的程序地址总线及5 条23位的数据地址总线,这些总线分别与CPU相连。总线通过 存储器接口单元(M)与外部程序总线和数据总线相连,实现 CPU对外部存储器的访问。这种并行的多总线结构,使CPU能 在一个CPU周期内完成1次32位程序代码读、3次16位数据读和 两次16位数据写。C55x根据功能的不同将CPU分为4个单元, 即指令缓冲单元(I)、程序流程单元(P)、地址流程单元( A)和数据计算单元(D) 2010年7月18日 TMS320C55xDSP原理及应用 7

第2章TMS320C55x的硬件结构 TMS320C55xCPU结构图 数据读数据总线BB,CB,DB(16位) 数据读地址总线BAB,CAB,DAB(23位) 读程序数据总线PB(32位) 读程序地址总线PAB(24位) 外部程序总线 CPU 存储器接口 单元(M) 指令缓冲 程序流程 地址流程 外部数据总线 数据计算 单元(I) 单元(P) 单元(A) 单元(D) 写数据数据总线EB,FB(16位) M 写数据地址总线EAB,FAB(23位) 2010年7月18日 TMS320C55xDSP原理及应用 8

第2章 TMS320C55x的硬件结构 读程序地址总线(PAB)上传送24位的程序代码地址,由读程序数 据总线(PB)将32位的程序代码送入指令缓冲单元I进行译码。 3条读数据地址总线(BAB、CAB、DAB)与3条读数据数据总线( BB、CB、DB)配合使用,即BAB对应BB、CAB对应CB和DAB对应DB 。 地址总线指定数据空间或/O空间地址,通过数据总线将16位数据传送 到CPU的各个功能单元。其中,BB只与D单元相连,用于实现从存储器 到D单元乘法累加器(MAC)的数据传送。特殊的指令也可以同时使用 BB、DB和CB来读取三个操作数。 2条写数据地址总线(EAB、FAB)与两条写数据数据总线(EB、FB )配合使用,即EAB对应EB、FAB对应FB。地址总线指定数据空间或I/O 空间地址,通过数据总线,将数据从CPU的功能单元传送到数据空间或 I/O空间。所有数据空间地址由A单元产生。EB和FB从P单元、A单元和D 单元接收数据,对于同时向存储器写两个16位数据的指令要使用EB和FB ,而对于完成单写操作的指令只使用EB。 2010年7月18日 TMS320C55xDSP原理及应用 9

第2章 TMS320C55x的硬件结构 2.1.2 指令缓冲单元(I) C55x的指令缓冲单元由指 PB 令缓冲队列BQ(Instruction Buffer Queue)和指令译码器组 单元 M单元 成。在每个CPU周期内,I单元 将从读程序数据总线接收的4B 指令 程序代码放入指令缓冲队列,指 缓冲 队列 令译码器从队列中取6B程序代 (64字节) 码,根据指令的长度可对8位、 16位、24位、32位和48位的变长 指令进行译码,然后把译码数据 P单元 指令 送入P单元、A单元和D单元去执 译码 A单元 行。 D单元 指令缓冲单元结构图 2010年7月18日 TMS320C55xDSP原理及应用 10