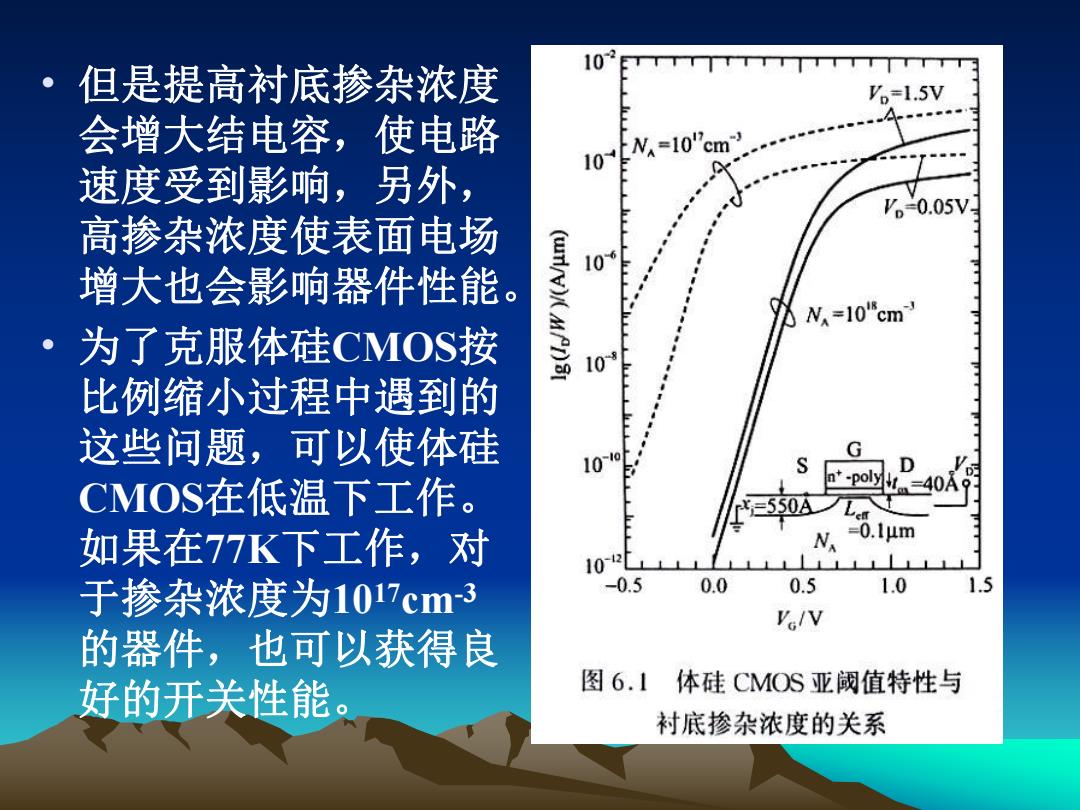

102 但是提高衬底掺杂浓度 '。=l.5V 会增大结电容,使电路 10 M=10"cm 速度受到影响,另外, '。0.05V 高掺杂浓度使表面电场 10 增大也会影响器件性能 N=10“cm 为了克服体硅CMOS按 10 比例缩小过程中遇到的 这些问题,可以使体硅 100 -D0 CMOS在低温下工作。 =550A 如果在77K下工作,对 =0.1μm 10[L 于掺杂浓度为1017cm3 -0.5 0.0 0.5 1.0 1.5 Ve/V 的器件,也可以获得良 好的开关性能 图6.1体硅CMOS亚阈值特性与 衬底掺杂浓度的关系

• 但是提高衬底掺杂浓度 会增大结电容,使电路 速度受到影响,另外, 高掺杂浓度使表面电场 增大也会影响器件性能。 • 为了克服体硅CMOS按 比例缩小过程中遇到的 这些问题,可以使体硅 CMOS在低温下工作。 如果在77K下工作,对 于掺杂浓度为10 17cm-3 的器件,也可以获得良 好的开关性能

另外一种解决途径是采有薄膜全耗尽(FD)SOI器件 图6.2示出了FD SOI器件的结构。由于源、漏区下面是厚 的埋氧化层,使结电容极大地减小。 由于采用很薄的硅膜,在垂直方向的电场有很大变化,引 起水平方向的电势曲率加大,因而有助于建立起电子势垒, 防止电子从源区注入到沟道。这样,通过改变垂直结构控 制水平方向的泄漏电流。 对图6.2所示的SOI MOS器件结构,硅膜中的电势由下述 泊松方程决定:

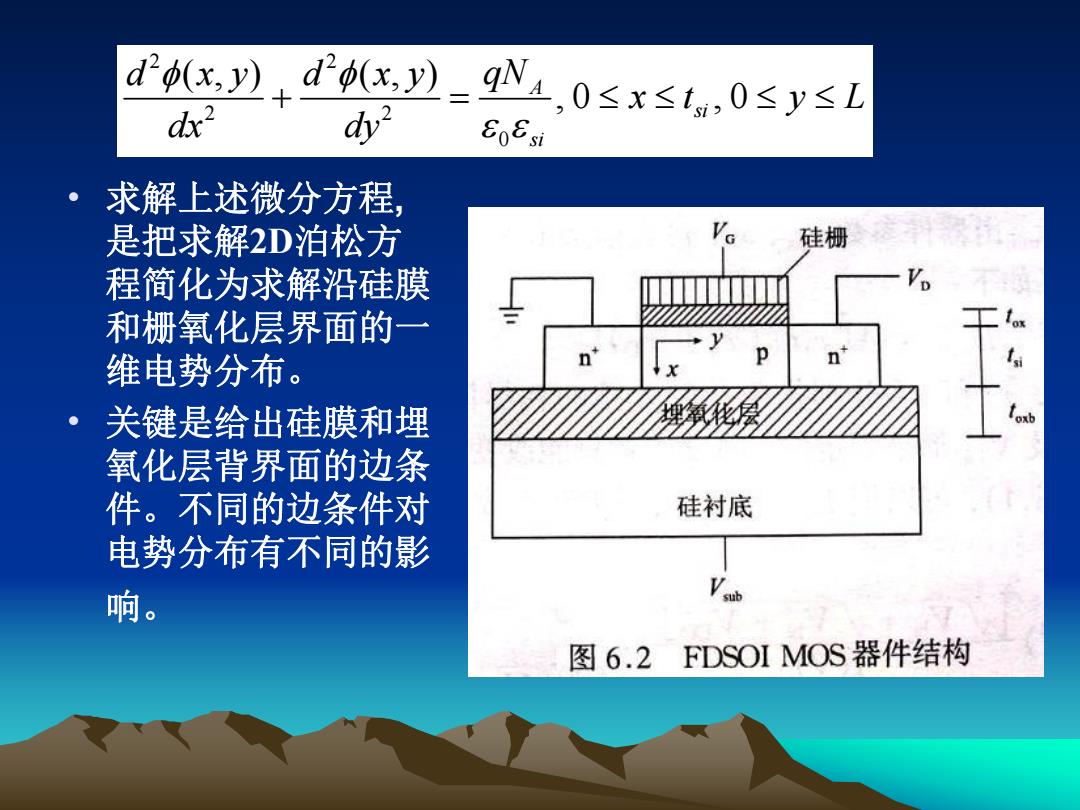

• 另外一种解决途径是采有薄膜全耗尽(FD)SOI器件 • 图6.2示出了FD SOI器件的结构。由于源、漏区下面是厚 的埋氧化层,使结电容极大地减小。 • 由于采用很薄的硅膜,在垂直方向的电场有很大变化,引 起水平方向的电势曲率加大,因而有助于建立起电子势垒, 防止电子从源区注入到沟道。这样,通过改变垂直结构控 制水平方向的泄漏电流。 • 对图6.2所示的SOI MOS器件结构,硅膜中的电势由下述 泊松方程决定:

dx,)+d(x,》_gN4,0≤x≤t,0≤y≤L dx2 dy" EoEsi 求解上述微分方程, 是把求解2D泊松方 硅栅 程简化为求解沿硅膜 和栅氧化层界面的一 n n 1。 维电势分布。 关键是给出硅膜和埋 氧化层背界面的边条 件。不同的边条件对 硅衬底 电势分布有不同的影 响。 sub 图6.2 FDSOI MOS器件结构

• 求解上述微分方程, 是把求解2D泊松方 程简化为求解沿硅膜 和栅氧化层界面的一 维电势分布。 • 关键是给出硅膜和埋 氧化层背界面的边条 件。不同的边条件对 电势分布有不同的影 响。 2 2 2 2 0 ( , ) ( , ) , 0 , 0 A si si d x y d x y qN x t y L dx dy

要减小水平方向的泄漏电流,需要较大的源沟道之间的 电势差,即电势水平方向有较大的曲率。 由二维泊松方程看出有两个途径增大电势水平方向的曲率: 1、提高沟道区掺杂浓度N;2、通过改变-db/dx2来增大 水平方向的电势曲率,也就是要获得一个陡变的纵向电场。 在漏电压V较小时,沿x方向(纵向)的电势分布可以用 简单的抛物线函数描述,即 (x,y)co(y)+c(y)x+c2(y)x 其中参数cy)、c,y)和c2y)仅仅是y的函数

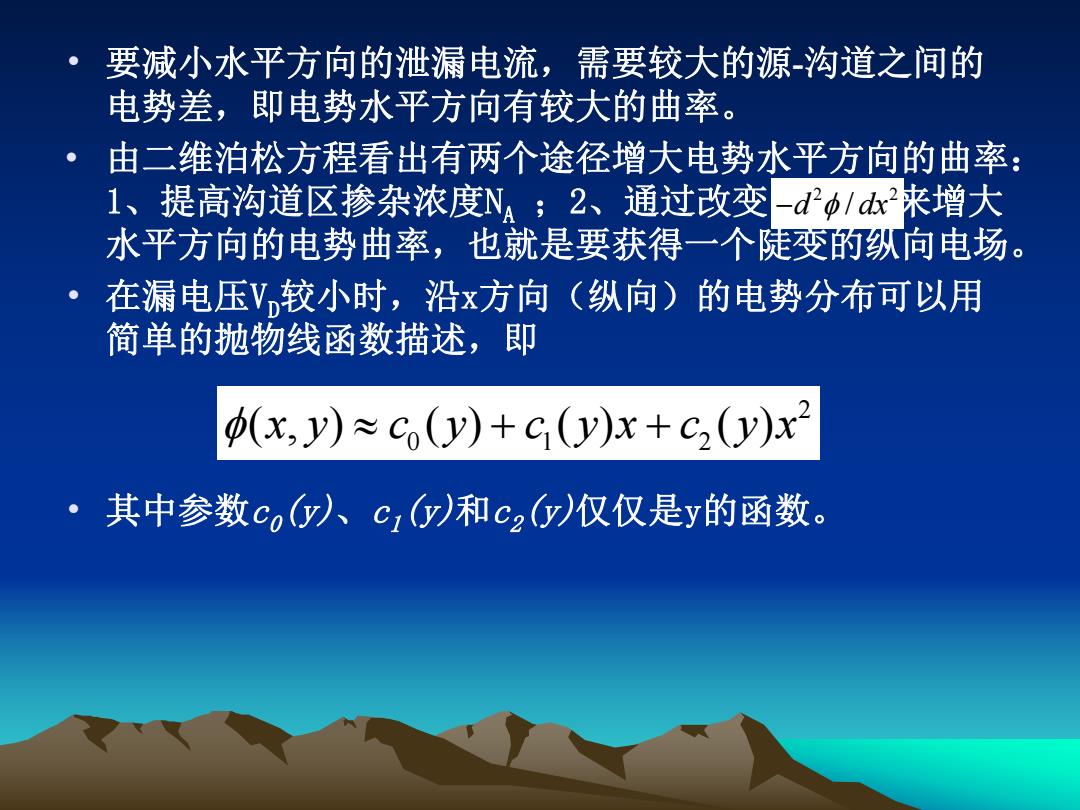

• 要减小水平方向的泄漏电流,需要较大的源-沟道之间的 电势差,即电势水平方向有较大的曲率。 • 由二维泊松方程看出有两个途径增大电势水平方向的曲率: 1、提高沟道区掺杂浓度NA ;2、通过改变 来增大 水平方向的电势曲率,也就是要获得一个陡变的纵向电场。 • 在漏电压VD较小时,沿x方向(纵向)的电势分布可以用 简单的抛物线函数描述,即 • 其中参数c0(y)、c1(y)和c2(y)仅仅是y的函数。 2 2 d / dx 2 0 1 2 (x, y) c (y) c (y)x c (y)x

E(ev) SOURCE p DRAIN MOSFET的能带 n+ EFn EFn GATE V>0 DEPLETION REGION DRAIN VOSFET的电势 VG>VT GATE VD>0 分布 SOURCE U+ b

• MOSFET的电势 分布 MOSFET的能带