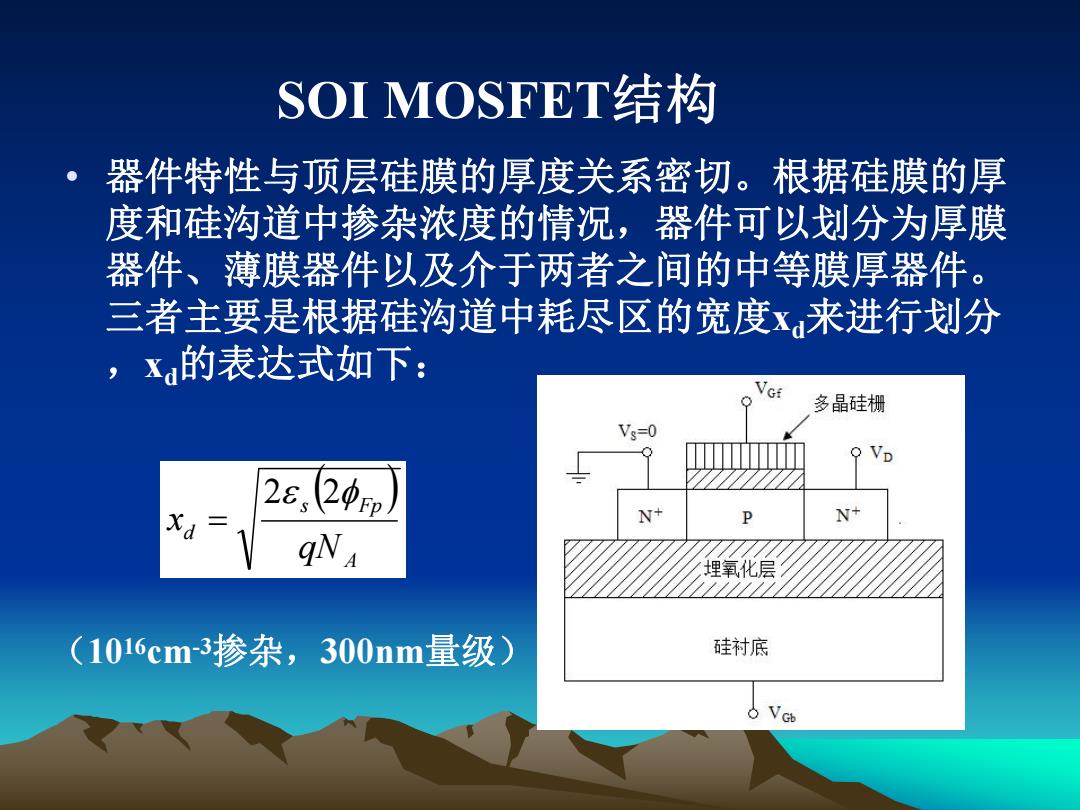

SOI MOSFET结构 器件特性与顶层硅膜的厚度关系密切。根据硅膜的厚 度和硅沟道中掺参杂浓度的情况,器件可以划分为厚膜 器件、薄膜器件以及介于两者之间的中等膜厚器件。 三者主要是根据硅沟道中耗尽区的宽度x,来进行划分 ,x的表达式如下: 多晶硅栅 Vs=0 2c,2φm N+ 埋氧化层 (1016cm-3掺杂,300nm量级) 硅衬底

• 器件特性与顶层硅膜的厚度关系密切。根据硅膜的厚 度和硅沟道中掺杂浓度的情况,器件可以划分为厚膜 器件、薄膜器件以及介于两者之间的中等膜厚器件。 三者主要是根据硅沟道中耗尽区的宽度xd来进行划分 ,xd的表达式如下: SOI MOSFET结构 A s Fp d qN x 2 2 (10 16cm-3掺杂,300nm量级)

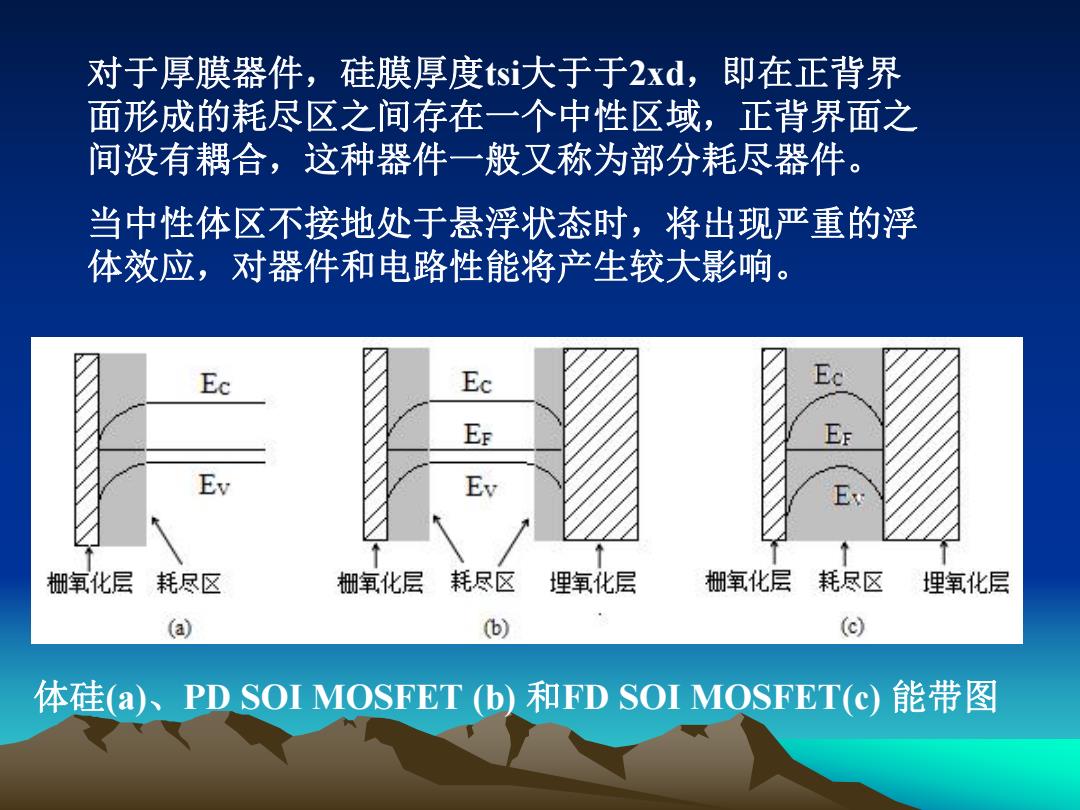

对于厚膜器件,硅膜厚度tsi大于于2xd,即在正背界 面形成的耗尽区之间存在一个中性区域,正背界面之 间没有耦合,这种器件一般又称为部分耗尽器件。 当中性体区不接地处于悬浮状态时,将出现严重的浮 体效应,对器件和电路性能将产生较大影响。 Ec Ec Er Er Ev Ev 栅氧化层 耗尽区 栅氧化层 耗尽区 埋氧化层 栅氧化层 耗尽区 埋氧化层 (a) (b) (c) 体硅(a)、PD SOI MOSFET(b)和FD SOI MOSFET(c能带图

对于厚膜器件,硅膜厚度tsi大于于2xd,即在正背界 面形成的耗尽区之间存在一个中性区域,正背界面之 间没有耦合,这种器件一般又称为部分耗尽器件。 当中性体区不接地处于悬浮状态时,将出现严重的浮 体效应,对器件和电路性能将产生较大影响。 体硅(a)、PD SOI MOSFET (b) 和FD SOI MOSFET(c) 能带图

对于薄膜器件,硅膜厚度~小于于xd,当器件开启时, 硅膜处于全耗尽状态(除去由于背栅偏压使背界面处于 积累或反型情况),通常将这种器件称为全耗尽器件 FDSOI MOSFET 全耗尽器件器件具有较高的电流驱动能力,陡直的亚 阈值斜率,较小的短沟道和窄沟道效应及Kink效应。 硅膜厚度处于厚膜和薄膜之间的器件称作中等膜厚器件, 根据不同背栅偏置电压,呈现出不同特性。在适当的背界 面栅压下正背界面耗尽区不会发生交叠,背栅界面呈现出 积累或中性,则该器件呈现厚膜器件特性;如果适当的背 栅压下正背界面耗尽区发生交叠,硅膜呈现全耗尽状态, 则器件呈现薄膜器件特性

• 对于薄膜器件,硅膜厚度~小于于xd,当器件开启时, 硅膜处于全耗尽状态(除去由于背栅偏压使背界面处于 积累或反型情况),通常将这种器件称为全耗尽器件 FDSOI MOSFET 。 • 全耗尽器件器件具有较高的电流驱动能力,陡直的亚 阈值斜率,较小的短沟道和窄沟道效应及Kink效应。 • 硅膜厚度处于厚膜和薄膜之间的器件称作中等膜厚器件, 根据不同背栅偏置电压,呈现出不同特性。在适当的背界 面栅压下正背界面耗尽区不会发生交叠,背栅界面呈现出 积累或中性,则该器件呈现厚膜器件特性;如果适当的背 栅压下正背界面耗尽区发生交叠,硅膜呈现全耗尽状态, 则器件呈现薄膜器件特性

SOI CMOS等比例缩小理论 考虑到对器件截止态电流的限制,要使缩小后的器 件仍具有较好的亚阈值特性,则器件的有效沟道长 度必须大于一个最小值Lmin。 Lmin由器件参数tx、x, 衬底掺杂浓度N,和电源电 压决定,Lmin和器件参数的关系如下: min =A[x,t(x,+xD)2]Ψ3 其中,4=(0.41A)x和x,分别是源、漏pn结的耗尽 区宽度。针对一定工艺,Letr,to和x,以及Vpn都 是固定的,则设计者只能改变衬底参杂浓度N,来满 足要求,即

• 考虑到对器件截止态电流的限制,要使缩小后的器 件仍具有较好的亚阈值特性,则器件的有效沟道长 度必须大于一个最小值Lmin 。 • Lmin由器件参数t ox、xj,衬底掺杂浓度NA和电源电 压决定,Lmin和器件参数的关系如下: • 其中, xs和xD分别是源、漏pn结的耗尽 区宽度。针对一定工艺,Leff,tox和xj,以及VDD都 是固定的,则设计者只能改变衬底掺杂浓度NA来满 足要求,即 2 1/ 3 min [ ( ) ] L A j ox s D x t x x 1/ 3 A (0.41A)

W,≥1.8×107(emV+V+yo 0.1(um) 1(V) 500(A) 40(A) 这就意味着,对于 0=0.lum,1m=40A,x,=500A 的技术, 在1V电源电压下,符展疹东张度安达到1018cm3 图6.1说明了衬底掺杂浓度对体硅CM0S亚阈值特性 的影响。针对给定的器件参数 、 0.1um,tom=40A,x=550A,'oD =1.5V/ 则N4=10”cm时不能获得满意的亚阈值特性,掺 杂浓度必须增大到1018cm3

• 这就意味着,对于 的技术, 在1V电源电压下,衬底掺杂浓度要达到10 18cm-3 。 • 图6.1说明了衬底掺杂浓度对体硅CMOS亚阈值特性 的影响。针对给定的器件参数 • 则 时不能获得满意的亚阈值特性,掺 杂浓度必须增大到10 18cm -3 。 2 17 3 [ ] 0.1( ) 1.8 10 ( ) 1( ) 500( ) 40( ) bi bi DD j ox A ef V V V x m t N cm V L A A 0.1 , 40 , 500 Lef m ox j t A x A 0.1 , 40 , 550 , 1.5 L ef m ox j DD t A x A V V 17 3 10 NA cm