数字电子技术.第3章组合逻辑电路 教学目标: 1、理解半加器和全加器的基本原理。 2、掌握加法器的设计方法 3、掌握数值比较器的原理和基本设计方法 教学重点: 加法器、数值比较器的原理和计方法。 教学难点: 全加器构成多位加法器。 3.2.1加法器 一、半加器和全加器 l.半加器(Half Adder): 半加器逻辑状态表 A B S C 逻辑表达式 0000 0110 S=AB+AB=A⊕B 1010 1101 C=AB 曲 逻纸图 2.全加器(Full Adder) 一一考虑来自低位的进位, ()列逻辑状态表 A B Ci-1 S:C. 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 0 1 1 1 1 1 1 (2)写出逻辑式

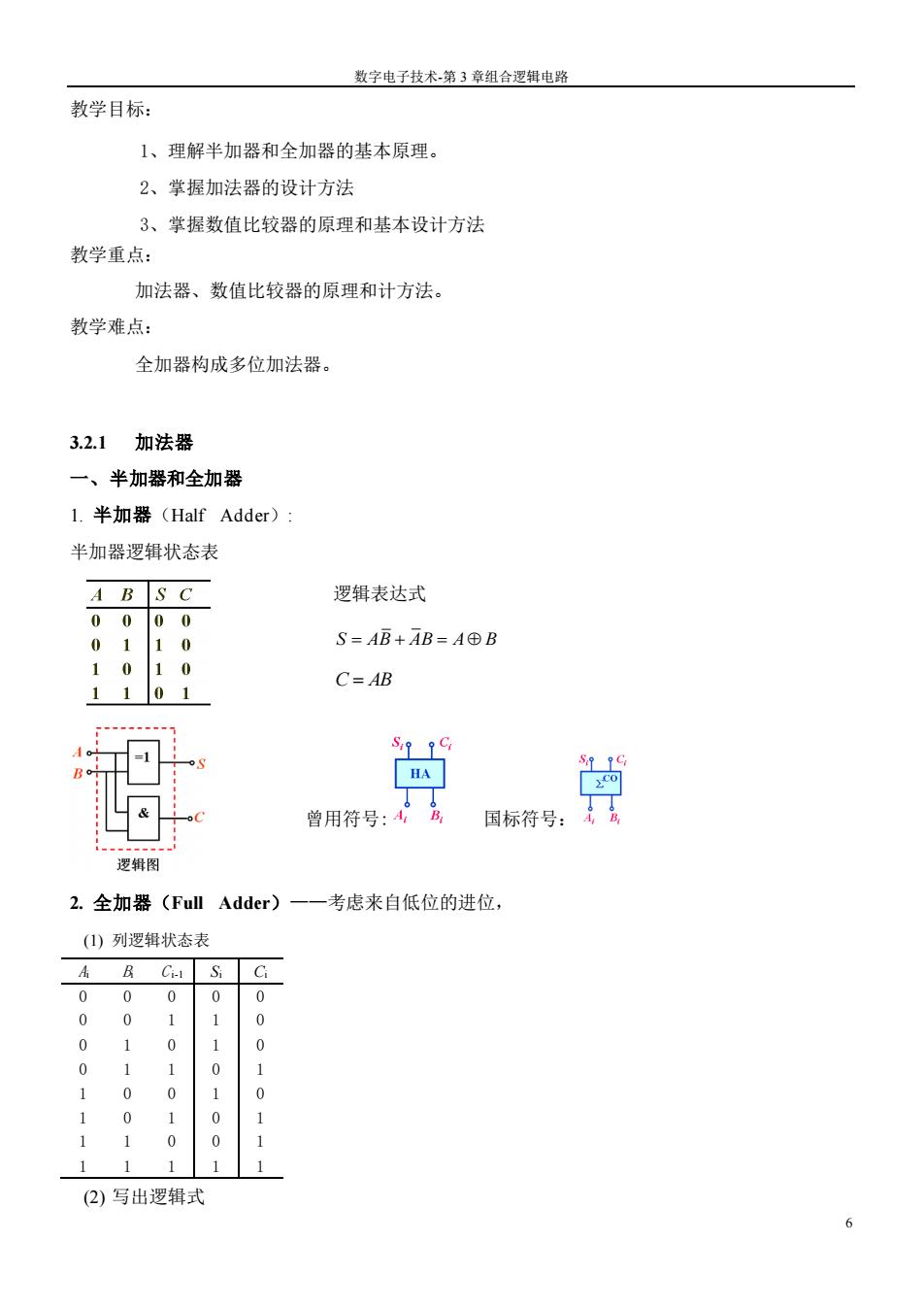

数字电子技术-第 3 章组合逻辑电路 6 教学目标: 1、理解半加器和全加器的基本原理。 2、掌握加法器的设计方法 3、掌握数值比较器的原理和基本设计方法 教学重点: 加法器、数值比较器的原理和计方法。 教学难点: 全加器构成多位加法器。 3.2.1 加法器 一、半加器和全加器 1. 半加器(Half Adder): 半加器逻辑状态表 2. 全加器(Full Adder)——考虑来自低位的进位, (1) 列逻辑状态表 Ai Bi C i-1 Si Ci 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 (2) 写出逻辑式 逻辑表达式 S AB AB A B = + = C AB = 曾用符号: 国标符号:

数字电子技术第3章组合逻辑电路 S=4BC.+BC.+4BC+4BC C=4B+4C+B.C 用与或非门和非门实现逻辑图 FA 电电 曾用号: 国标符号: 3.集成全加器 将2个上图封装在一个器件中,就构成了双全加器。 双全加器TTL:74LS183 CMOS:C661 外引线功能端排列图P153图3.2.5 二、加法器(Adder) 1.4位串行进位加法器 2.超前进位加法器 作加法运算时,总进位信号由输入二进制数直接产生。 优点:速度快 缺点:电路比较复杂 3.2.2数值比较器(Digital Comparator) 一、1位数值比较器 L(A>B) 1位 oG(A=B) B:0 比较器 °M(A<B) 二、4位数值比较器 真值表 7

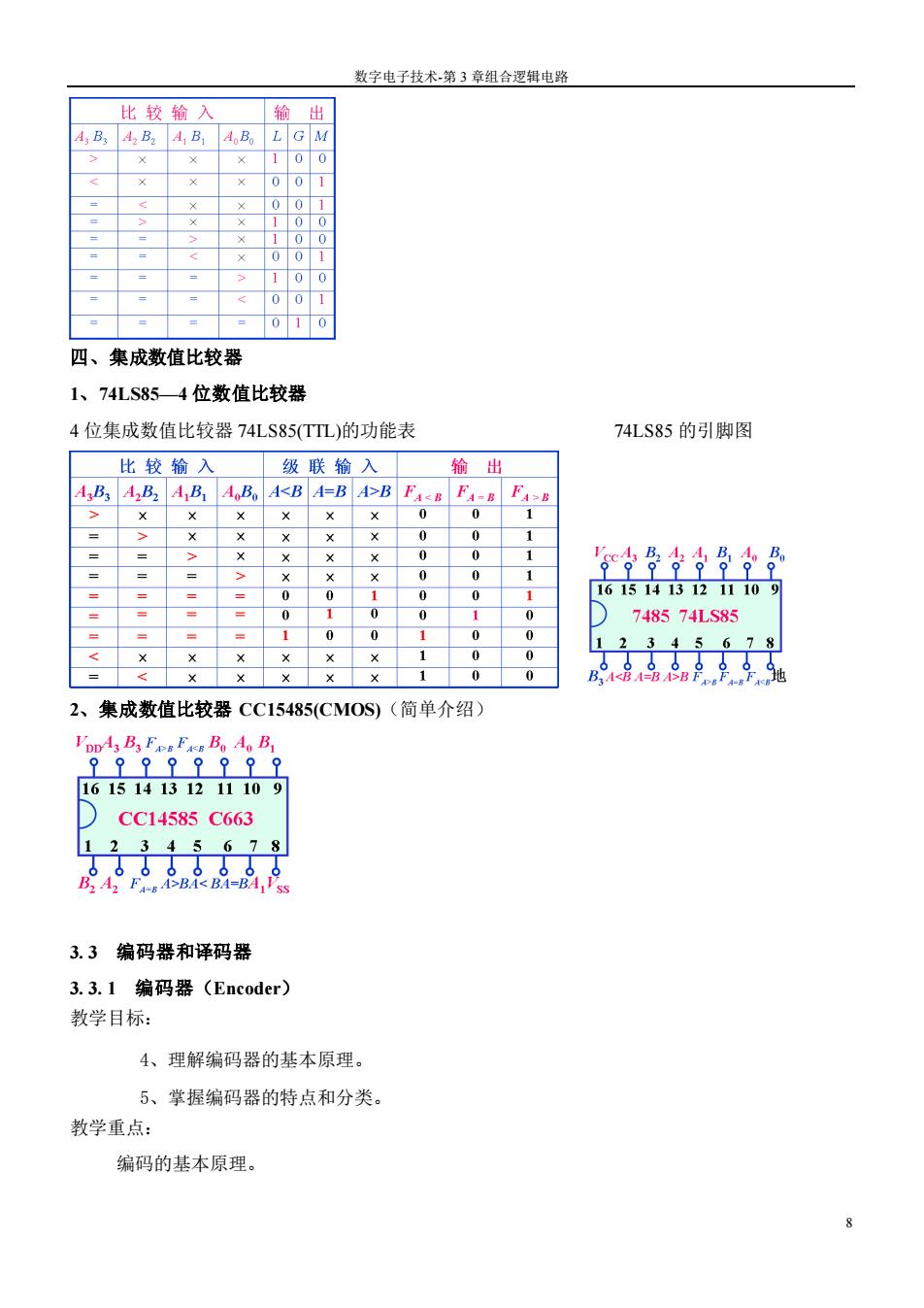

数字电子技术-第 3 章组合逻辑电路 7 i i i i i i i i i i i i i 1 1 1 1 S ABC ABC ABC ABC = + + + − − − − C A B AC B C i i i i i i i = + + − − 1 1 用与或非门和非门实现逻辑图 3. 集成全加器 将 2 个上图封装在一个器件中,就构成了双全加器。 双全加器 TTL:74LS183 CMOS:C661 外引线功能端排列图 P153 图 3.2.5 二、加法器(Adder) 1. 4 位串行进位加法器 2. 超前进位加法器 作加法运算时,总进位信号由输入二进制数直接产生。 优点:速度快 缺点:电路比较复杂 3. 2. 2 数值比较器(Digital Comparator) 一、1 位数值比较器 二、4 位数值比较器 真值表 曾用符号: 国标符号:

数字电子技术第3章组合逻辑电路 比较输入 输出 4B4B24B,AB。LGM 01 010 四、集成数值比较器 1、74LS854位数值比较器 4位集成数值比较器74LS85TL)的功能表 74LS85的引脚图 比较输入 级联输入 输出 AB 4Bs AB.AB A<B A-B AB F-a Fa "g受令台8令品 16151413121110可 748574L585 0 12345678 1 0 <×100 2、集成数值比较器CC15485(CMOS)(简单介绍) 'DDA3B3 Fes F&B。AoB 99999999 161514131211109 DCC14585C663 12345678 8n品品品 B:A F 3.3编码器和译码器 3.3.1编码器(Encoder) 教学目标: 4、理解编码器的基本原理。 5、掌握编码器的特点和分类。 教学重点: 编码的基本原理

数字电子技术-第 3 章组合逻辑电路 8 四、集成数值比较器 1、74LS85—4 位数值比较器 4 位集成数值比较器 74LS85(TTL)的功能表 74LS85 的引脚图 2、集成数值比较器 CC15485(CMOS)(简单介绍) 3. 3 编码器和译码器 3. 3. 1 编码器(Encoder) 教学目标: 4、理解编码器的基本原理。 5、掌握编码器的特点和分类。 教学重点: 编码的基本原理