K康芯科技 4.1 Quartusll-设计流程 5.时序仿真 ps 5.12us 10.24us 15.36us 20.48us 25.6us 30.72us 39 Name Value at 10.55ns 10.55ns CLK B0 W RST CoUT 司 团C9 图4-15设置好的激励波形图

KX 康芯科技 4.1 QuartusII设计流程 图4-15 设置好的激励波形图 5.时序仿真

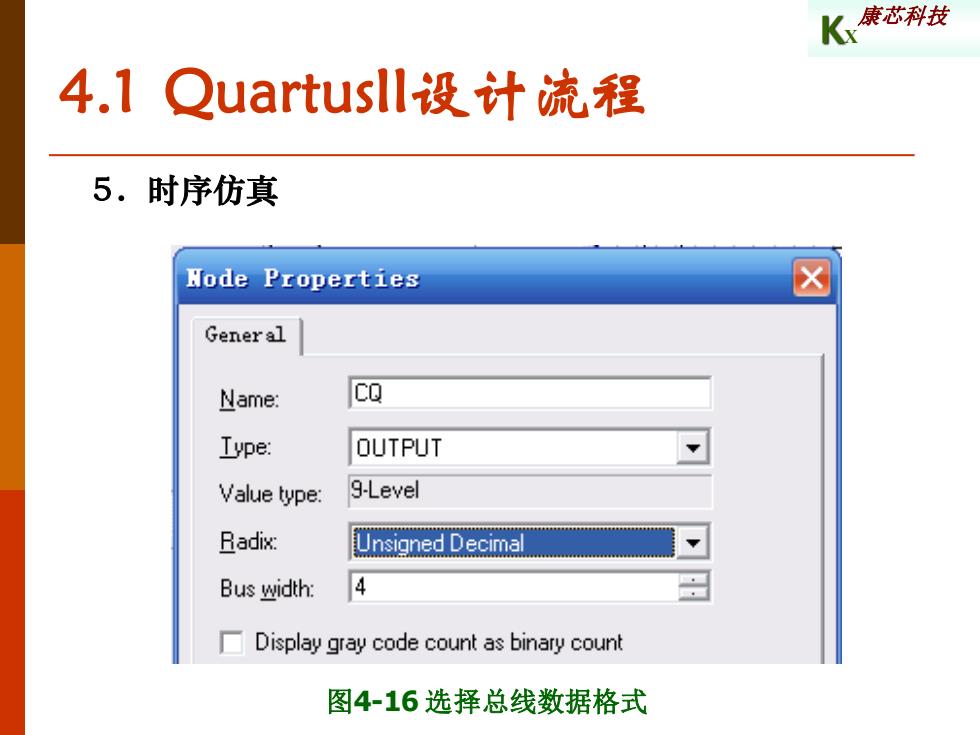

K康芯科技 4.1 Quartusll-设计流程 5.时序仿真 Node Properties ☒ General Name: ca Type: OUTPUT Value type: 9-Level Radix: Unsigned Decimal Bus width: 4 ■ Display gray code count as binary count 图4-16选择总线数据格式

KX 康芯科技 4.1 QuartusII设计流程 图4-16 选择总线数据格式 5.时序仿真

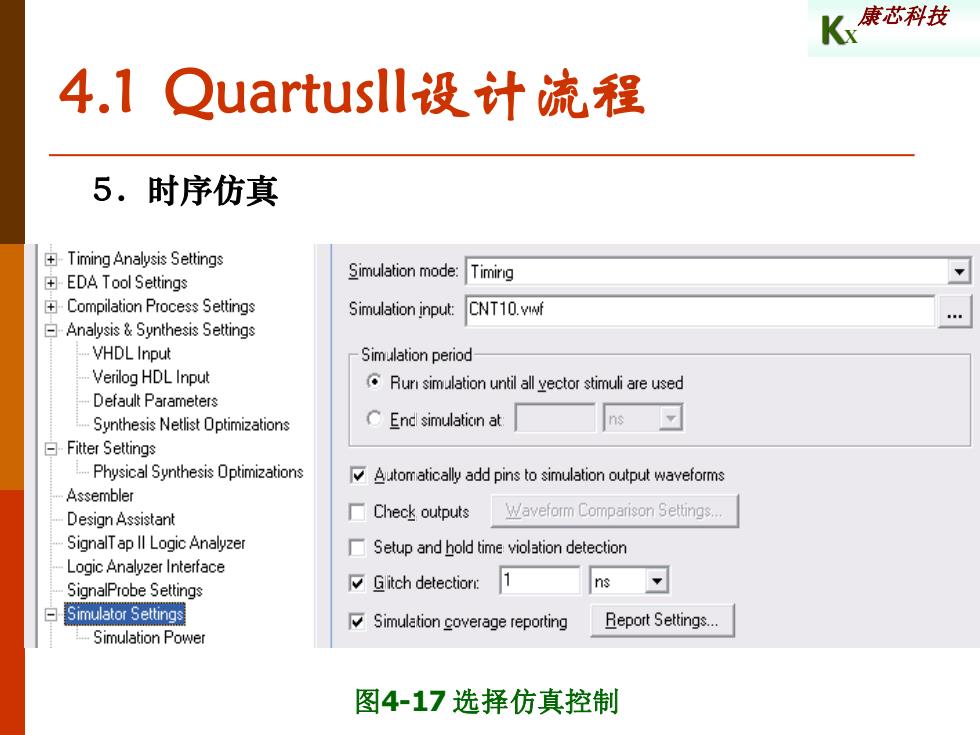

K康芯科技 4.1 Quartusll-设计流程 5.时序仿真 Timing Analysis Settings EDA Tool Settings Simulation mode:Timing Compilation Process Settings Simulation input: CNT10.vwf Analysis&Synthesis Settings VHDL Input Simulation period Verilog HDL Input Rur simulation until all yector stimuli are used Default Parameters Synthesis Netlist Optimizations Endl simulaticin at ns 已-Fitter Settings Physical Synthesis Optimizations Automatically add pins to simulation output waveforms Assembler Design Assistant 口 Check outputs Waveform Comparison Settings. SignalTap ll Logic Analyzer Setup and hold time violation detection Logic Analyzer Interface SignalProbe Settings Gitch detectior: 1 Simulator Settings Simulation coverage reporting Report Settings. Simulation Power 图4-17选择仿真控制

KX 康芯科技 4.1 QuartusII设计流程 图4-17 选择仿真控制 5.时序仿真

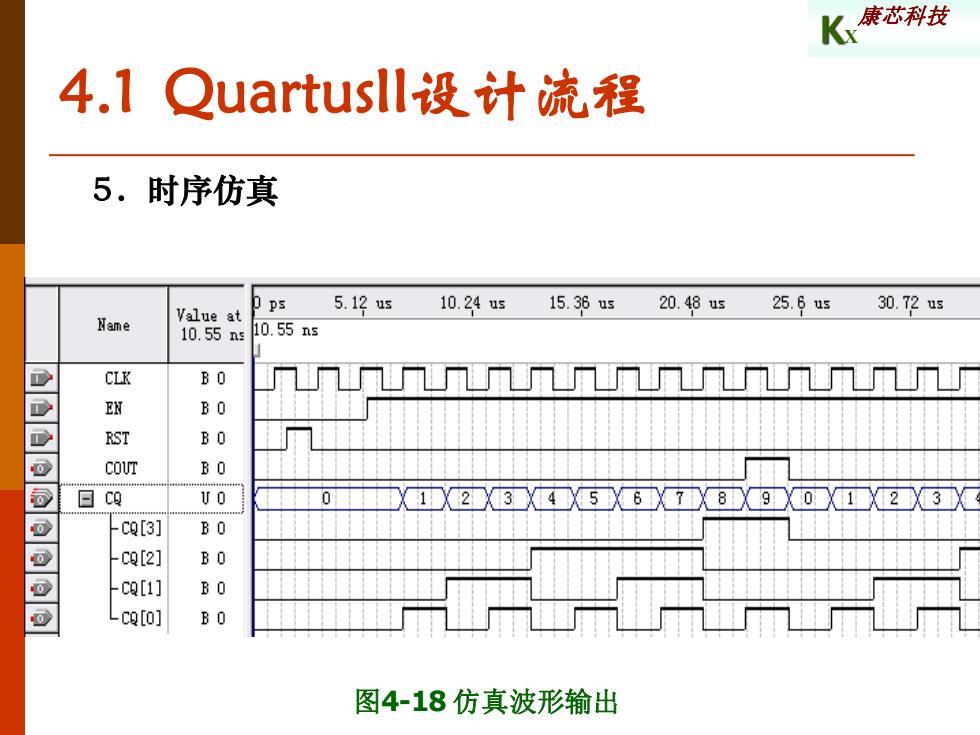

K能芯科技 4.1 Quartusll-设计流程 5.时序仿真 ps 5.12us 10.24us 15.36us 20.48us 25.6us 30.72us Name Value at 10.55ns 10.55ns CLK B0 EN B0 RST B0 回 CovT B0 司 日C9 U O 1 @ -CQ[3] B0 -CQ[2] BO 可 -C9[1] BO 可 Lco[o] B0 图4-18仿真波形输出

KX 康芯科技 4.1 QuartusII设计流程 图4-18 仿真波形输出 5.时序仿真

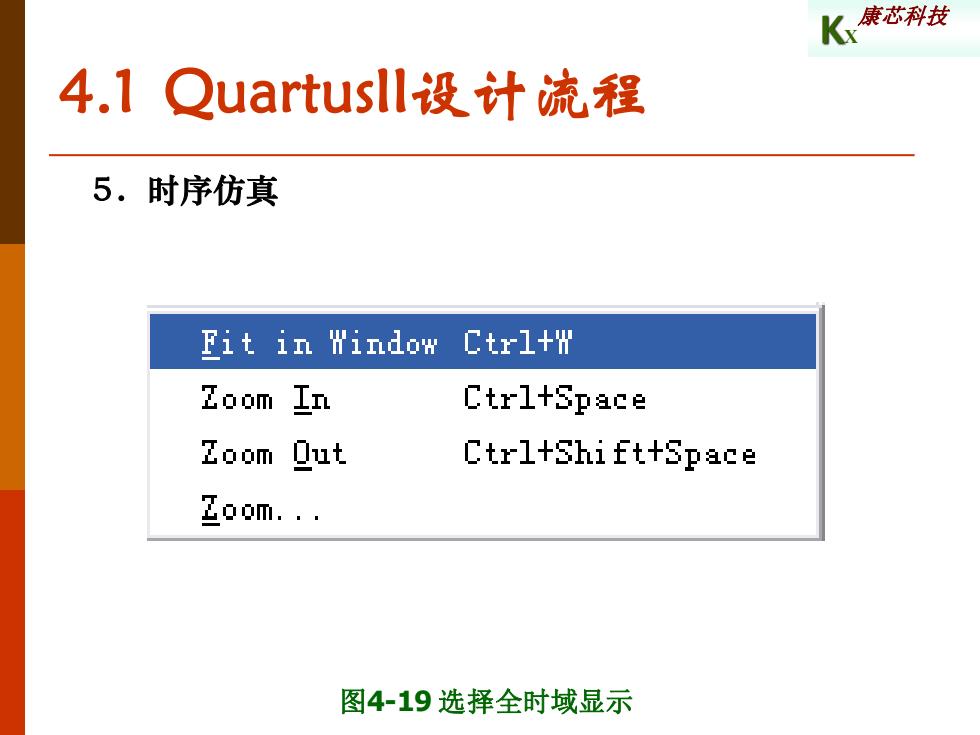

K康还科技 4.1 Quartusll-设计流程 5.时序仿真 Fit in Window Ctrl+ Zoom In Ctrl+Space Zoom 01t Ctrl+Shift+Space Zoom. 图4-19选择全时域显示

KX 康芯科技 4.1 QuartusII设计流程 图4-19 选择全时域显示 5.时序仿真