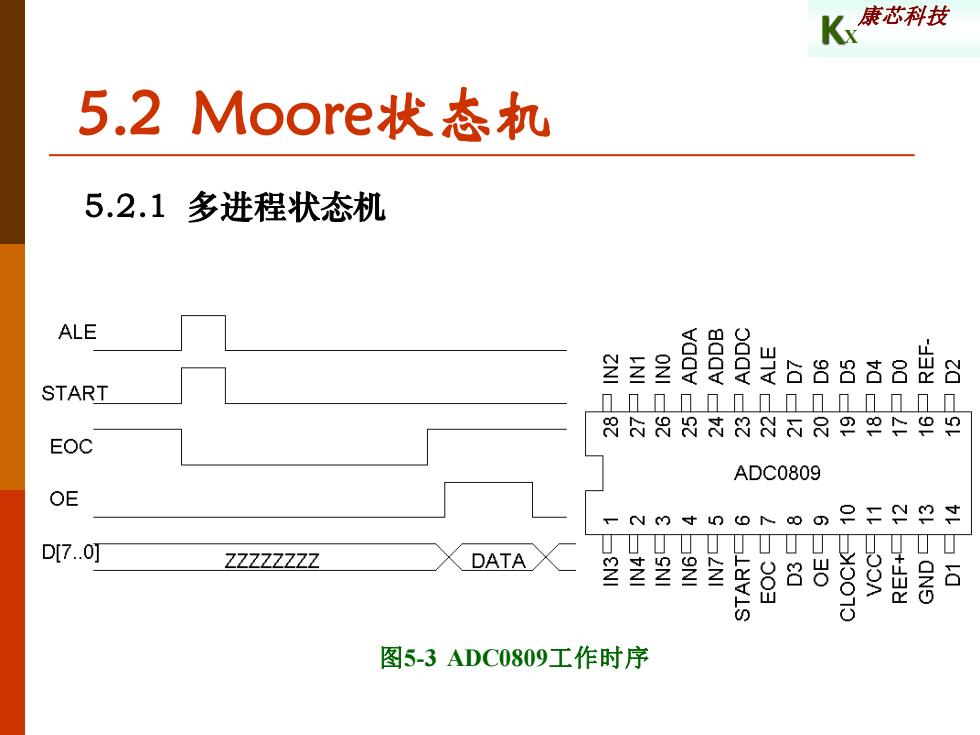

K康还科技 5.2 Aoore状态机 5.2.1多进程状态机 ALE 兰2 員員 山 合88吝8臣8 START 11010111111101 8☆8R88PFP EOC ADC0809 OE -NM寸noNo 只F92寸 D7.0 DATA UUUUUJUUUUILU 77777777 2毫 9 888 6 图5-3ADC0809工作时序

KX 康芯科技 5.2 Moore状态机 5.2.1 多进程状态机 图5-3 ADC0809工作时序

K能芯科拉 5.2 Moore状态机 5.2.1多进程状态机 sto 对0809初始化 LOCK:0->1 由LOCK信号锁存 st4 转换好的数据 st1 启动AVD转换 OE='11 数据输出有效 采样周期中等待 st3 st2 EOC1'转换结束 EOC=0'正在转换 图5-4控制ADC0809采样状态图

KX 康芯科技 5.2 Moore状态机 5.2.1 多进程状态机 图5-4 控制ADC0809采样状态图

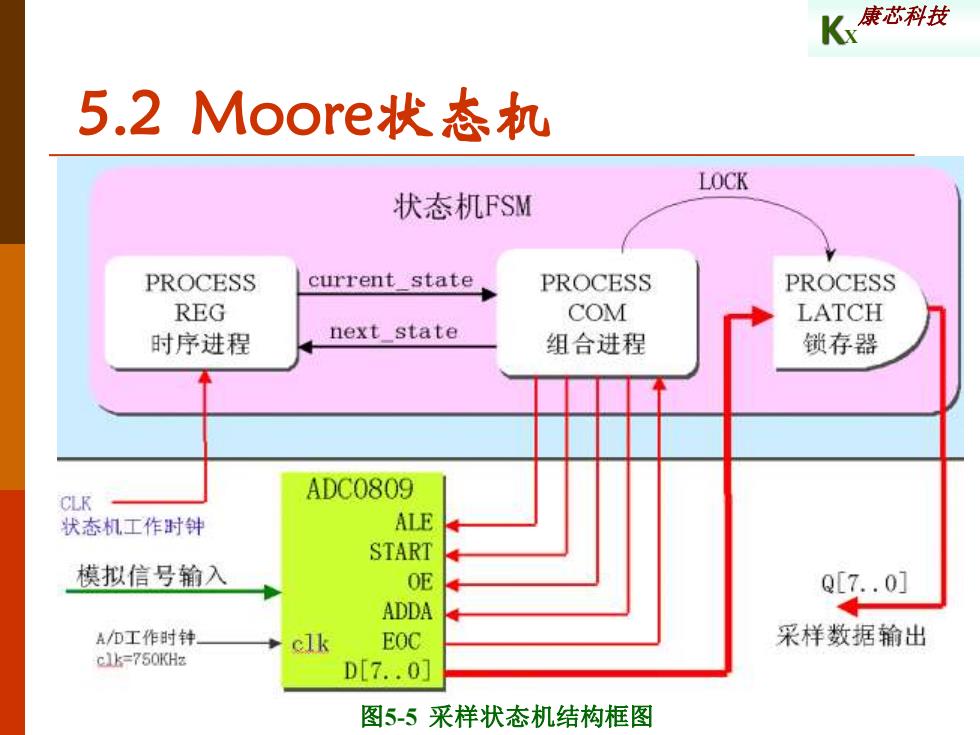

K康还科技 5.2 Moore状态机 LOCK 状态机FSM PROCESS current state PROCESS PROCESS REG COM LATCH 时序进程 nextstate 组合进程 锁存器 ADC0809 CLK 状态机工作时钟 ALE START 模拟信号输入 OE Q[7.0] ADDA A/D工作时钟 clk EOC 采样数据输出 clk=750KHz D[7.0] 图5-5采样状态机结构框图

KX 康芯科技 5.2 Moore状态机 5.2.1 多进程状态机 图5-5 采样状态机结构框图

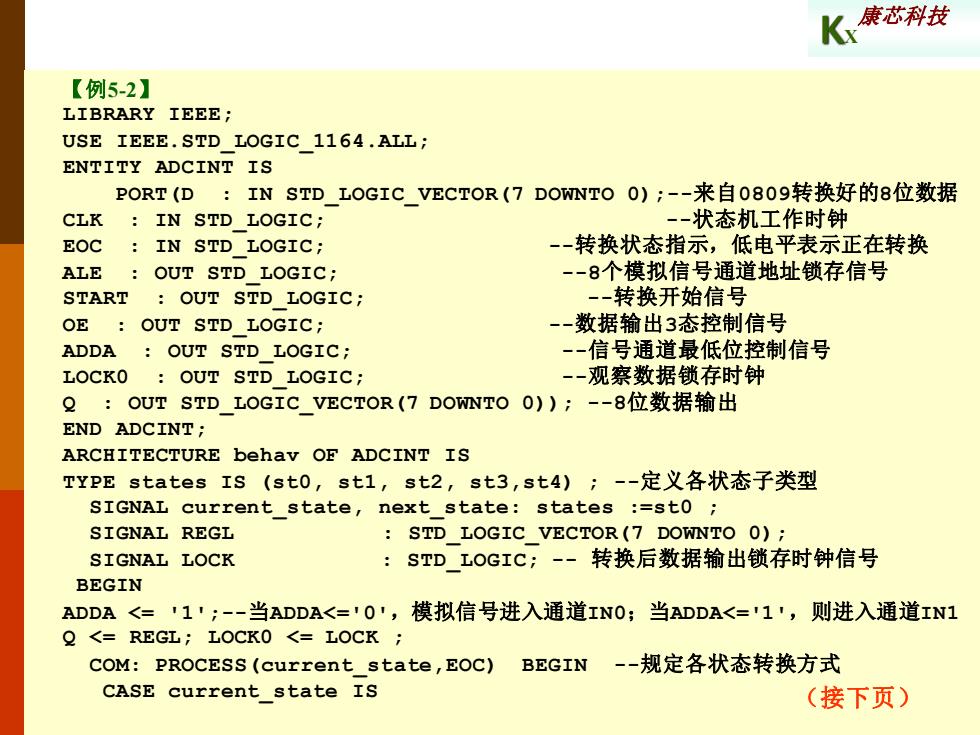

K能恋科技 【例5-2】 LIBRARY IEEE; USE IEEE.STD LOGIC 1164.ALL; ENTITY ADCINT IS PORT(D:IN STD_LOGIC VECTOR(7 DOWNTO 0);-来自0809转换好的8位数据 CLK IN STD LOGIC; -状态机工作时钟 EOC IN STD LOGIC; -转换状态指示,低电平表示正在转换 ALE OUT STD LOGIC; -8个模拟信号通道地址锁存信号 START OUT STD LOGIC; -转换开始信号 OE OUT STD LOGIC; -数据输出3态控制信号 ADDA OUT STD LOGIC; -信号通道最低位控制信号 LOCKO OUT STD LOGIC; -观察数据锁存时钟 Q:OUT STD LOGIC VECTOR(7 DOWNTO0));-8位数据输出 END ADCINT; ARCHITECTURE behav OF ADCINT IS TYPE states Is(st0,st1,st2,st3,st4);-定义各状态子类型 SIGNAL current state,next state:states :=st0 SIGNAL REGL STD LOGIC VECTOR(7 DOWNTO 0); SIGNAL LOCK :STD LOGIC;-转换后数据输出锁存时钟信号 BEGIN ADDA<=·1';-当ADDA<='0',模拟信号进入通道IN0;当ADDA<='1',则进入通道IN1 Q <REGL;LOCKO <LOCK COM:PROCESS(current state,EOC)BEGIN-规定各状态转换方式 CASE current state IS (接下页)

KX 康芯科技 【例5-2】 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY ADCINT IS PORT(D : IN STD_LOGIC_VECTOR(7 DOWNTO 0);-来自0809转换好的8位数据 CLK : IN STD_LOGIC; -状态机工作时钟 EOC : IN STD_LOGIC; -转换状态指示,低电平表示正在转换 ALE : OUT STD_LOGIC; -8个模拟信号通道地址锁存信号 START : OUT STD_LOGIC; -转换开始信号 OE : OUT STD_LOGIC; -数据输出3态控制信号 ADDA : OUT STD_LOGIC; -信号通道最低位控制信号 LOCK0 : OUT STD_LOGIC; -观察数据锁存时钟 Q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); -8位数据输出 END ADCINT; ARCHITECTURE behav OF ADCINT IS TYPE states IS (st0, st1, st2, st3,st4) ; -定义各状态子类型 SIGNAL current_state, next_state: states :=st0 ; SIGNAL REGL : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL LOCK : STD_LOGIC; - 转换后数据输出锁存时钟信号 BEGIN ADDA <= '1';-当ADDA<='0' ,模拟信号进入通道IN0;当ADDA<='1' ,则进入通道IN1 Q <= REGL; LOCK0 <= LOCK ; COM: PROCESS(current_state,EOC) BEGIN -规定各状态转换方式 CASE current_state IS (接下页)

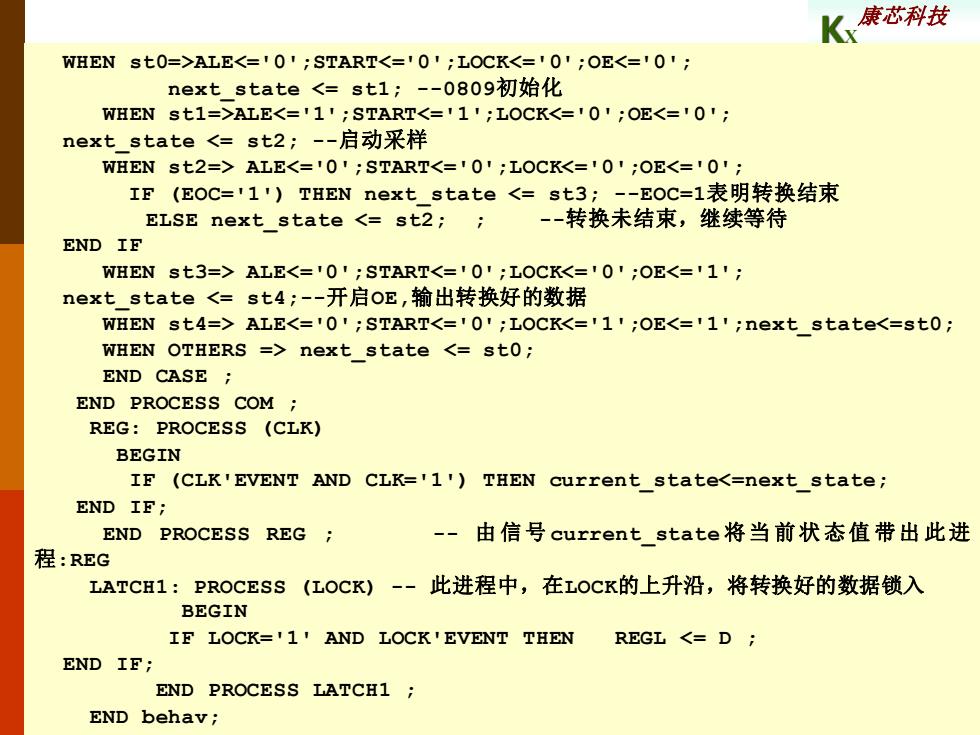

K康芯科技 WHEN stO=>ALE<=0;START<=0;LOCK<=0;OE<='0; next state<=st1;-0809初始化 WHEN st1=>ALE<='1 ;START<=1;LOCK<=0';OE<=0; next_state<=st2;-启动采样 WHEN st2=>ALE<=10;START<=0;LOCK<=0OE<=0; IE(EOC='1')THEN next state<=st3;-EOC=l表明转换结束 ELSE next_state<=st2;;-转换未结束,继续等待 END IF WHEN st3=>ALE<=0;START<=0;LOCK<=0;OE<=1; next_state<=st4;-开启oE,输出转换好的数据 WHEN st4=>ALE<=10';START<='0';LOCK<='1';OE<='1';next state<=st0; WHEN OTHERS =next_state <st0; END CASE END PROCESS COM REG:PROCESS (CLK) BEGIN IF (CLK'EVENT AND CLK='1')THEN current state<=next state; END IF; END PROCESS REG -由信号current_state将当前状态值带出此进 程:REG LATCH1:PROCESS(LOCK)-此进程中,在LOCK的上升沿,将转换好的数据锁入 BEGIN IF LOCK=1 AND LOCK EVENT THEN REGL <D END IF; END PROCESS LATCH1; END behav;

KX 康芯科技 WHEN st0=>ALE<='0';START<='0';LOCK<='0';OE<='0'; next_state <= st1; -0809初始化 WHEN st1=>ALE<='1';START<='1';LOCK<='0';OE<='0'; next_state <= st2; -启动采样 WHEN st2=> ALE<='0';START<='0';LOCK<='0';OE<='0'; IF (EOC='1') THEN next_state <= st3; -EOC=1表明转换结束 ELSE next_state <= st2; ; -转换未结束,继续等待 END IF WHEN st3=> ALE<='0';START<='0';LOCK<='0';OE<='1'; next_state <= st4;-开启OE,输出转换好的数据 WHEN st4=> ALE<='0';START<='0';LOCK<='1';OE<='1';next_state<=st0; WHEN OTHERS => next_state <= st0; END CASE ; END PROCESS COM ; REG: PROCESS (CLK) BEGIN IF (CLK'EVENT AND CLK='1') THEN current_state<=next_state; END IF; END PROCESS REG ; - 由 信号 current_state 将当 前状 态值 带出 此进 程:REG LATCH1: PROCESS (LOCK) - 此进程中,在LOCK的上升沿,将转换好的数据锁入 BEGIN IF LOCK='1' AND LOCK'EVENT THEN REGL <= D ; END IF; END PROCESS LATCH1 ; END behav;