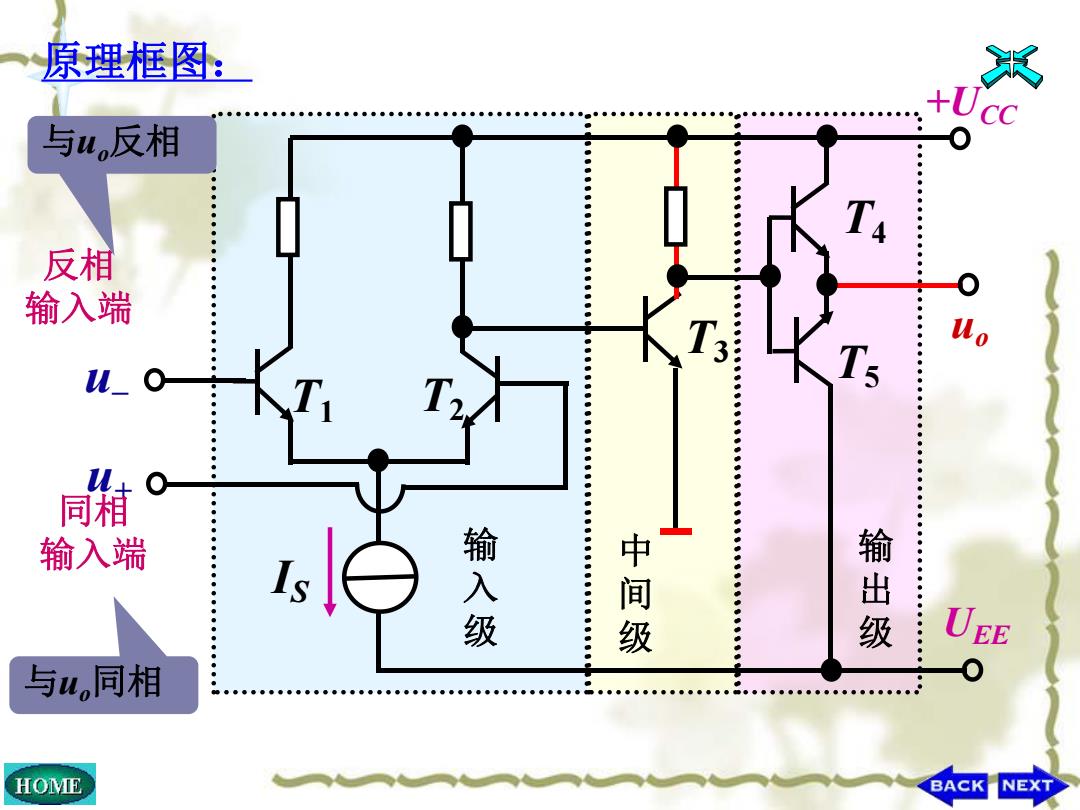

原理框图: +U 与u,反相 反相 输入端 W_ 同相 输入端 输入级 中 级 输出级 UEE 与u同相 HOME BACK NEXT

UEE +UCC u+ uo u– 反相 输入端同相 输入端 T3 T4 T5 T1 T2 IS 原理框图: 输入级 中间级 输出级 与uo反相 与uo同相

汉 集成运放的结构 (1)输入级和第二级一般采用差动放大器。采用 复合三极管或场效应管,以减小输入电流, 增加输入电阻。 (2)中间级采用四级以上的共发射极放大器。 (3)输出级采用互补对称式射极跟随器,以进行 功率放大,提高带负载的能力。 HOME BACK NEXT

集成运放的结构 (1)输入级和第二级一般采用差动放大器。采用 复合三极管或场效应管,以减小输入电流, 增加输入电阻。 (2)中间级采用四级以上的共发射极放大器。 (3)输出级采用互补对称式射极跟随器,以进行 功率放大,提高带负载的能力

二、一集成运放的主要性能指标 汉 1.开环差模电压放大倍数K 无外加反馈回路的差模放大倍数。一般在 105~107(或60~100dB)之间。理想运放 的K为o。 2.共模抑制比CMRR 常用分贝作单位,一般100dB以上。 3.输入阻抗r >1M2,有的可达100M2以上。 4.输出阻抗1。 r。=几2-几十2。 HOME BACK NEXT

⒈ 开环差模电压放大倍数Kd 无外加反馈回路的差模放大倍数。一般在 10 5 10 7(或60~100dB)之间。理想运放 的Kd为。 ⒉ 共模抑制比CMRR 常用分贝作单位,一般100dB以上。 ⒊ 输入阻抗ri ri>1M, 有的可达100M以上。 ⒋ 输出阻抗ro ro =几-几十。 二、集成运放的主要性能指标

5.输入失调电压U 汉 反映了运放差动输入级的对称程度,失调电压 越大,运放的对称性越差。一般为毫伏级。 6.输入失调电流Is 由差动输入级两个晶体管B值不一致所引起的。 其他反映运放对称性、零漂等的参数。 HOME BACK NEXT

⒌ 输入失调电压Uis ⒍ 输入失调电流Iis 其他反映运放对称性、零漂等的参数。 反映了运放差动输入级的对称程度,失调电压 越大,运放的对称性越差。一般为毫伏级。 由差动输入级两个晶体管β值不一致所引起的

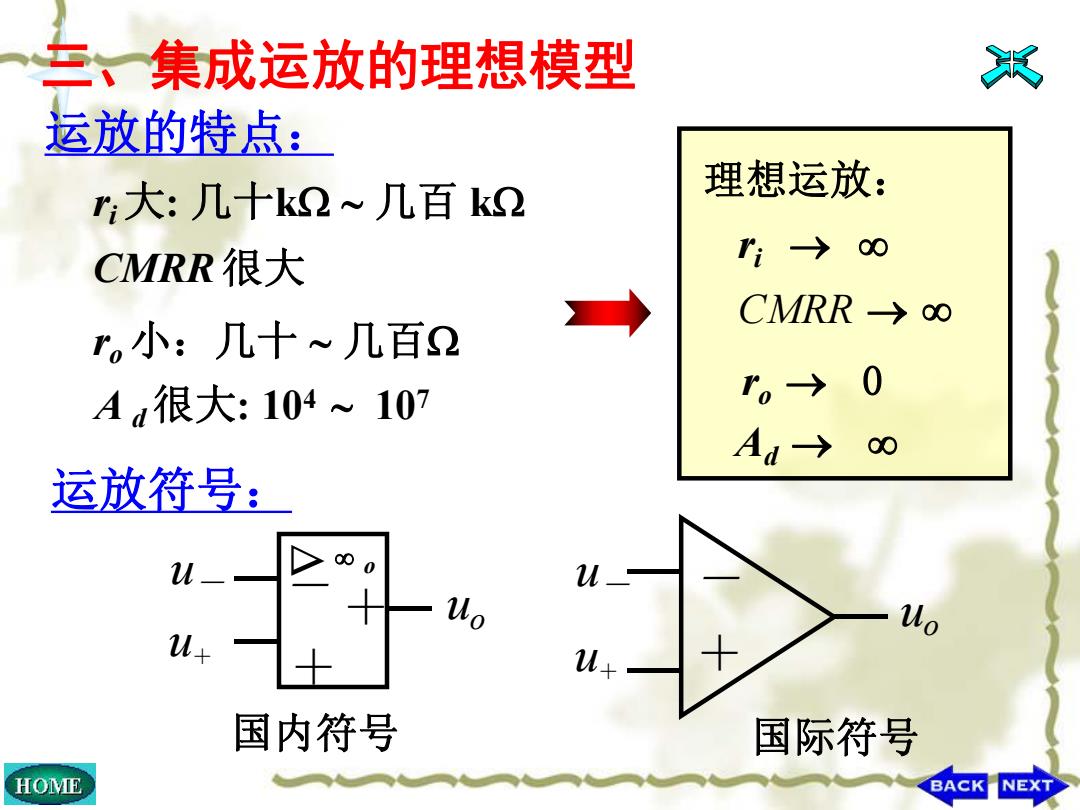

三、集成运放的理想模型 汉 运放的特点: :大:几十k2~几百k2 理想运放: CMRR很大 ':〉00 CMRR→oo r。小:几十心几百2 A,很大:104心107 ro-> 0 Aa→ 运放符号: u 00 + u+ 国内符号 国际符号 HOME BACK NEXT

ri大: 几十k 几百 k 运放的特点: CMRR很大 ro小:几十 几百 A d很大: 10 4 10 7 理想运放: ri CMRR ro 0 Ad 运放符号: + u- - u+ uo - + + u- u+ uo o 国内符号 国际符号 三、集成运放的理想模型