4.5触发器的VHDL描述及其仿真

4.5 触发器的VHDL描述及其仿真

例4.5.1同步D触发器的VHDL描述和仿真 ✉D冈I d_ff.scf-Waveform Editor =▣x Ref: 0.0ns ▣Time:O.0ns Interval:0.0ns 0.0ns Name: Value: 100.0ns200.0ns300.0ns400.0ns500.0ns600.0ns700.0ns800.0ns900.0ns1 reset 1 工d 0 工-ck 0 -@q 0 PROCESS (clk) BEGIN IF cIk'EVENT AND clk='1'THEN IF reset='1'THEN QK='0'; ELSE q<=d; END IF; END IF: END PROCESS; END one;

[例4.5.1] 同步D触发器的VHDL描述和仿真 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY d_ff is PORT (d,clk,reset : IN STD_LOGIC; q : OUTSTD_LOGIC); END d_ff; ARCHITECTURE one OF d_ff IS BEGIN PROCESS (clk) BEGIN IF clk'EVENT AND clk='1' THEN IF reset='1' THEN Q<='0'; ELSE q<=d; END IF; END IF; END PROCESS; END one;

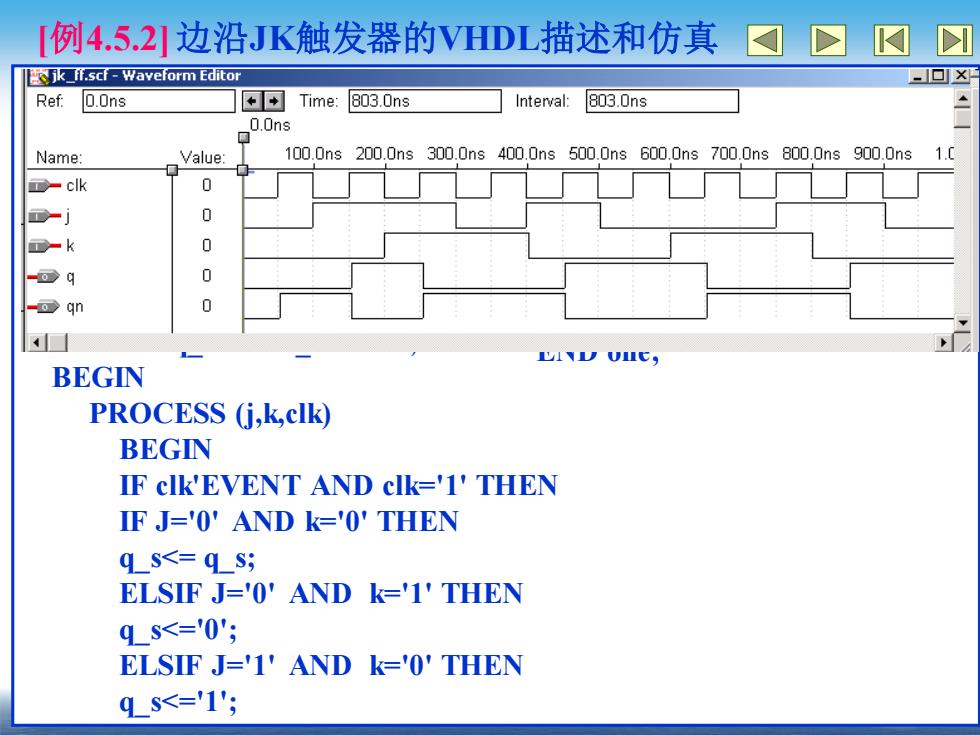

[例4.5.2]边沿JK触发器的VDL描述和仿真 jk_ff.scf Waveform Editor ▣X Ref: 0.0ns ✉+Time:83.0ns Interval: 803.0ns 0.Ons Name: Value: 100.0ns200.0ns300.0ns400.0ns500.0ns600.0ns700.0ns800.0ns900.0ns1.C 工-clk 0 工=j Dk 0 q 0 qn 0 心D UnC) BEGIN PROCESS (j,k,clk) BEGIN IF clk'EVENT AND clk='1'THEN IF J='0'AND k='0'THEN q_s<=qs; ELSIF J='0'AND k='1'THEN qs<='0'; ELSIF J='1'AND k='0'THEN qs<='1';

[例4.5.2] 边沿JK触发器的VHDL描述和仿真 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY jk_ff is PORT (j,k,clk : IN STD_LOGIC; q, qn : OUT STD_LOGIC); END jk_ff; ARCHITECTURE one OF jk_ff IS SIGNAL q_s : STD_LOGIC; BEGIN PROCESS (j,k,clk) BEGIN IF clk'EVENT AND clk='1' THEN IF J='0' AND k='0' THEN q_s<= q_s; ELSIF J='0' AND k='1' THEN q_s<='0'; ELSIF J='1' AND k='0' THEN q_s<='1'; ELSIF J='1' AND k='1' THEN q_s<=NOT q_s; END IF; END IF; END PROCESS; q<=q_s; qn<=not q_s; END one;