K康芯科技 3.2时序电路描述 3.信号定义和数据对象 4.上升沿检测表式和信号属性函数EVENT <信号名>'EVENT 5.不完整条件语句与时序电路

KX 康芯科技 3.2 时序电路描述 3. 信号定义和数据对象 <信号名>'EVENT 4. 上升沿检测表式和信号属性函数EVENT 5. 不完整条件语句与时序电路

K康还科技 3.2附序电路描述 【例3-7】 ENTITY COMP BAD IS PORT(a1,b1 IN BIT; q1 OUT BIT ) END; ARCHITECTURE one OF COMP BAD IS BEGIN PROCESS(a1,b1) BEGIN IF al>b1 THEN q1<='1'; ELSIF a1<b1 THEN q1<='O';-未提及当a1=b1时,ql作何操作 END IF; END PROCESS; END;

KX 康芯科技 3.2 时序电路描述 【例3-7】 ENTITY COMP_BAD IS PORT( a1,b1 : IN BIT; q1 : OUT BIT ); END ; ARCHITECTURE one OF COMP_BAD IS BEGIN PROCESS (a1,b1) BEGIN IF a1 > b1 THEN q1 <= '1' ; ELSIF a1 < b1 THEN q1 <= '0' ;- 未提及当a1=b1时,q1作何操作 END IF; END PROCESS ; END ;

K能苏科技 3.2附序电路描述 latrs D 915 0 Q 91 91_1 a 11 图3-5例3-7的电路图

KX 康芯科技 3.2 时序电路描述 图3-5 例3-7的电路图

K康还科技 3.2附序电路描述 【例3-8】 IF al b1 THEN ql <1; ELSE ql <=0 END IF; q1 a 图3-6例3-8的电路图

KX 康芯科技 3.2 时序电路描述 图3-6 例3-8的电路图 【例3-8】 . IF a1 > b1 THEN q1 <= '1' ; ELSE q1 <= '0' ; END IF;

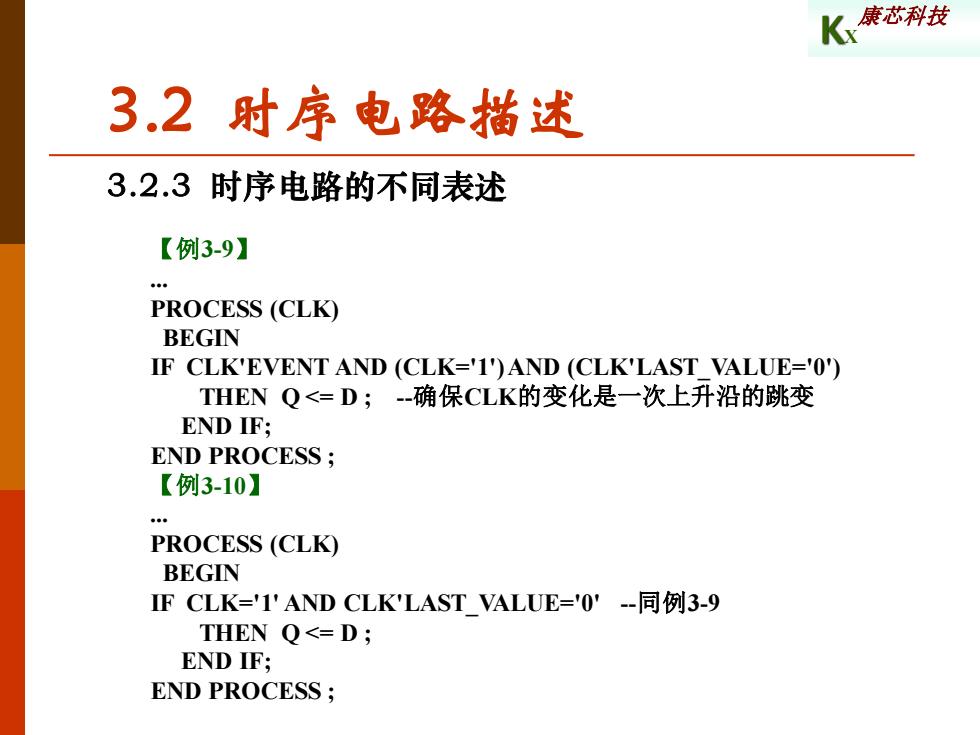

K能苏科技 3.2时序电路描述 3.2.3时序电路的不同表述 【例3-9】 PROCESS (CLK) BEGIN IF CLK'EVENT AND(CLK-'1)AND(CLK'LAST VALUE=0) THEN Q<=D;-确保CLK的变化是一次上升沿的跳变 END IF; END PROCESS 【例3-10】 PROCESS (CLK) BEGIN FCLK='1'AND CLK'LAST_VALUE='O'-同例3-9 THEN Q<=D; END IF; END PROCESS;

KX 康芯科技 3.2 时序电路描述 3.2.3 时序电路的不同表述 【例3-9】 . PROCESS (CLK) BEGIN IF CLK'EVENT AND (CLK='1')AND (CLK'LAST_VALUE='0') THEN Q <= D ; -确保CLK的变化是一次上升沿的跳变 END IF; END PROCESS ; 【例3-10】 . PROCESS (CLK) BEGIN IF CLK='1' AND CLK'LAST_VALUE='0' -同例3-9 THEN Q <= D ; END IF; END PROCESS ;