K康科技 3.1VHDL基本语法 9.条件语句 10.WHEN_ELSE条件信号赋值语句 赋值目标<=表达式WHEN赋值条件ELSE 表达式WHEN赋值条件ELSE ● 表达式; z<= a WHEN p1 =1 ELSE b WHEN p2 =1 ELSE

KX 康芯科技 3.1 VHDL 基本语法 9. 条件语句 10. WHEN_ELSE条件信号赋值语句 赋值目标 <= 表达式 WHEN 赋值条件 ELSE 表达式 WHEN 赋值条件 ELSE . 表达式 ; z <= a WHEN p1 = '1' ELSE b WHEN p2 = '1' ELSE c ;

K康芯科技 3.1VHDL基本语法 11.进程语句和顺序语句 IF THEN ELSE END IF; PROCESS.END PROCESS 12.文件取名和存盘 “vhd” adder f.vhd

KX 康芯科技 3.1 VHDL 基本语法 11. 进程语句和顺序语句 12. 文件取名和存盘 IF_THEN_ELSE_END IF; PROCESS. END PROCESS “ .vhd” adder_f.vhd

K康还科技 3.2附序电路描述 3.2.1D触发器 【例3-6】 LIBRARY IEEE USE IEEE.STD LOGIC 1164.ALL ENTITY DFF1 IS PORT (CLK IN STD LOGIC; D:IN STD LOGIC DFF1 Q:OUT STD LOGIC ) END 图3-4D触发器 ARCHITECTURE bhv OF DFF1 IS SIGNAL Q1:STD工OGIC;-类似于在芯片内部定义一个数据的暂存节点 BEGIN PROCESS (CLK,Q1) BEGIN IF CLK'EVENT AND CLK=1 THEN Q1 <=D; END IF; END PROCESS 9<=91; -一将内部的暂存数据向端口输出(双横线-是注释符号) END bhv;

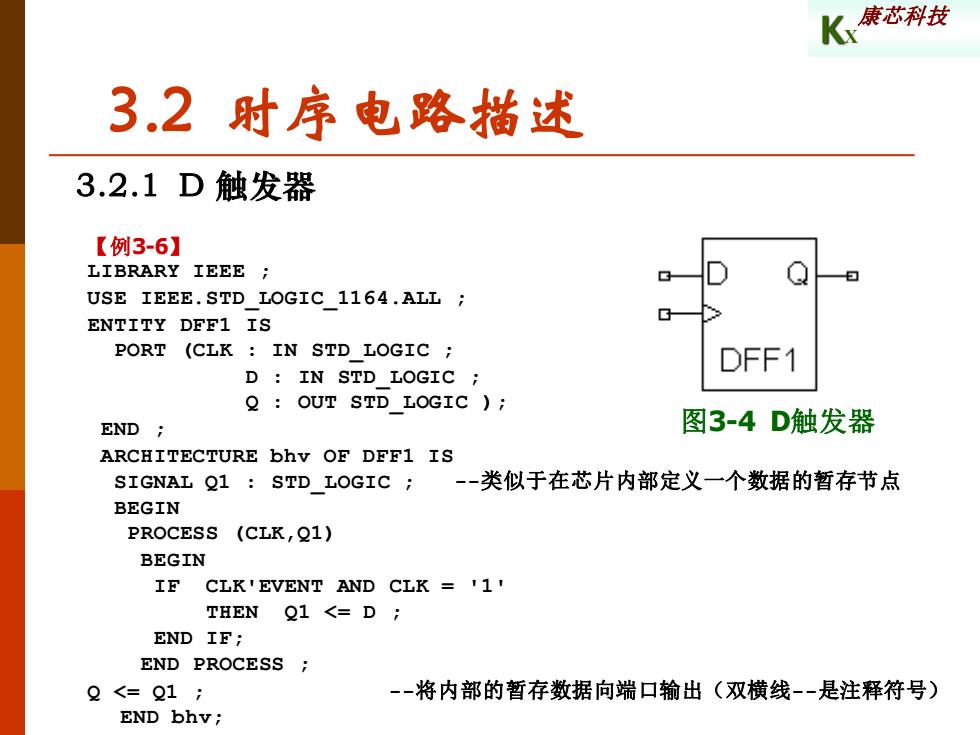

KX 康芯科技 3.2 时序电路描述 3.2.1 D 触发器 【例3-6】 LIBRARY IEEE ; USE IEEE.STD_LOGIC_1164.ALL ; ENTITY DFF1 IS PORT (CLK : IN STD_LOGIC ; D : IN STD_LOGIC ; Q : OUT STD_LOGIC ); END ; ARCHITECTURE bhv OF DFF1 IS SIGNAL Q1 : STD_LOGIC ; -类似于在芯片内部定义一个数据的暂存节点 BEGIN PROCESS (CLK,Q1) BEGIN IF CLK'EVENT AND CLK = '1' THEN Q1 <= D ; END IF; END PROCESS ; Q <= Q1 ; -将内部的暂存数据向端口输出(双横线-是注释符号) END bhv; 图3-4 D触发器

K科技 3.2时序电路描述 3.2.2时序描述VHDL规则 1.标准逻辑位数据类型STD_LOGIC BIT数据类型定义: TYPE BIT IS(O','1):-只有两种取值 STD_LOGIC数据类型定义: TYPE STD._LOGIC IS('U',X','0','1','Z','"W','L','H','-)i-有9种取值

KX 康芯科技 3.2 时序电路描述 3.2.2 时序描述VHDL规则 1. 标准逻辑位数据类型 STD_LOGIC BIT数据类型定义: TYPE BIT IS('0','1'); -只有两种取值 STD_LOGIC数据类型定义: TYPE STD_LOGIC IS ('U','X','0','1','Z','W','L','H','-'); -有9种取值

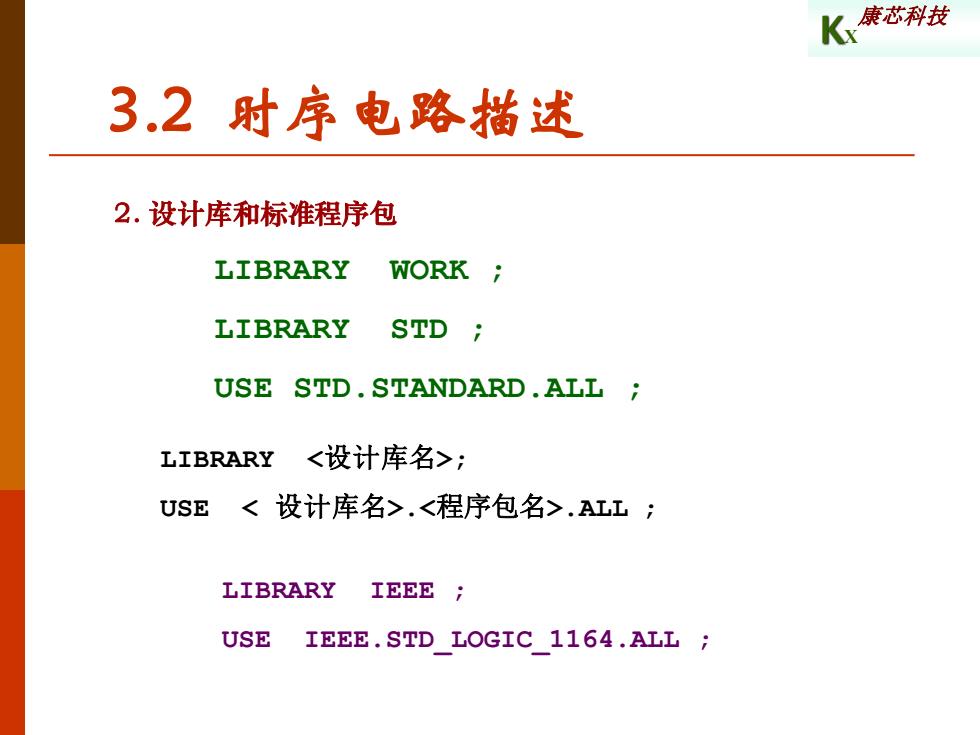

K康还科技 3.2时序电路描述 2.设计库和标准程序包 LIBRARY WORK LIBRARY STD USE STD.STANDARD.ALL LIBRARY<设计库名>; USE<设计库名>.<程序包名>.ALL: LIBRARY IEEE USE IEEE.STD LOGIC 1164.ALL

KX 康芯科技 3.2 时序电路描述 2. 设计库和标准程序包 LIBRARY WORK ; LIBRARY STD ; USE STD.STANDARD.ALL ; LIBRARY <设计库名>; USE < 设计库名>.<程序包名>.ALL ; LIBRARY IEEE ; USE IEEE.STD_LOGIC_1164.ALL ;