DIC 2014 lab1 TA:Pengzhi Chu MicroE@SJTU HSPICE SIMULATION

HSPICE SIMULATION DIC_2014_lab1 TA: Pengzhi Chu MicroE@SJTU

Outline Introduction to Hspice Hspice simulation lab1 Lab Report

Outline Introduction to Hspice Hspice simulation_lab1 Lab Report

Hspice Introduction SPICE-Simulation Program with Integrated Circuit Emphasis developed by U.C.Berkeley SPICE simulate your electrical circuit designs,based on circuit level. Steady-state (DC Analysis) Time (Transient Analysis) Frequency (AC Analysis) ■

Hspice Introduction SPICE – Simulation Program with Integrated Circuit Emphasis developed by U.C.Berkeley SPICE simulate your electrical circuit designs, based on circuit level. Steady-state (DC Analysis) Time (Transient Analysis) Frequency (AC Analysis)

Hspice Introduction HSPICE Models Analog/RF Custom digital Standard cell Signal integrity

Hspice Introduction

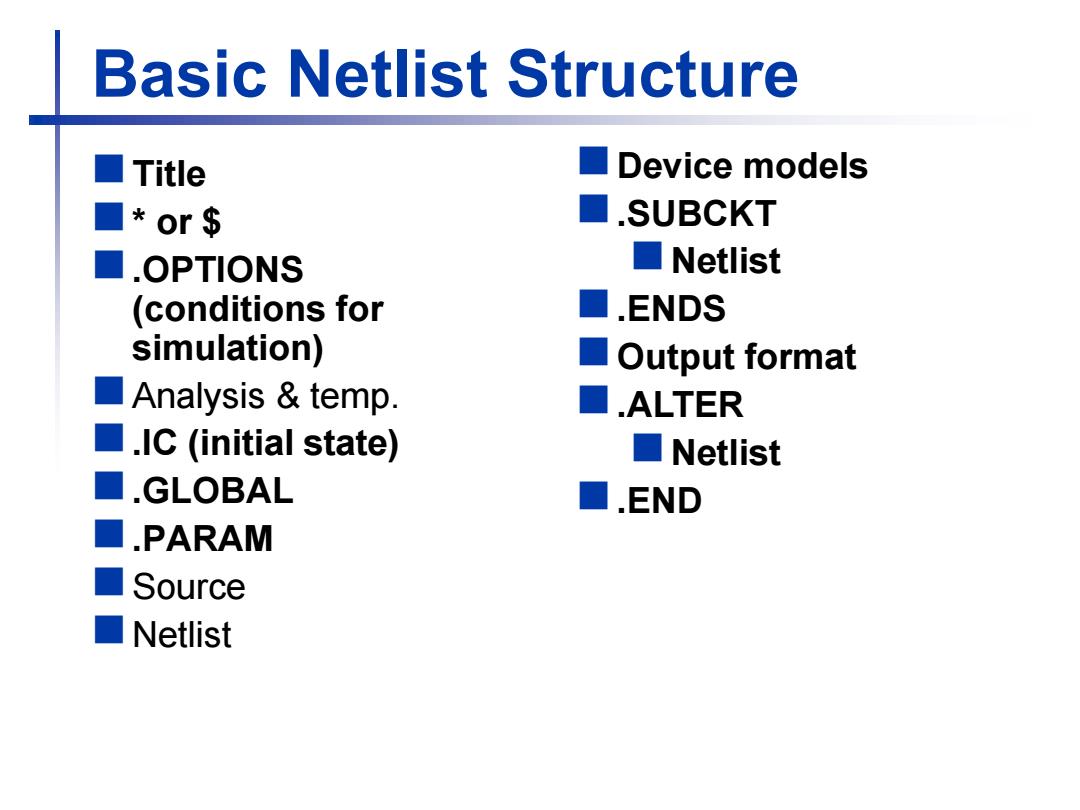

Basic Netlist Structure Title ■Device models or ■.SUBCKT ■.OPTIONS ■Netlist (conditions for ■.ENDS simulation) ☐Output format ☐Analysis&temp. ■.ALTER ☐.lc(initial state) ■Netlist ■.GLOBAL ■.END ■.PARAM ■Source ■Netlist

Basic Netlist Structure Title * or $ .OPTIONS (conditions for simulation) Analysis & temp. .IC (initial state) .GLOBAL .PARAM Source Netlist Device models .SUBCKT Netlist .ENDS Output format .ALTER Netlist .END