EBL技术采用高能电子束对光刻胶进行曝光从而直接获得 结构图形,由于其德布罗意波长为0.004nm左右,EBL不受衍 射极限的影响,可获得接近原子尺度的分辨率。 Reflective mask Separate mask and Vacuum isolation: projection optics Projection optics/ vacuum environments illuminator Illuminator optics 6-Mirror projection optics NA=0.25) EUV-generating Separate projection plasma optics and wafer vacuum environments 300 mm wafer Vacuum isolation:EUV source collector Schematic of an EUVL lithography setup

EBL技术采用高能电子束对光刻胶进行曝光从而直接获得 结构图形,由于其德布罗意波长为0.004nm左右,EBL不受衍 射极限的影响,可获得接近原子尺度的分辨率

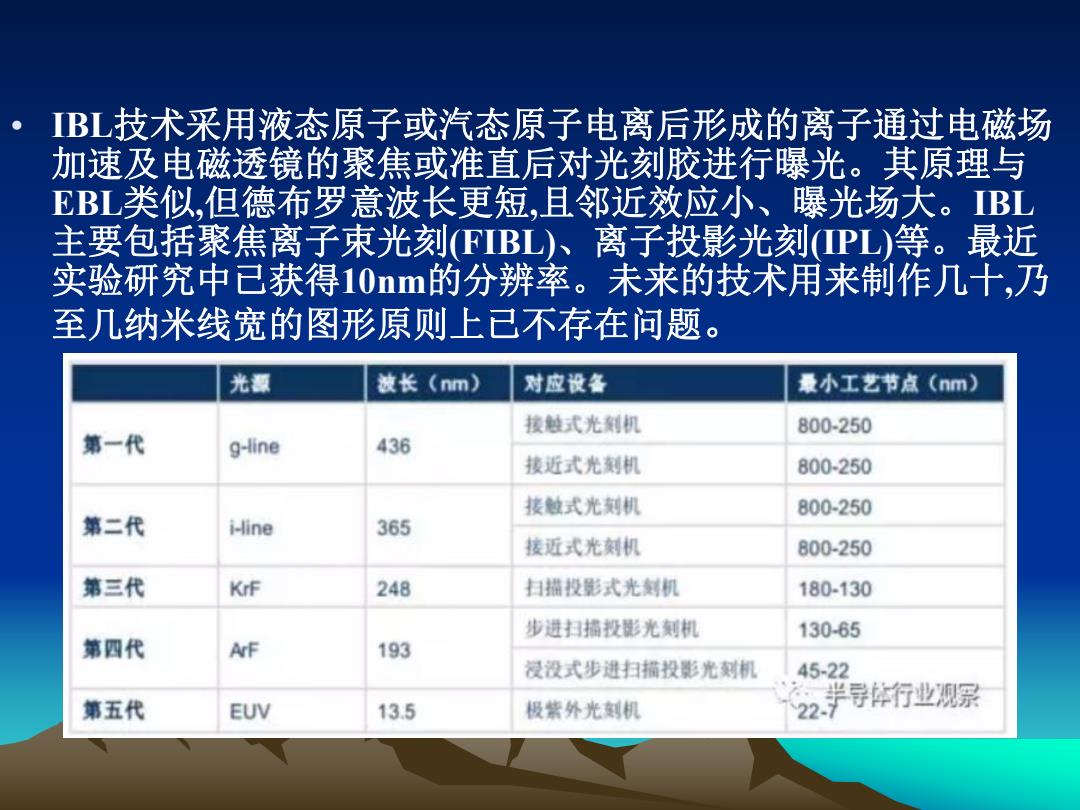

BL技术采用液态原子或汽态原子电离后形成的离子通过电磁场 加速及电磁透镜的聚焦或准直后对光刻胶进行曝光。其原理与 EBL类似,但德布罗意波长更短,且邻近效应小、曝光场大。IBL 主要包括聚焦离子束光刻FBL)、离子投影光刻PL)等。最近 实验研究中已获得10nm的分辨率。未来的技术用来制作几十,乃 至几纳米线宽的图形原则上已不存在问题。 光源 波长(nm) 对应设备 最小工艺节点(nm) 接触式光刻机 800-250 第一代 g-line 436 接近式光刻机 800-250 接触式光刻机 800-250 第二代 i-line 365 接近式光刻机 800-250 第三代 KrF 248 扫描投影式光刻机 180-130 步进扫描投影光刻机 130-65 第四代 ArF 193 浸没式步进扫描投影光刻机 45-22 第五代 EUV 13.5 极紫外光刻机 芋寻体行业观景 22-7

• IBL技术采用液态原子或汽态原子电离后形成的离子通过电磁场 加速及电磁透镜的聚焦或准直后对光刻胶进行曝光。其原理与 EBL类似,但德布罗意波长更短,且邻近效应小、曝光场大。IBL 主要包括聚焦离子束光刻(FIBL)、离子投影光刻(IPL)等。最近 实验研究中已获得10nm的分辨率。未来的技术用来制作几十,乃 至几纳米线宽的图形原则上已不存在问题

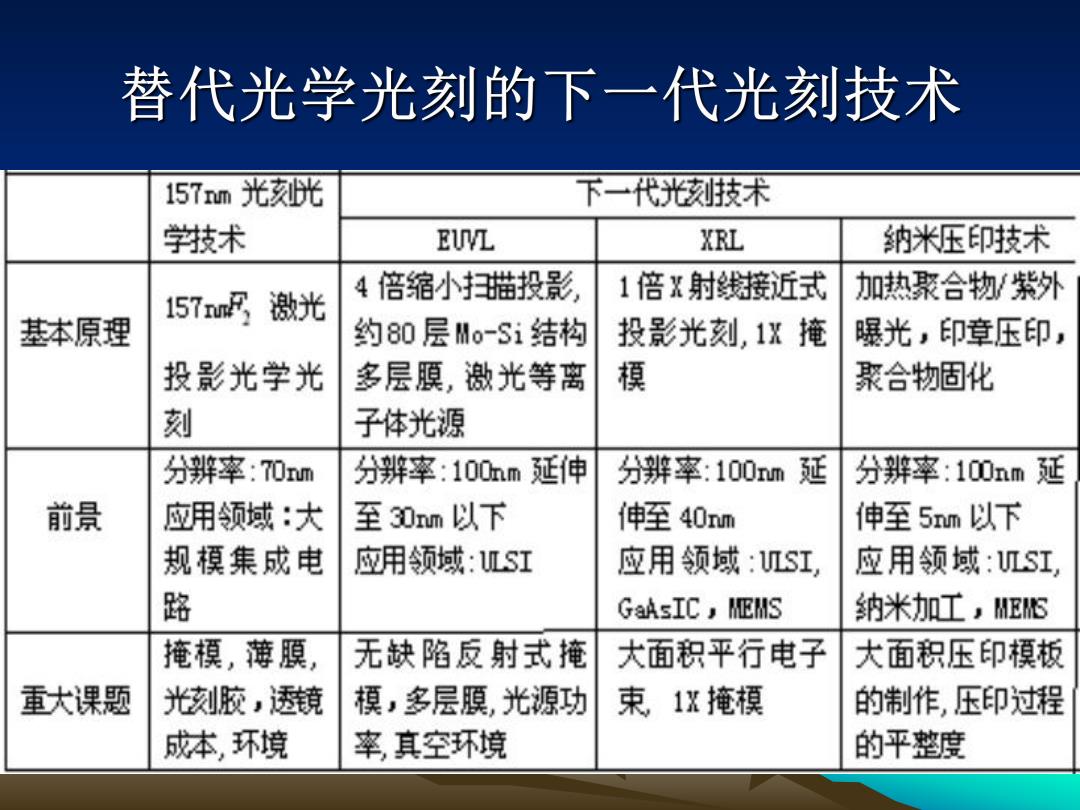

替代光学光刻的下一代光刻技术 157rm光孩刻光 下一代光孩刻技术 学對技术 EUVL XRL 纳米压印技术 157rn激光 4倍缩小扫描投影, 1倍X射接近式 加热聚合物/紫外 基本原理 约80层Mo-Si结构 投影光刻,1X掩 曝光,印章压印, 投影光学光 多层膜,激光等离 模 聚合物固化 刻 子体光源 分辨率:70rn 分辨率:100m延伸 分辨率:100nm延 分辨率:1Dnm延 前景 应用领域:大 至30rm以下 伸至40rm 伸至5m以下 规模集成电 应用领域:LST 应用领域:SI, 应用领域:LSI, 路 GaAsIC,MEMS 纳米加工,MES 掩模,薄膜, 无缺陷反射式掩 大面积平行电子 大面积压印模板 重大课题 光刻胶,透镜 模,多层膘,光源功 束1X掩模 的制作,压印过程 成本,环境 率,真空环境 的平整度

·2、刻蚀、氧化、掺杂等 运用低压、高密度离子源干法刻蚀代替了传统的湿 法刻蚀以实现越来越细的线条和不断增大深宽比的 孔。 批处理高温氧化布散一艺将逐步减少,较深的扩散 区或较厚氧化层的工序还将采用小批量高温工艺 为了实现浅结和精确的沟道杂质剖面控制,单片加 工的离子注人工艺己经逐步取代了批处理的扩散工 艺。 先进的CMOS IC已采用浅的沟槽隔离代替厚的场氧化 隔离,以减少高温处理过程和减小芯片面积

• 2、刻蚀、氧化、掺杂等 • 运用低压、高密度离子源干法刻蚀代替了传统的湿 法刻蚀以实现越来越细的线条和不断增大深宽比的 孔。 • 批处理高温氧化布散一艺将逐步减少,较深的扩散 区或较厚氧化层的工序还将采用小批量高温工艺。 • 为了实现浅结和精确的沟道杂质剖面控制,单片加 工的离子注人工艺己经逐步取代了批处理的扩散工 艺。 • 先进的CMOS IC已采用浅的沟槽隔离代替厚的场氧化 隔离,以减少高温处理过程和减小芯片面积

。3、互连线 采用化学气相淀积(CVD)方法淀积介质或其他材 料薄膜。对导体膜,则采用新的物理气相淀积 (PVD:Physical Vapor Deposition)方法。 CMOS ICx将普遍采用铜连线和低介电常数的介质材 料,因此要发展适于铜互连的新工艺技术。为了 实现多层互连,要保证硅片表面平整,化学机械 抛光(CP:Chemical Mechanical Polish)也是 今后工艺中的一项重要技术

• 3、 互连线 • 采用化学气相淀积(CVD)方法淀积介质或其他材 料薄膜。对导体膜,则采用新的物理气相淀积 (PVD: Physical Vapor Deposition)方法。 • CMOS IC将普遍采用铜连线和低介电常数的介质材 料,因此要发展适于铜互连的新工艺技术。为了 实现多层互连,要保证硅片表面平整,化学机械 抛光(CMP: Chemical Mechanical Polish) 也是 今后工艺中的一项重要技术