表2-2 AB CD 0001 1110 00 01 11 10 由卡诺图得出逻辑表达式,并演化成“与非”的形式 Z=ABC+BCD+ACD+ABD=ABC·BCD-ACD·ABC 根据逻辑表达式画出用“与非门”构成的逻辑电路如图2一2所示,用实验验证 逻辑功能。 图2一2表决电路逻辑图 在实验装置适当位置选定三个14P插座,按照集成块定位标记插好集成块74S20。 按图2一2接线,输入端A、B、C、D接至逻辑开关输出插口,输出端Z接逻辑电 平显示输入插口,按真值表要求,逐次改变输入变量,测量相应的输出值,验证逻辑 功能。与表2一1进行比较,验证所设计的逻辑电路是否符合要求。 三、实验设备与器件 1、现代数字电路系统实验箱2、直流数字万用表 3、74LS0074LS2074LS8674LS55 四、实验内容 1、用与74LS00、74LS20设计一个三人无弃权表决电路,当两个或两个以上输入 为“1”时,输出端才为“1”。 2、设计用异或门(74LS86)和与非门(74LS00、74LS20)组成半加器、全减器 9

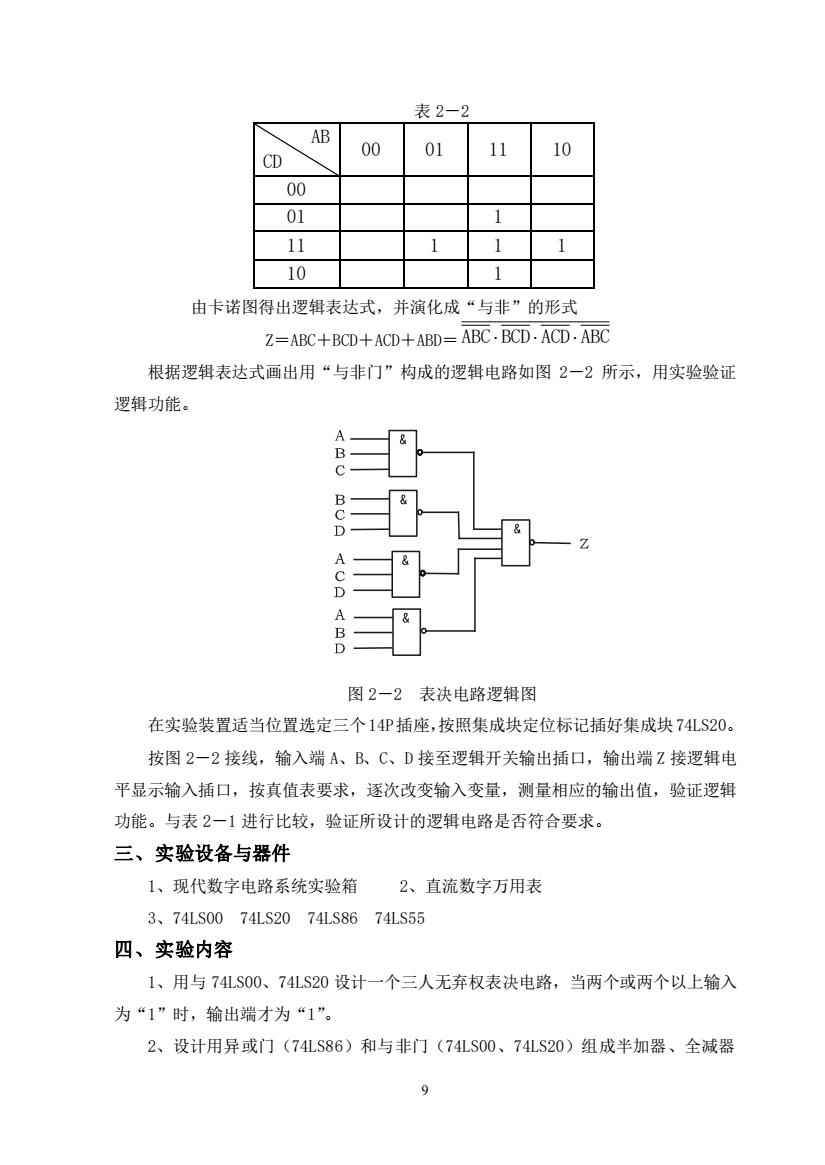

9 表 2-2 AB CD 00 01 11 10 00 01 1 11 1 1 1 10 1 由卡诺图得出逻辑表达式,并演化成“与非”的形式 Z=ABC+BCD+ACD+ABD= ABC BCD ACD ABC 根据逻辑表达式画出用“与非门”构成的逻辑电路如图 2-2 所示,用实验验证 逻辑功能。 图 2-2 表决电路逻辑图 在实验装置适当位置选定三个14P插座,按照集成块定位标记插好集成块74LS20。 按图 2-2 接线,输入端 A、B、C、D 接至逻辑开关输出插口,输出端 Z 接逻辑电 平显示输入插口,按真值表要求,逐次改变输入变量,测量相应的输出值,验证逻辑 功能。与表 2-1 进行比较,验证所设计的逻辑电路是否符合要求。 三、实验设备与器件 1、现代数字电路系统实验箱 2、直流数字万用表 3、74LS00 74LS20 74LS86 74LS55 四、实验内容 1、用与 74LS00、74LS20 设计一个三人无弃权表决电路,当两个或两个以上输入 为“1”时,输出端才为“1”。 2、设计用异或门(74LS86)和与非门(74LS00、74LS20)组成半加器、全减器

电路。用741S86、74LS55、74LS00实现全加器电路 要求按本文所述的设计步骤进行,直到测试电路逻辑功能符合设计要求为止。 五、实验预习要求 1、根据实验任务要求设计组合电路,并根据所给的标准器件画出逻辑图。 2、如何用最简单的方法验证“与或非”门的逻辑功能是否完好? 3、“与或非”门中,当某一组与端不用时,应作如何处理? 六、实验报告 1、列写实验任务的设计过程,画出设计的电路图。 2、对所设计的电路进行实验测试,记录测试结果。 3、组合电路设计体会。 七、集成电路引脚图 +5y 网国回同而可8风 网国回回网可8 B @ 可▣ 46 图2-374LS00引脚图 图2-474LS55引脚图 3A 3Y 网国▣而回⑧ 回回 中高 图2-574LS86引脚图 10

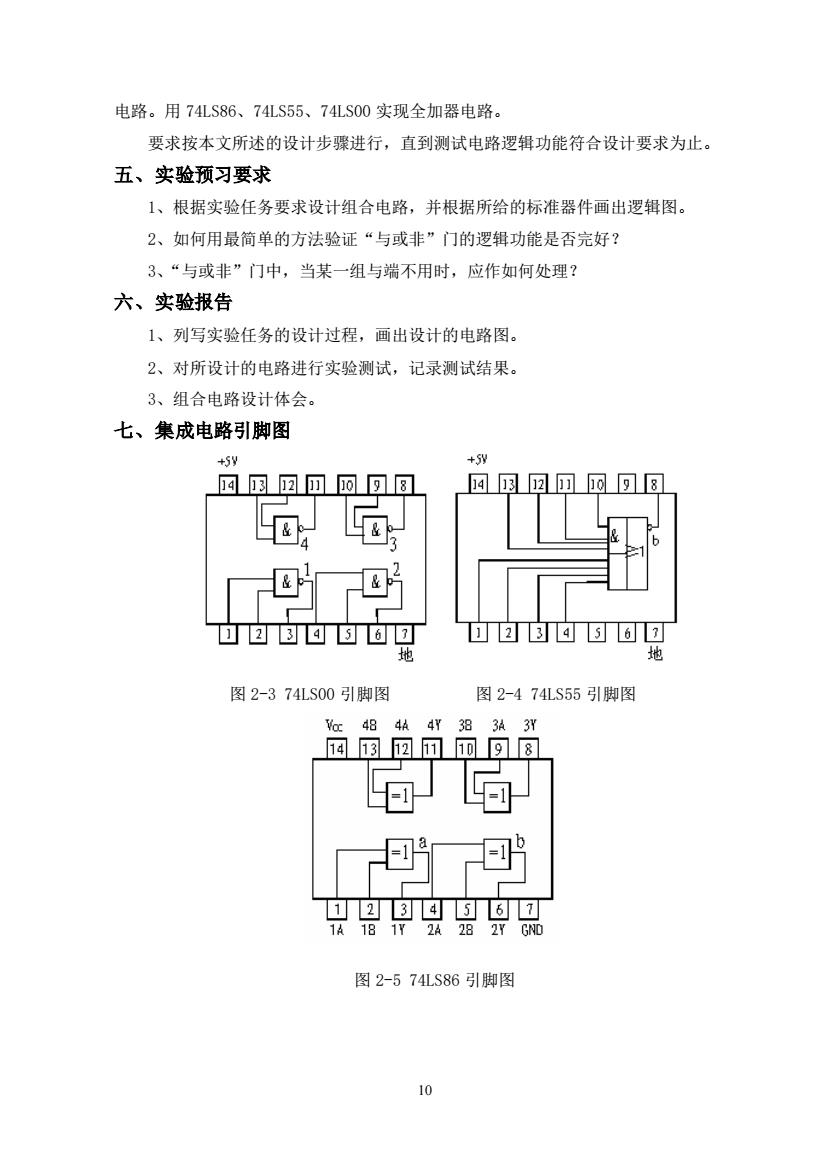

10 电路。用 74LS86、74LS55、74LS00 实现全加器电路。 要求按本文所述的设计步骤进行,直到测试电路逻辑功能符合设计要求为止。 五、实验预习要求 1、根据实验任务要求设计组合电路,并根据所给的标准器件画出逻辑图。 2、如何用最简单的方法验证“与或非”门的逻辑功能是否完好? 3、“与或非”门中,当某一组与端不用时,应作如何处理? 六、实验报告 1、列写实验任务的设计过程,画出设计的电路图。 2、对所设计的电路进行实验测试,记录测试结果。 3、组合电路设计体会。 七、集成电路引脚图 图 2-3 74LS00 引脚图 图 2-4 74LS55 引脚图 图 2-5 74LS86 引脚图

实验三译码器及其应用 一、实验目的 1、掌握中规模集成译码器的逻辑功能和使用方法 2、熟悉数码管的使用 二、实验原理 译码器是一个多输入、多输出的组合逻辑电路。它的作用是把给定的代码进行“翻 译”,变成相应的状态,使输出通道中相应的一路有信号输出。译码器在数字系统中 有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配,存贮器寻 址和组合控制信号等。不同的功能可选用不同种类的译码器。 译码器可分为通用译码器和显示译码器两大类。前者又分为变量译码器和代码变 换译码器。 1、变量译码器(又称二进制译码器),用以表示输入变量的状态,如2线一4线、 3线一8线和4线一16线译码器。若有n个输入变量,则有21个不同的组合状态,就 有2个输出端供其使用。而每一个输出所代表的函数对应于n个输入变量的最小项。 以3线一8线译码器74LS138为例进行分析,图3一1(a)、(6)分别为其逻辑图及 引脚排列。 其中A2、A、A为地址输入端,了。~可,为译码输出端,S、S2、S为使 能端。 65v 3 13 12 白中中 11 Y o Y 白白白aD 7 Ao A (a) h 图3-13一8线译码器74LS138逻辑图及引脚排列 表3-1为74S138功能表,当S=1,S2+S=0时,器件使能,地址码所指定 的输出端有信号(为0)输出,其它所有输出端均无信号(全为1)输出。当S,=0, 11

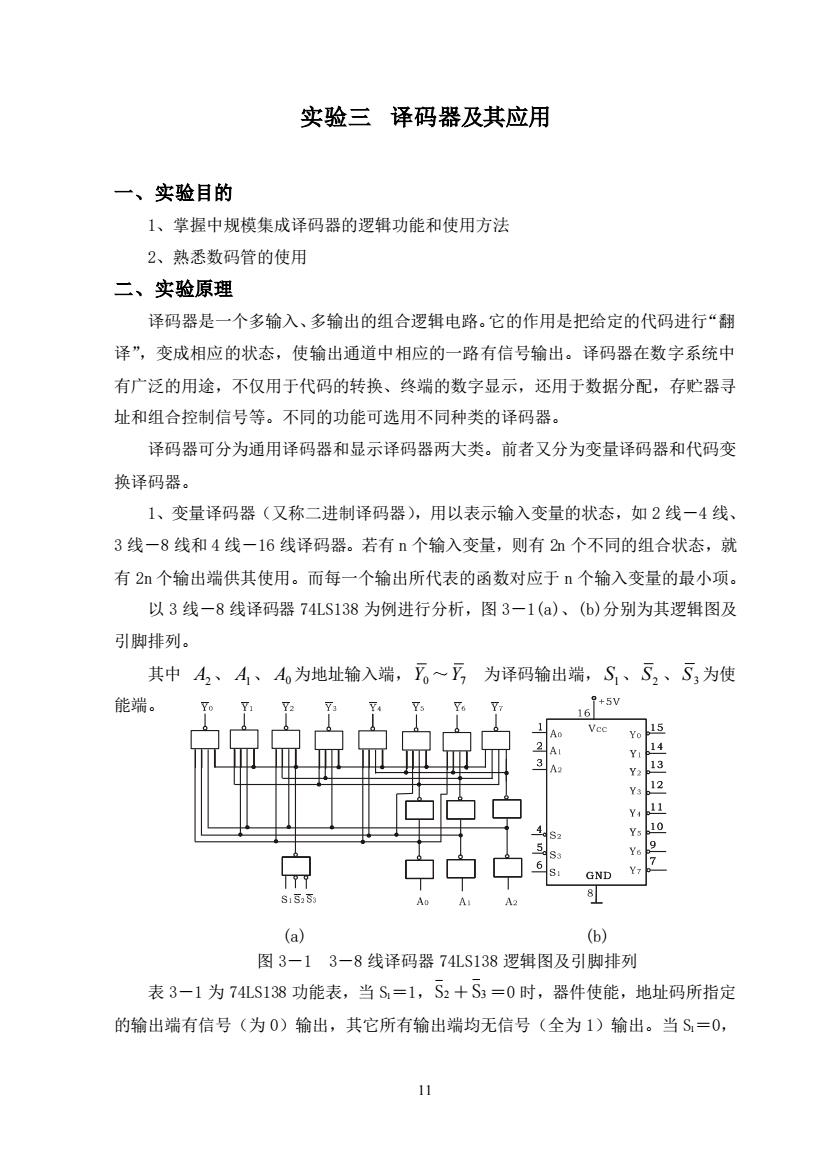

11 实验三 译码器及其应用 一、实验目的 1、掌握中规模集成译码器的逻辑功能和使用方法 2、熟悉数码管的使用 二、实验原理 译码器是一个多输入、多输出的组合逻辑电路。它的作用是把给定的代码进行“翻 译”,变成相应的状态,使输出通道中相应的一路有信号输出。译码器在数字系统中 有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配,存贮器寻 址和组合控制信号等。不同的功能可选用不同种类的译码器。 译码器可分为通用译码器和显示译码器两大类。前者又分为变量译码器和代码变 换译码器。 1、变量译码器(又称二进制译码器),用以表示输入变量的状态,如 2 线-4 线、 3 线-8 线和 4 线-16 线译码器。若有 n 个输入变量,则有 2n 个不同的组合状态,就 有 2n 个输出端供其使用。而每一个输出所代表的函数对应于 n 个输入变量的最小项。 以 3 线-8 线译码器 74LS138 为例进行分析,图 3-1(a)、(b)分别为其逻辑图及 引脚排列。 其中 A2、 A1、 A0 为地址输入端, Y0 ~Y7 为译码输出端, 1 S 、 2 S 、 3 S 为使 能端。 (a) (b) 图 3-1 3-8 线译码器 74LS138 逻辑图及引脚排列 表 3-1 为 74LS138 功能表,当 S1=1,S2 + S3 =0 时,器件使能,地址码所指定 的输出端有信号(为 0)输出,其它所有输出端均无信号(全为 1)输出。当 S1=0

52+5=×时,或S=×,52+5=1时,译码器被禁止,所有输出同时为1. 表3-174LS138功能表 输入 输 出 S2+53 6 1 0 0 X ×1111 1 11 1 二进制译码器实际上也是负脉冲输出的脉冲分配器。若利用使能端中的一个输 入端输入数据信息,器件就成为一个数据分配器(仅称多路分配器),如图3一2所示。 若在S输入端输入数据信息,S,=S=0,地址码所对应的输出是S,数据信息的反码: 若从S2端输入数据信息,令S=1、S=0,地址码所对应的输出就是S2端数据信息 的原码。若数据信息是时钟脉冲,则数据分配器便成为时钟脉冲分配器。 根据输入地址的不同组合译出唯一地址,故可用作地址译码器。接成多路分配 器,可将一个信号源的数据信息传输到不同的地点。 三进制译码器还能方便地实现逻辑函数,如图3一3所示,实现的逻辑函数是 Z=ABC+ABC+ABC+ABC 12

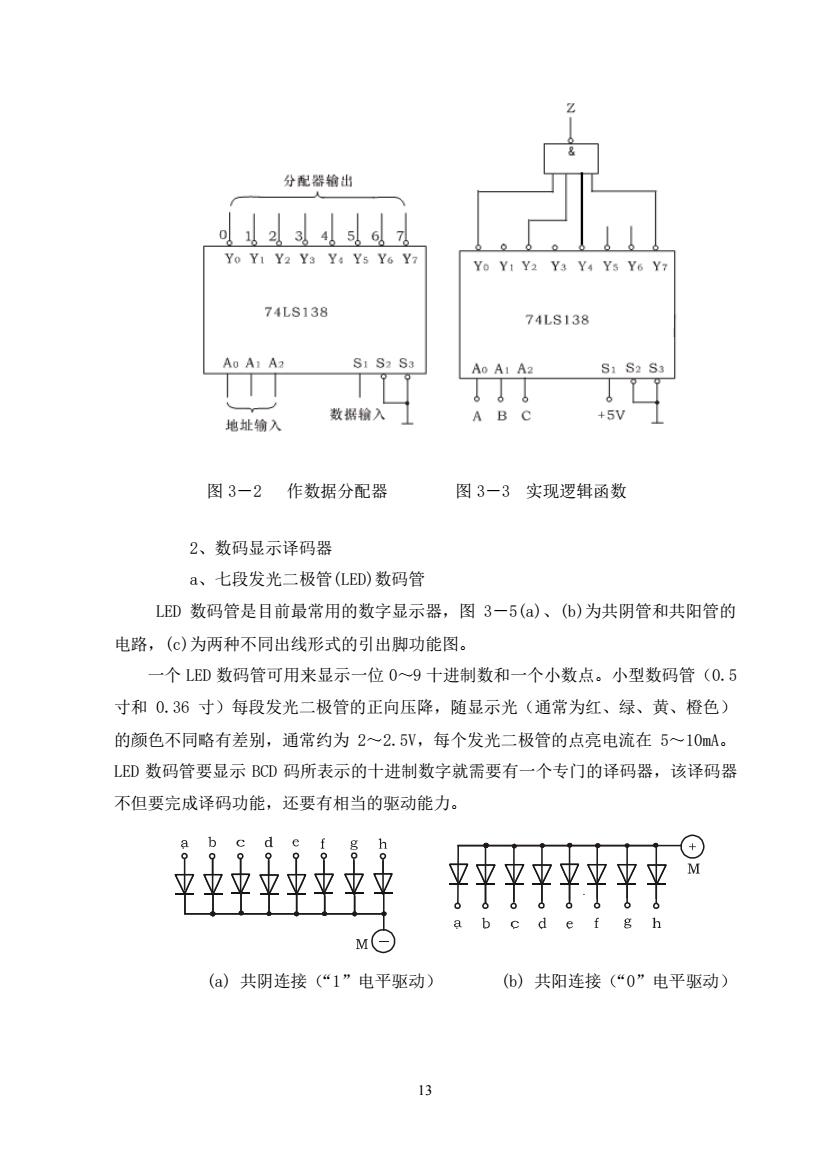

12 S2 + S3 =×时,或 S1=×,S2 + S3 =1 时,译码器被禁止,所有输出同时为 1。 表 3-1 74LS138 功能表 输 入 输 出 S1 S2 + S3 A2 A1 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 1 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 1 1 0 0 1 0 1 1 0 1 1 1 1 1 1 0 0 1 1 1 1 1 0 1 1 1 1 1 0 1 0 0 1 1 1 1 0 1 1 1 1 0 1 0 1 1 1 1 1 1 0 1 1 1 0 1 1 0 1 1 1 1 1 1 0 1 1 0 1 1 1 1 1 1 1 1 1 1 0 0 × × × × 1 1 1 1 1 1 1 1 × 1 × × × 1 1 1 1 1 1 1 1 二进制译码器实际上也是负脉冲输出的脉冲分配器。若利用使能端中的一个输 入端输入数据信息,器件就成为一个数据分配器(又称多路分配器),如图 3-2 所示。 若在 1 S 输入端输入数据信息, S2 =S3 =0,地址码所对应的输出是 1 S 数据信息的反码; 若从 S2 端输入数据信息,令 1 S =1、S3 =0,地址码所对应的输出就是 S2 端数据信息 的原码。若数据信息是时钟脉冲,则数据分配器便成为时钟脉冲分配器。 根据输入地址的不同组合译出唯一地址,故可用作地址译码器。接成多路分配 器,可将一个信号源的数据信息传输到不同的地点。 三进制译码器还能方便地实现逻辑函数,如图 3-3 所示,实现的逻辑函数是 Z= ABC + ABC + ABC + ABC

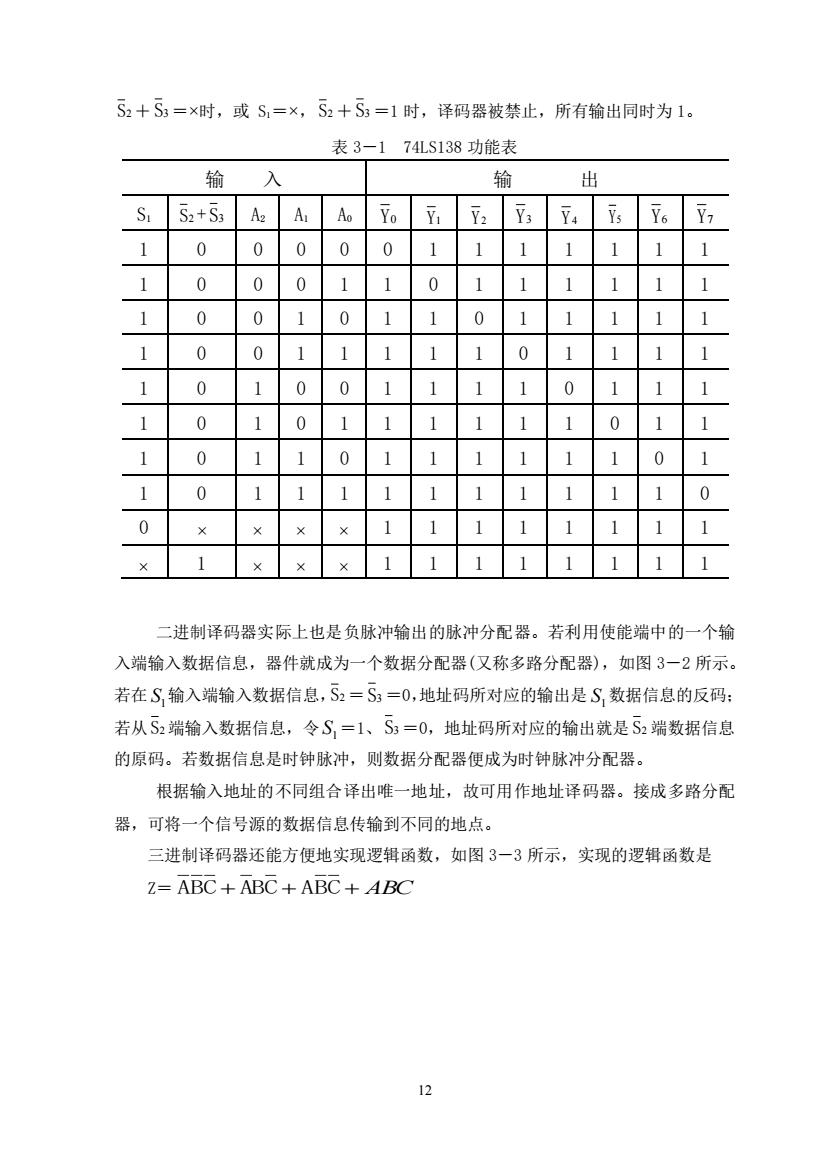

分配器输出 Yo YI Y2 Y3 Ya Ys Yo Y7 Yo Y1 Y2 Y3 Y4 Ys Y6 Y 74LS138 74LS138 Ao AA Sa S3 Ao A1 A2 S1 S2 S3 地址输入 数据输入 5V 图3一2作数据分配器 图3一3实现逻辑函数 2、数码显示译码器 a、七段发光二极管(LED)数码管 LD数码管是目前最常用的数字显示器,图3一5(a)、(b)为共阴管和共阳管的 电路,(c)为两种不同出线形式的引出脚功能图。 一个LD数码管可用来显示一位09十进制数和一个小数点。小型数码管(0.5 寸和0.36寸)每段发光二极管的正向压降,随显示光(通常为红、绿、黄、橙色) 的颜色不同略有差别,通常约为2~2.5V,,每个发光二极管的点亮电流在5~10mA。 LED数码管要显示BCD码所表示的十进制数字就需要有一个专门的译码器,该译码器 不但要完成译码功能,还要有相当的驱动能力。 中中应中中应亚应亚 a b c d e f g h MO (a)共阴连接(“1”电平驱动)(6)共阳连接(“0”电平驱动) 13

13 图 3-2 作数据分配器 图 3-3 实现逻辑函数 2、数码显示译码器 a、七段发光二极管(LED)数码管 LED 数码管是目前最常用的数字显示器,图 3-5(a)、(b)为共阴管和共阳管的 电路,(c)为两种不同出线形式的引出脚功能图。 一个 LED 数码管可用来显示一位 0~9 十进制数和一个小数点。小型数码管(0.5 寸和 0.36 寸)每段发光二极管的正向压降,随显示光(通常为红、绿、黄、橙色) 的颜色不同略有差别,通常约为 2~2.5V,每个发光二极管的点亮电流在 5~10mA。 LED 数码管要显示 BCD 码所表示的十进制数字就需要有一个专门的译码器,该译码器 不但要完成译码功能,还要有相当的驱动能力。 (a) 共阴连接(“1”电平驱动) (b) 共阳连接(“0”电平驱动)