t的测试电路如图1一5(b)所示,由于TTL门电路的延迟时间较小,直接测量时 对信号发生器和示波器的性能要求较高,故实验采用测量由奇数个与非门组成的环形振 荡器的振荡周期T来求得。其工作原理是:假设电路在接通电源后某一瞬间,电路中 的A点为逻辑“1”,经过三级门的延迟后,使A点由原来的逻辑“1”变为逻辑“0”: 再经过三级门的延迟后,A点电平又重新回到逻辑“1”。电路中其它各点电平也跟随变 化。说明使A点发生一个周期的振荡,必须经过6级门的延迟时间。因此平均传输延 迟时间为 T tpd Tm电路的一般在10S品之间。 74LS20主要电参数规范如表1一1所示 表1-1 参数名称和符号 规范值单位 测试条件 通导电源电流c <14mA Vc=5V,输入端悬空,输出端空载 截止电源电流 <7 mA Vc=5V,输入端接地,输出端空载 Vc=5V,被测输入端接地,其他输入 低电平输入电流 ≤1.4 mA 端悬空,输出端空载 Vc=5V,被测输入端V.=2.4W,其 <50 μA 他输入端接地,输出端空载。 流 高电平输入电流 参 下1 Vc=5V,被测输入端V.=5V,其他 mA 输入端接地,输出端空载。 Ve=5V,被测输入端V.=0.8V,其 输出高电平 ≥3.4 他输入端悬空,1m=400μA。 Vc=5V,输入端Vn=2.0V, 输出低电平 <0.3 I=12.8mA。 扇出系数 N 4-8 V 同Vm和VL 交 流参 Vc=5V,被测输入端输入信号: 平均传输延迟时间 ≤20 ns 数 Vn=3.0V,f=2Hz。 三、实验设备与器件 1、现代数字电路系统实验箱 2、直流数字万用表

4 tpd的测试电路如图 1-5(b)所示,由于 TTL 门电路的延迟时间较小,直接测量时 对信号发生器和示波器的性能要求较高,故实验采用测量由奇数个与非门组成的环形振 荡器的振荡周期 T 来求得。 其工作原理是:假设电路在接通电源后某一瞬间,电路中 的 A 点为逻辑“1”,经过三级门的延迟后,使 A 点由原来的逻辑“1”变为逻辑“0”; 再经过三级门的延迟后,A 点电平又重新回到逻辑“1”。电路中其它各点电平也跟随变 化。说明使 A 点发生一个周期的振荡,必须经过 6 级门的延迟时间。因此平均传输延 迟时间为 TTL 电路的 tpd 一般在 10nS~40nS 之间。 74LS20 主要电参数规范如表 1-1 所示 表 1-1 参数名称和符号 规范值 单位 测 试 条 件 直 流 参 数 通导电源电流 ICCL <14 mA VCC=5V,输入端悬空,输出端空载 截止电源电流 ICCH <7 mA VCC=5V,输入端接地,输出端空载 低电平输入电流 IiL ≤1.4 mA VCC=5V,被测输入端接地,其他输入 端悬空,输出端空载 高电平输入电流 IiH <50 μA VCC=5V,被测输入端 Vin=2.4V,其 他输入端接地,输出端空载。 <1 mA VCC=5V,被测输入端 Vin=5V,其他 输入端接地,输出端空载。 输出高电平 VOH ≥3.4 V VCC=5V,被测输入端 Vin=0.8V,其 他输入端悬空,IOH=400μA。 输出低电平 VOL <0.3 V VCC=5V,输入端 Vin=2.0V, IOL=12.8mA。 扇出系数 NO 4~8 V 同 VOH 和 VOL 交 流 参 数 平均传输延迟时间 tpd ≤20 ns VCC=5V,被测输入端输入信号: Vin=3.0V,f=2MHz。 三、实验设备与器件 1、现代数字电路系统实验箱 2、 直流数字万用表 6 T tpd =

3、74LS20、10K电位器,100Q电阻器(0.5W) 0.47y0.01μ100030007. 图16实验元件板 四、实验内容 验证TTL集成与非门74L.S20的逻辑功能 按图1一7接线,门的四个输入端接逻辑开关输出插口,以提供“0”与“1”电平 信号,开关向上,输出逻辑“1”,向下为逻辑“0”。门的输出端接由LED发光二极管 组成的逻辑电平显示器(又称0一1指示器)的显示插口,LD亮为逻辑“1”,不亮为 逻辑“0”。按表1一2的真值表逐个测试集成块中两个与非门的逻辑功能。74LS20有4 个输入端,有16个最小项,在实际测试时,只要通过对输入1111、0111、1011、1101、 1110五项进行检测就可判断其逻辑功能是否正常。 9+5V 14 74Ls20 小N 45 71 G A1 BI CI D 图1-7与非门逻辑功能测试电路

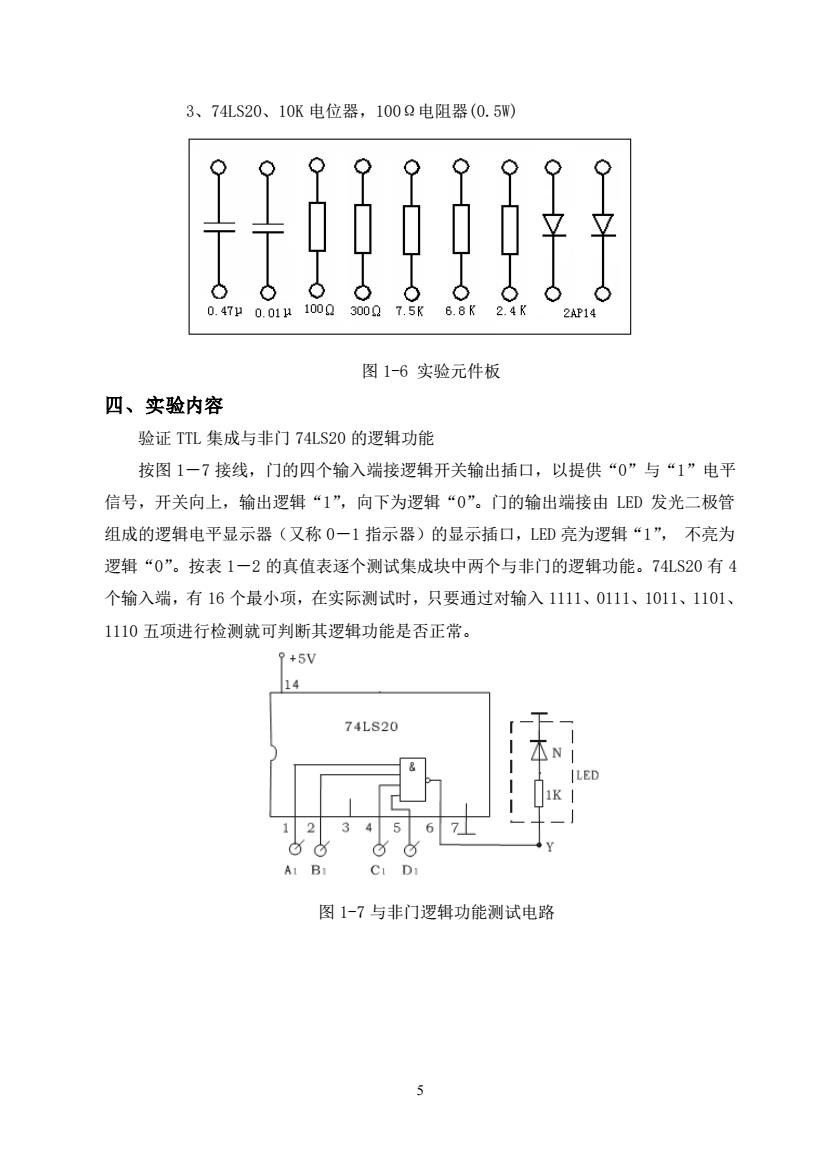

5 3、74LS20、10K 电位器,100Ω电阻器(0.5W) 图 1-6 实验元件板 四、实验内容 验证 TTL 集成与非门 74LS20 的逻辑功能 按图 1-7 接线,门的四个输入端接逻辑开关输出插口,以提供“0”与“1”电平 信号,开关向上,输出逻辑“1”,向下为逻辑“0”。门的输出端接由 LED 发光二极管 组成的逻辑电平显示器(又称 0-1 指示器)的显示插口,LED 亮为逻辑“1”, 不亮为 逻辑“0”。按表 1-2 的真值表逐个测试集成块中两个与非门的逻辑功能。74LS20 有 4 个输入端,有 16 个最小项,在实际测试时,只要通过对输入 1111、0111、1011、1101、 1110 五项进行检测就可判断其逻辑功能是否正常。 图 1-7 与非门逻辑功能测试电路

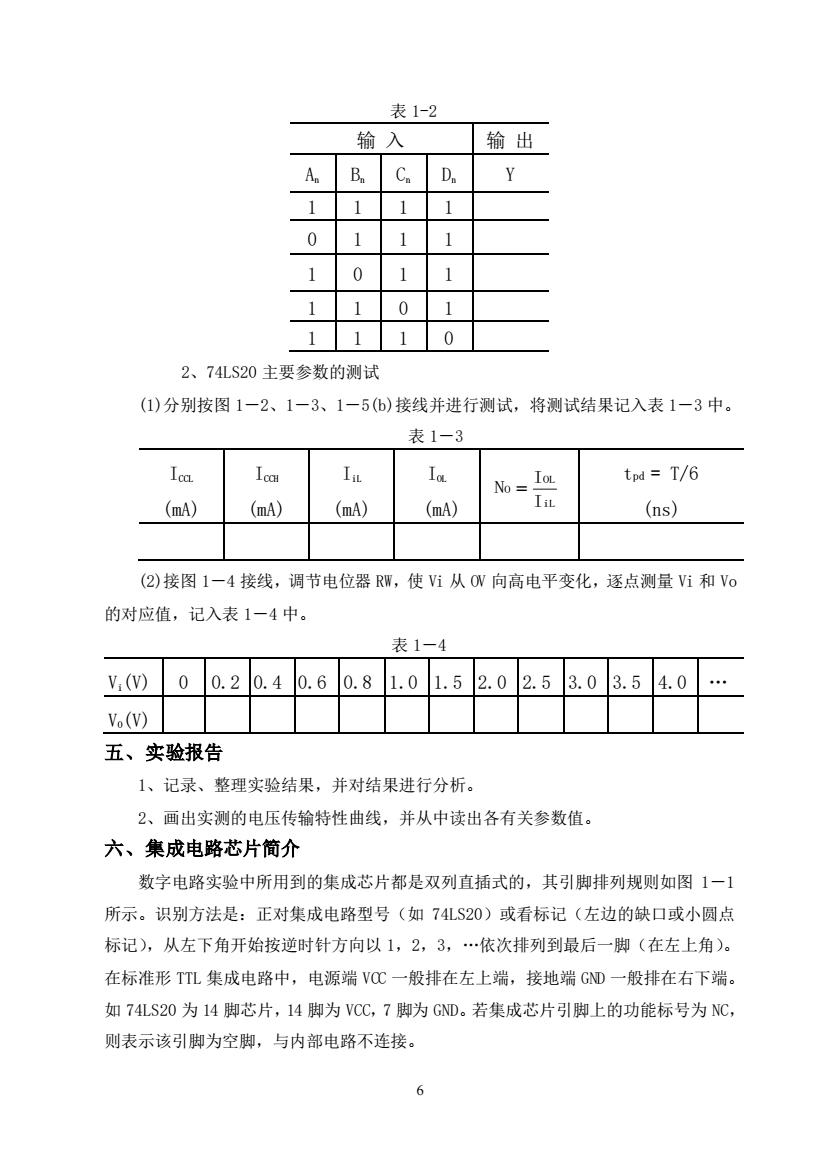

表1-2 输入 输出 B.C D. Y 0 1110 2、74LS20主要参数的测试 (1)分别按图1一2、1-3、1一5(6)接线并进行测试,将测试结果记入表1一3中。 表1-3 No Io tpd=T/6 (mA) (mA) (mA) (mA) I (ns) (②)接图1一4接线,调节电位器Rm,使Vi从0W向高电平变化,逐点测量Vi和Vo 的对应值,记入表1一4中。 表1-4 v000.20.40.60.81.01.52.02.53.03.54.0. Vo(V) 五、实验报告 1、记录、整理实验结果,并对结果进行分析。 2、画出实测的电压传输特性曲线,并从中读出各有关参数值。 六、集成电路芯片简介 数字电路实验中所用到的集成芯片都是双列直插式的,其引脚排列规则如图1一1 所示。识别方法是:正对集成电路型号(如74LS20)或看标记(左边的缺口或小圆点 标记),从左下角开始按逆时针方向以1,2,3,.依次排列到最后一脚(在左上角)。 在标准形TTL集成电路中,电源端VCC一般排在左上端,接地端GD一般排在右下端。 如74LS20为14脚芯片,14脚为VCC,7脚为GND。若集成芯片引脚上的功能标号为NC, 则表示该引脚为空脚,与内部电路不连接。 6

6 表 1-2 输 入 输 出 An Bn Cn Dn Y 1 1 1 1 0 1 1 1 1 0 1 1 1 1 0 1 1 1 1 0 2、74LS20 主要参数的测试 (1)分别按图 1-2、1-3、1-5(b)接线并进行测试,将测试结果记入表 1-3 中。 表 1-3 ICCL (mA) ICCH (mA) IiL (mA) IOL (mA) tpd = T/6 (ns) (2)接图 1-4 接线,调节电位器 RW,使 Vi 从 OV 向高电平变化,逐点测量 Vi 和 Vo 的对应值,记入表 1-4 中。 表 1-4 Vi(V) 0 0.2 0.4 0.6 0.8 1.0 1.5 2.0 2.5 3.0 3.5 4.0 . VO(V) 五、实验报告 1、记录、整理实验结果,并对结果进行分析。 2、画出实测的电压传输特性曲线,并从中读出各有关参数值。 六、集成电路芯片简介 数字电路实验中所用到的集成芯片都是双列直插式的,其引脚排列规则如图 1-1 所示。识别方法是:正对集成电路型号(如 74LS20)或看标记(左边的缺口或小圆点 标记),从左下角开始按逆时针方向以 1,2,3,.依次排列到最后一脚(在左上角)。 在标准形 TTL 集成电路中,电源端 VCC 一般排在左上端,接地端 GND 一般排在右下端。 如 74LS20 为 14 脚芯片,14 脚为 VCC,7 脚为 GND。若集成芯片引脚上的功能标号为 NC, 则表示该引脚为空脚,与内部电路不连接。 iL OL O I I N =

七、TTL集成电路使用规则 1、接插集成块时,要认清定位标记,不得插反。 2、电源电压使用范围为+4.5V~+5.5V之间,实验中要求使用Vcc=+5V。电源 极性绝对不允许接错。 3、闲置输入端处理方法 (1)悬空,相当于正逻辑“1”,对于一般小规模集成电路的数据输入端,实验 时允许悬空处理。但易受外界干扰,导致电路的逻辑功能不正常。因此,对于接有长线 的输入端,中规模以上的集成电路和使用集成电路较多的复杂电路,所有控制输入端必 须按逻辑要求接入电路,不允许悬空。 (2)直接接电源电压Vc(也可以串入一只1~10KQ的固定电阻)或接至某一固 定电压(+2.4≤V≤4.5V)的电源上,或与输入端为接地的多余与非门的输出端相接。 (③)若前级驱动能力允许,可以与使用的输入端并联。 4、输入端通过电阻接地,电阻值的大小将直接影响电路所处的状态。当R≤680Q 时,输入端相当于逻辑“0”:当R≥4.7KQ时,输入端相当于逻辑“1”。对于不同系 列的器件,要求的阻值不同。 5、输出端不允许并联使用(集电极开路门(OC)和三态输出门电路(3S)除外)。否则 不仅会使电路逻辑功能混乱,并会导致器件损坏。 6、输出端不允许直接接地或直接接+5V电源,否则将损坏器件,有时为了使后级 电路获得较高的输出电平,允许输出端通过电阻R接至Vcc,一般取R=3~5.1KQ。 1

7 七、TTL 集成电路使用规则 1、接插集成块时,要认清定位标记,不得插反。 2、电源电压使用范围为+4.5V~+5.5V 之间,实验中要求使用 Vcc=+5V。电源 极性绝对不允许接错。 3、闲置输入端处理方法 (1) 悬空,相当于正逻辑“1”,对于一般小规模集成电路的数据输入端,实验 时允许悬空处理。但易受外界干扰,导致电路的逻辑功能不正常。因此,对于接有长线 的输入端,中规模以上的集成电路和使用集成电路较多的复杂电路,所有控制输入端必 须按逻辑要求接入电路,不允许悬空。 (2) 直接接电源电压 VCC(也可以串入一只 1~10KΩ的固定电阻)或接至某一固 定电压(+2.4≤V≤4.5V)的电源上, 或与输入端为接地的多余与非门的输出端相接。 (3) 若前级驱动能力允许,可以与使用的输入端并联。 4、输入端通过电阻接地,电阻值的大小将直接影响电路所处的状态。当 R≤680Ω 时,输入端相当于逻辑“0”;当 R≥4.7 KΩ时,输入端相当于逻辑“1”。对于不同系 列的器件,要求的阻值不同。 5、输出端不允许并联使用(集电极开路门(OC)和三态输出门电路(3S)除外)。否则 不仅会使电路逻辑功能混乱,并会导致器件损坏。 6、输出端不允许直接接地或直接接+5V 电源,否则将损坏器件,有时为了使后级 电路获得较高的输出电平,允许输出端通过电阻 R 接至 Vcc,一般取 R=3~5.1 KΩ

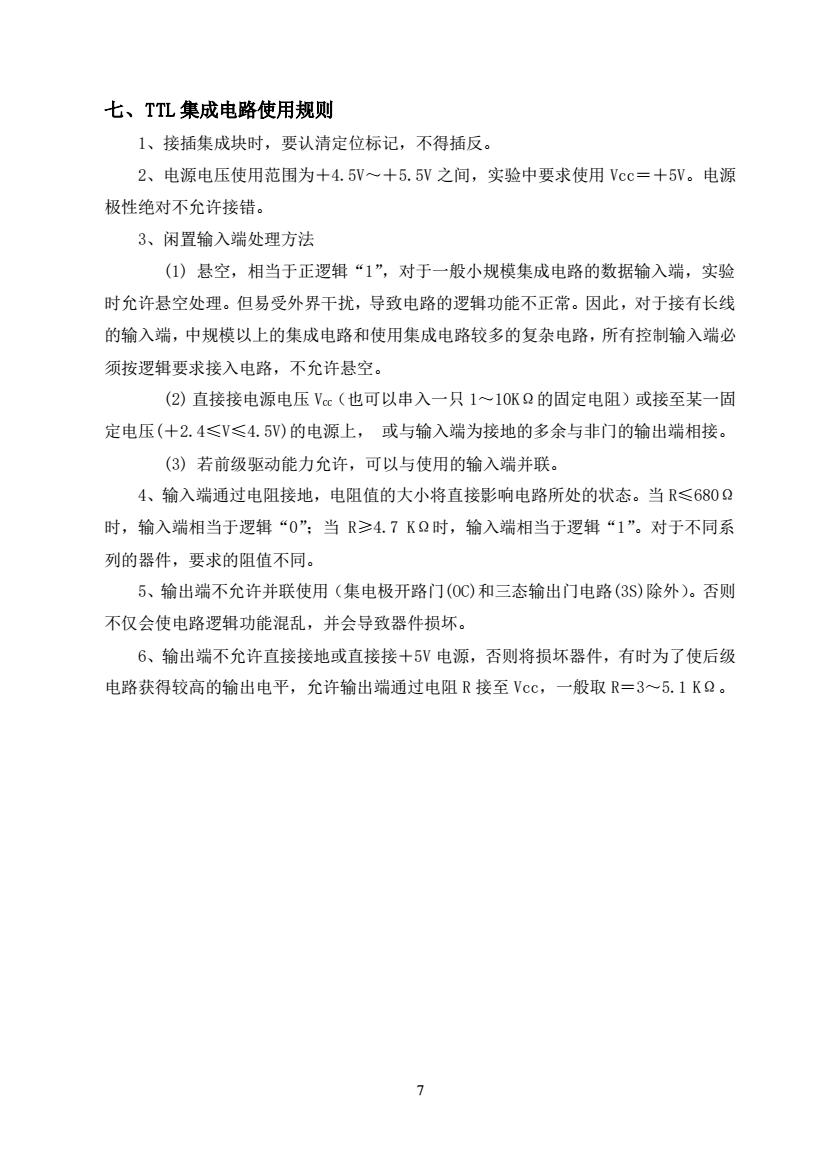

实验二组合逻辑电路的设计与测试 一、实验目的 掌握组合逻辑电路的设计与测试方法 二、实验原理 1、使用中、小规模集成电路来设计组合电路是最常见的逻辑电路。设计组合电路 的一般步骤如图2-1所示。 设计婴求 真值表 逻辑表达式 卡诺图 简化逻辑表达式 逻辑图■ 图2一1组合逻辑电路设计流程图 根据设计任务的要求建立输入、输出变量,并列出真值表。然后用逻辑代数或卡 诺图化简法求出简化的逻辑表达式。并按实际选用逻辑门的类型修改逻辑表达式。根 据简化后的逻辑表达式,画出逻辑图,用标准器件构成逻辑电路。最后,用实验来验 证设计的正确性。 2、组合逻辑电路设计举例 用“与非”门设计一个表决电路。当三个输入端中有两个或三个为“1”时,输 出端才为“1”。 设计步骤:根据题意列出真值表如表2一1所示,再填入卡诺图表2一2中。 表2-1 A0000000011111111 B0000111100001111 c0011001100110011 D0101010101010101 Z0000000100010111

8 实验二 组合逻辑电路的设计与测试 一、实验目的 掌握组合逻辑电路的设计与测试方法 二、实验原理 1、使用中、小规模集成电路来设计组合电路是最常见的逻辑电路。设计组合电路 的一般步骤如图 2-1 所示。 图 2-1 组合逻辑电路设计流程图 根据设计任务的要求建立输入、输出变量,并列出真值表。然后用逻辑代数或卡 诺图化简法求出简化的逻辑表达式。并按实际选用逻辑门的类型修改逻辑表达式。 根 据简化后的逻辑表达式,画出逻辑图,用标准器件构成逻辑电路。最后,用实验来验 证设计的正确性。 2、组合逻辑电路设计举例 用“与非”门设计一个表决电路。当三个输入端中有两个或三个为“1”时,输 出端才为“1”。 设计步骤:根据题意列出真值表如表 2-1 所示,再填入卡诺图表 2-2 中。 表 2-1 A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Z 0 0 0 0 0 0 0 1 0 0 0 1 0 1 1 1