实验二门电路的逻辑功能测试及功能转换 一、实验目的 1.掌握门电路的逻辑功能及其测试方法 2.掌握门电路之间的功能转换方法 3.掌握特殊门电路的特性分析和设计 二、实验仪器和器件 1.AEDK-labDEC型数字电路实验箱 2.RIGOL-DS1042C型双踪示波器 3.万用表 4.器件: 74LS00 2输入端四与非门 1片 74LS86 2输入端四异或门 1片 74LS125 三态输出的四总线缓冲门 1片 010000100000010000000 141312111098 141312111098 141312111098 74LS00 74LS86 74LS125 buddituuuddotuuoddobu 567 567 三、实验内容 1.测试与非门和异或门电路的逻辑功能 2.用三个与非门构成一个或门电路: 3.用异或门构成非门电路: 4.测试三个异或门构成电路的输出: 5.测试三态门的逻辑功能。 四、实验过程及方法 1.测试与非门和异或门电路的逻辑功能,注意全部门都得测(步骤同实验一)

9 实验二 门电路的逻辑功能测试及功能转换 一、实验目的 1.掌握门电路的逻辑功能及其测试方法 2.掌握门电路之间的功能转换方法 3.掌握特殊门电路的特性分析和设计 二、 实验仪器和器件 1.AEDK-labDEC 型数字电路实验箱 2.RIGOL-DS1042C 型双踪示波器 3.万用表 4.器件: 74LS00 2 输入端四与非门 1 片 74LS86 2 输入端四异或门 1 片 74LS125 三态输出的四总线缓冲门 1 片 三、实验内容 1.测试与非门和异或门电路的逻辑功能; 2.用三个与非门构成一个或门电路; 3.用异或门构成非门电路; 4.测试三个异或门构成电路的输出; 5.测试三态门的逻辑功能。 四、实验过程及方法 1.测试与非门和异或门电路的逻辑功能,注意全部门都得测(步骤同实验一)。 14 13 12 11 10 9 8 74LS125 1 2 3 4 5 6 7 14 13 12 11 10 9 8 74LS86 1 2 3 4 5 6 7 14 13 12 11 10 9 8 74LS00 1 2 3 4 5 6 7

1)将“与非门”74LS00插入实验箱面板上(注意:凹口朝左),14脚接+5V,7 脚接地,并把两个输入端接实验箱的逻辑开关D1、D2,输出端接发光二极管(L0~ L11任意一个),如图2.1(a)所示。 2)按照表2.1(b)不同的输入组合,记录对应的输出信号,结果填入表2.1(a)。 3)按同样的方法,验证74LS86的逻辑功能,接线图如图2.1(b)所示,测试结 果填入表2.1(b). Vee Di D2 Lo Vee Di D2 Lo i111000 141312111098 141312111098 74LS00 74LS86 tt心iii中 UUUUUUU GND GND 图2.1(a)与非门功能测试接线图 2.1(b)异或门功能测试接线图 表2.1(a)与非门真值表 表2.1(b)异或门真值表 输入 输出 输入 输出 A B 上 A B V 0 0 0 0 1 0 0 4)按照上述方法分别测试74LS00的另外三对与非门,以及74LS86的另外三对 门异或门,都符合其真值表,说明芯片功能正常。 2.用与非门实现或门功能。 10

10 1)将“与非门”74LS00 插入实验箱面板上(注意:凹口朝左),14 脚接+5V,7 脚接地,并把两个输入端接实验箱的逻辑开关 D1、D2,输出端接发光二极管(L0~ L11 任意一个),如图 2.1(a)所示。 2)按照表 2.1(b)不同的输入组合,记录对应的输出信号,结果填入表 2.1(a)。 3)按同样的方法,验证 74LS86 的逻辑功能,接线图如图 2.1(b)所示,测试结 果填入表 2.1(b)。 图 2.1(a)与非门功能测试接线图 2.1(b)异或门功能测试接线图 表 2.1(a)与非门真值表 表 2.1(b) 异或门真值表 输入 输出 A B Y 0 0 1 0 1 1 1 0 1 1 1 0 4)按照上述方法分别测试 74LS00 的另外三对与非门,以及 74LS86 的另外三对 门异或门,都符合其真值表,说明芯片功能正常。 2.用与非门实现或门功能。 输入 输出 A B Y 0 0 0 0 1 1 1 0 1 1 1 0 14 13 12 11 10 9 8 74LS86 1 2 3 4 5 6 7 Vcc D1 D2 L0 GND 14 13 12 11 10 9 8 74LS00 1 2 3 4 5 6 7 Vcc D1 D2 L0 GND

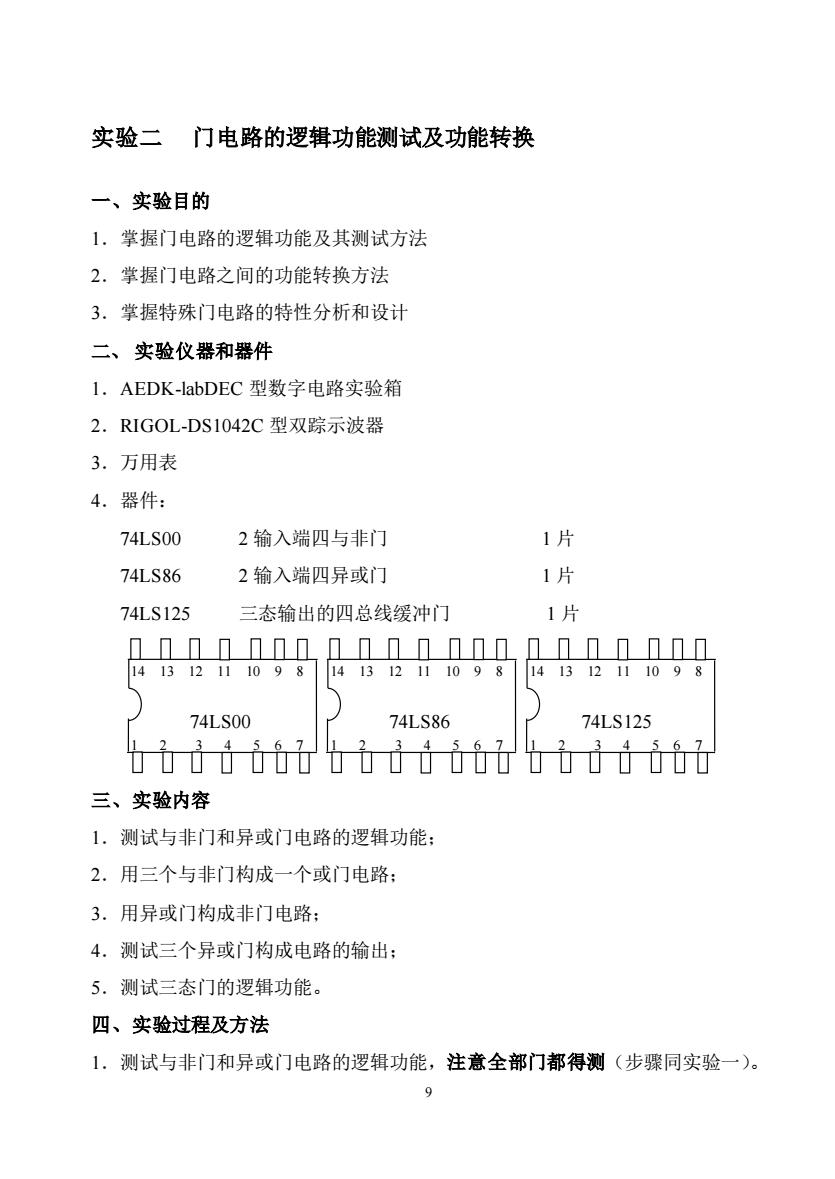

1)将“与非门”74LS00插入实验箱面板上(注意:凹口朝左),14脚接+5V,7 脚接地,并把两个输入端接实验箱的逻辑开关D1、D2,输出端接发光二极管L0 L11任意一个),逻辑电路图如图2.2(a)所示,接线图如图2.2(b)所示。 2)按照表2.2不同的输入组合,记录对应的输出信号,结果填入表2.2。其中D1 对应功能表中的A,D2对应B,Lo对应Y。 3)从功能表可知,该电路实现或门的功能。 3.用异或门实现非门功能 1)将“异或门”74LS86插入实验箱面板上(注意:凹口朝左),14脚接+5V,7 脚接地,并把1个输入端接实验箱的逻辑开关D1、另一个输入端接高电平,输出 端接发光二极管(Lo~L1任意一个),逻辑电路图如图2.3(a)所示,接线图如 图2.3(b)所示。 2)按照表2.3不同的输入组合,记录对应的输出信号,结果填入表2.3。其中D1 对应功能表中的A,Lo对应Y。 3)从功能表可知,该电路实现非门的功能。 图2.2(a)与非门实现或门测试电路 图2.3(a)与非门实现非门测试电路

11 1)将“与非门”74LS00 插入实验箱面板上(注意:凹口朝左),14 脚接+5V,7 脚接地,并把两个输入端接实验箱的逻辑开关 D1、D2,输出端接发光二极管 L0~ L11 任意一个),逻辑电路图如图 2.2(a)所示,接线图如图 2.2(b)所示。 2)按照表 2.2 不同的输入组合,记录对应的输出信号,结果填入表 2.2。其中 D1 对应功能表中的 A ,D2 对应 B,L0 对应 Y。 3)从功能表可知,该电路实现或门的功能。 3.用异或门实现非门功能 1)将“异或门”74LS86 插入实验箱面板上(注意:凹口朝左),14 脚接+5V,7 脚接地,并把 1 个输入端接实验箱的逻辑开关 D1、另一个输入端接高电平,输出 端接发光二极管(L0~L11 任意一个),逻辑电路图如图 2.3(a)所示,接线图如 图 2.3(b)所示。 2)按照表 2.3 不同的输入组合,记录对应的输出信号,结果填入表 2.3。其中 D1 对应功能表中的 A , L0 对应 Y。 3)从功能表可知,该电路实现非门的功能。 图 2.2(a)与非门实现或门测试电路 图 2.3(a)与非门实现非门测试电路 & & & A B Y Y A 1 =1

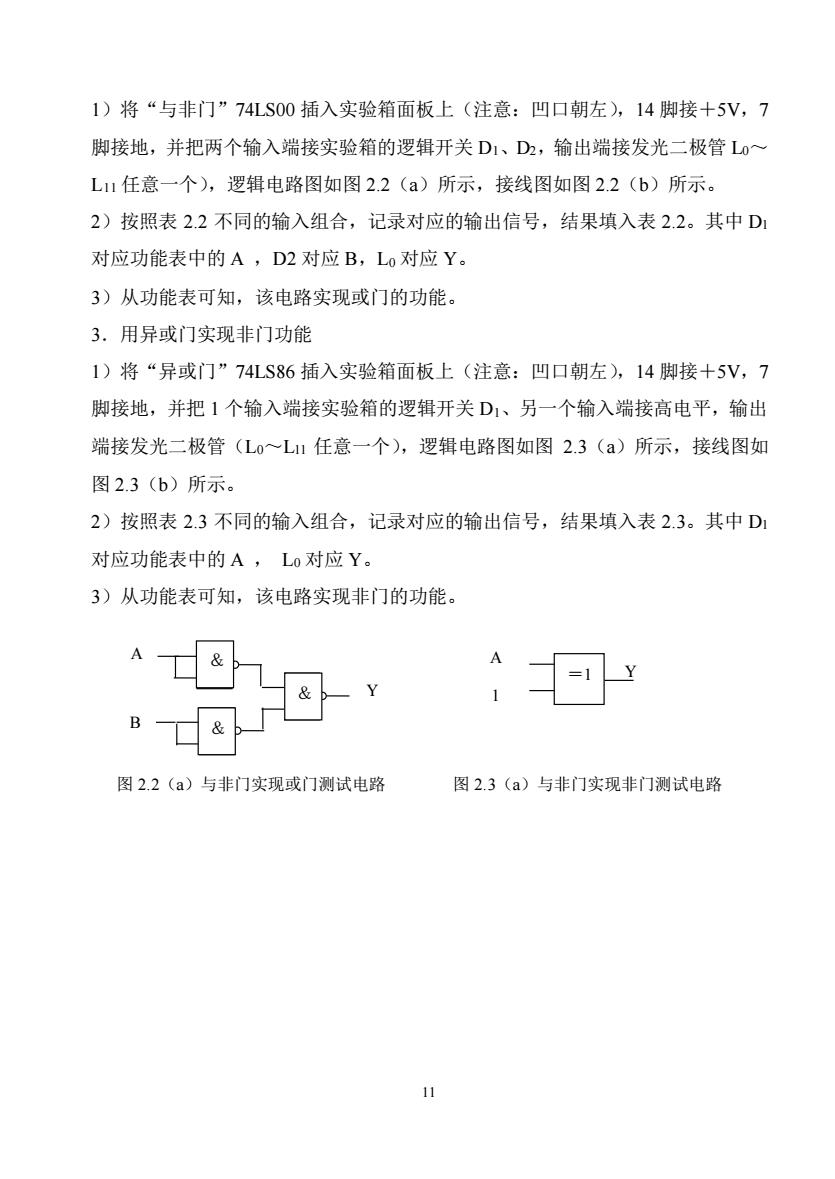

Vee D D2 Vee Di Vee Lo 4131211109 1413121109 74LS00 74LS86 34567 2 34567 中IUUU UUUUUUU GND GND 图2.2(b)与非门实现或门接线图2.3(b)异或门实现非门接线图 表2.2与非门实现或门真值表 表2.3异或门实现非门真值表 输入 输出 输入输出 A B Y A 0 0 1 0 0 4.测试三个异或门构成的小规模组合电路的输出,结果填入表2.4。 1)将“异或门”74LS86插入实验箱面板上,14脚接+5V,7脚接地,并把4个 输入端接实验箱的逻辑开关D1、D2、D4、D5,输出端接发光二极管(L0~L1任 意一个),逻辑电路图如图2.4(a)所示,接线图如图2.4(b)所示。 2)按照表2.4不同的输入组合,记录对应的输出信号,结果填入表2.4。 2=1 图2.4(a)三个异或门构成的测试电路

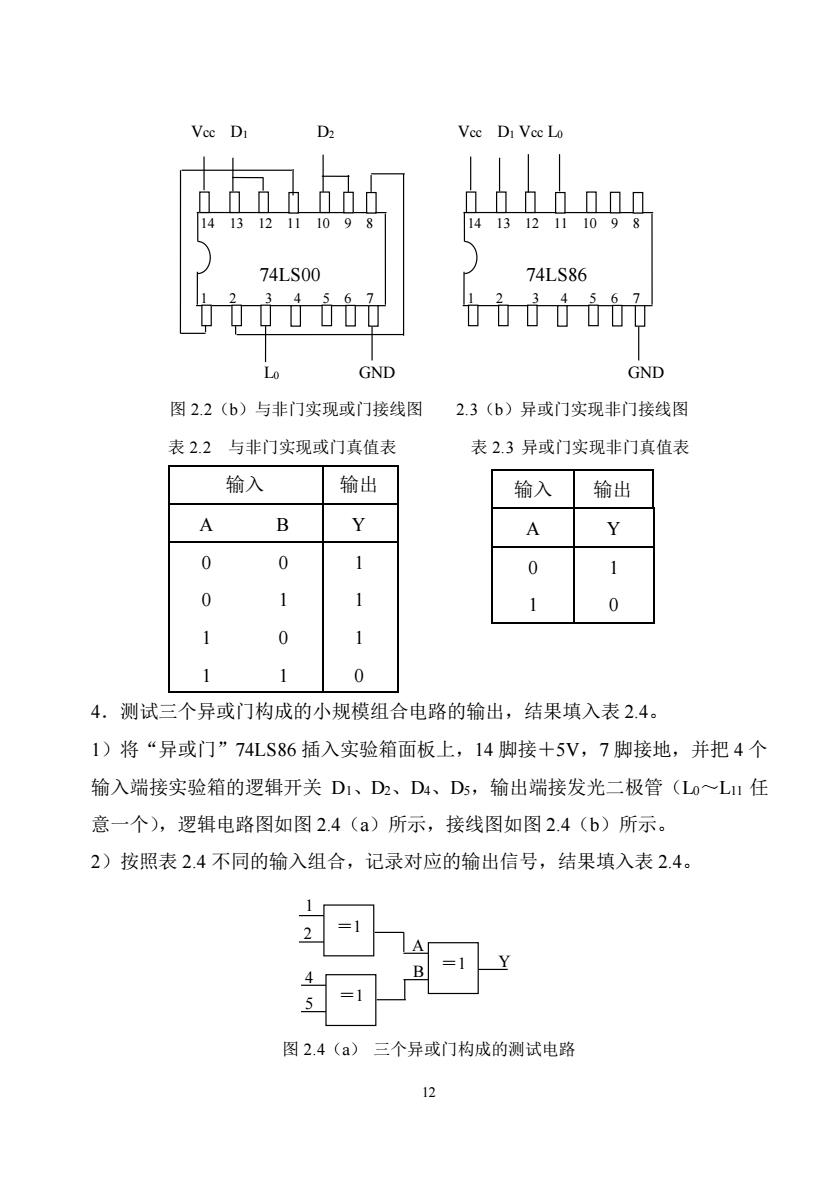

12 图 2.2(b)与非门实现或门接线图 2.3(b)异或门实现非门接线图 表 2.2 与非门实现或门真值表 表 2.3 异或门实现非门真值表 输入 输出 A B Y 0 0 1 0 1 1 1 0 1 1 1 0 4.测试三个异或门构成的小规模组合电路的输出,结果填入表 2.4。 1)将“异或门”74LS86 插入实验箱面板上,14 脚接+5V,7 脚接地,并把 4 个 输入端接实验箱的逻辑开关 D1、D2、D4、D5,输出端接发光二极管(L0~L11 任 意一个),逻辑电路图如图 2.4(a)所示,接线图如图 2.4(b)所示。 2)按照表 2.4 不同的输入组合,记录对应的输出信号,结果填入表 2.4。 图 2.4(a) 三个异或门构成的测试电路 输入 输出 A Y 0 1 1 0 14 13 12 11 10 9 8 74LS86 1 2 3 4 5 6 7 Vcc D1 Vcc L0 GND 14 13 12 11 10 9 8 74LS00 1 2 3 4 5 6 7 Vcc D1 D2 L0 GND Y B A 5 4 2 1 =1 =1 =1

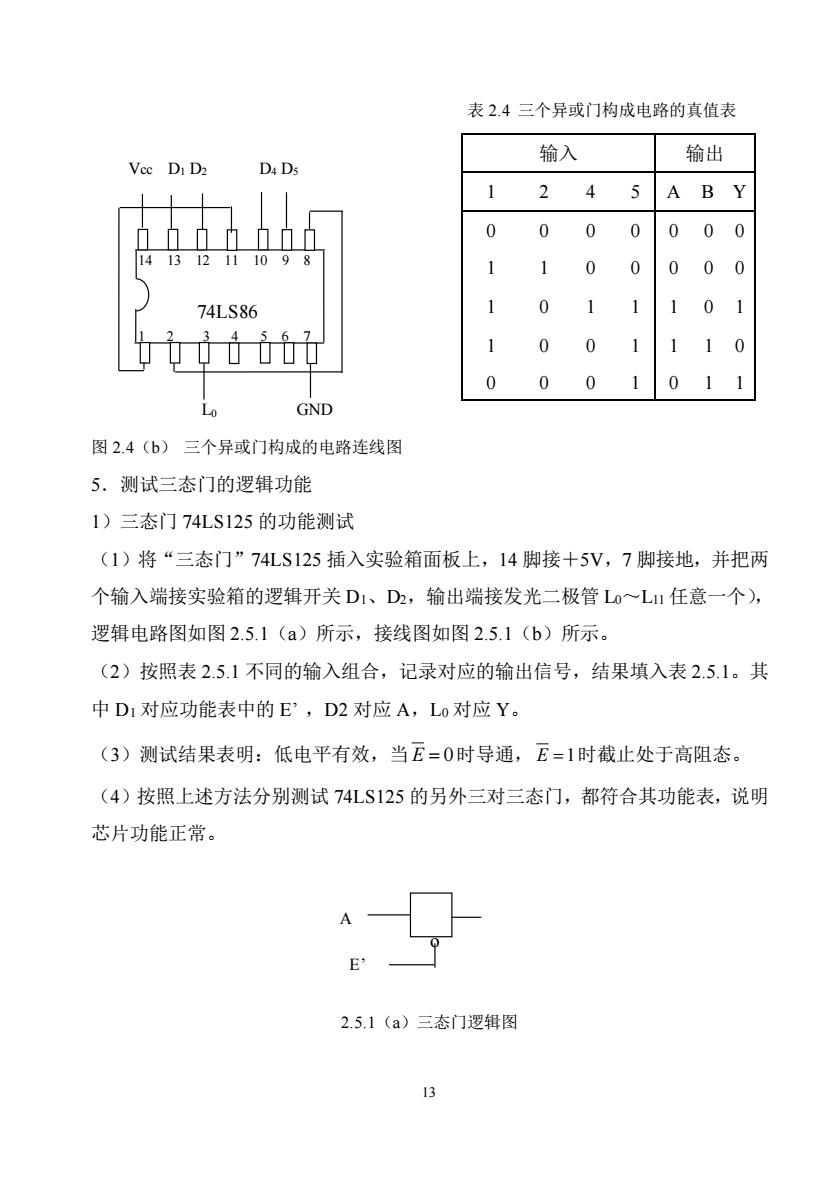

表2.4三个异或门构成电路的真值表 输入 输出 Vee Di D2 12 4 5A B Y 0000000 141312111098 1 10 0 000 74Ls86 1 011101 001110 0 001011 Lo GND 图2.4(b)三个异或门构成的电路连线图 5.测试三态门的逻辑功能 1)三态门74LS125的功能测试 (1)将“三态门”74LS125插入实验箱面板上,14脚接+5V,7脚接地,并把两 个输入端接实验箱的逻辑开关D1、D2,输出端接发光二极管L0~L山任意一个), 逻辑电路图如图2.5.1(a)所示,接线图如图2.5.1(b)所示。 (2)按照表2.5.1不同的输入组合,记录对应的输出信号,结果填入表2.5.1。其 中D1对应功能表中的E,D2对应A,Lo对应Y。 (3)测试结果表明:低电平有效,当E=0时导通,E=1时截止处于高阻态。 (4)按照上述方法分别测试74LS125的另外三对三态门,都符合其功能表,说明 芯片功能正常。 E 2.5.1(a)三态门逻辑图

13 表 2.4 三个异或门构成电路的真值表 图 2.4(b) 三个异或门构成的电路连线图 5.测试三态门的逻辑功能 1)三态门 74LS125 的功能测试 (1)将“三态门”74LS125 插入实验箱面板上,14 脚接+5V,7 脚接地,并把两 个输入端接实验箱的逻辑开关 D1、D2,输出端接发光二极管 L0~L11 任意一个), 逻辑电路图如图 2.5.1(a)所示,接线图如图 2.5.1(b)所示。 (2)按照表 2.5.1 不同的输入组合,记录对应的输出信号,结果填入表 2.5.1。其 中 D1 对应功能表中的 E’ ,D2 对应 A,L0 对应 Y。 (3)测试结果表明:低电平有效,当 E = 0 时导通, E =1 时截止处于高阻态。 (4)按照上述方法分别测试 74LS125 的另外三对三态门,都符合其功能表,说明 芯片功能正常。 2.5.1(a)三态门逻辑图 输入 输出 1 2 4 5 A B Y 0 0 0 0 0 0 0 1 1 0 0 0 0 0 1 0 1 1 1 0 1 1 0 0 1 1 1 0 0 0 0 1 0 1 1 14 13 12 11 10 9 8 74LS86 1 2 3 4 5 6 7 Vcc D1 D2 D4 D5 L0 GND A o E’