表2.3三态门功能表 Vee Di D2 Lo 输入 输出 n h ha n nn E A 141312111098 0 74LS125 bddob时 0 Z GND 2.5.1(b)三态门测试连线图 2)功能分析。当E=1时,三态门截止处于高阻态,输出状态由1B端的输入确定, 如图2.5.2(a)所示。按图2.5.2(b)的连线图连接电路,试测试当1B=1和1B=0 时,Z的输出(用示波器测)。其中开关K,控制74LS00的输入端口B,74LS125 输出端口Z接示波器测试,测试结果如表2.4所示。 74LS125 74LS00 74LS125 74LS00 7 0 1A 1Y IY 1Y 2.5.2(a)三态门功能分析的逻辑电路图

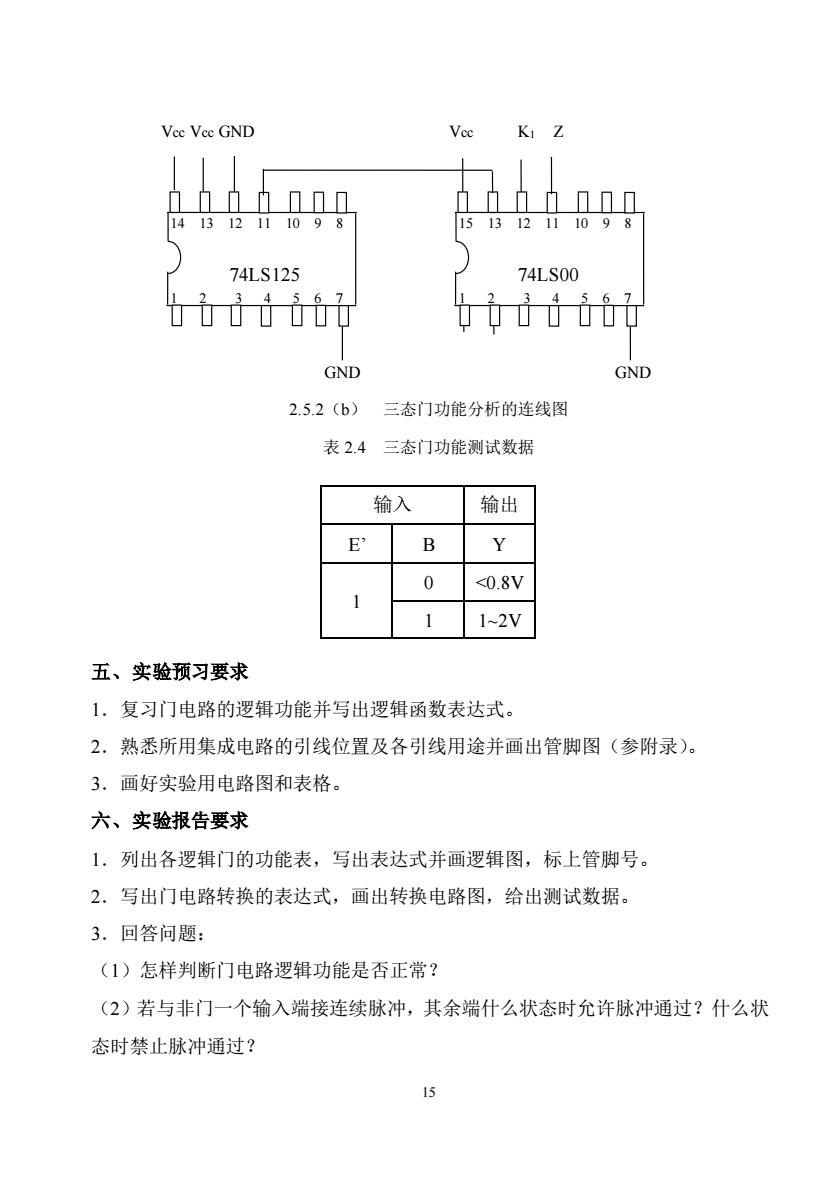

14 表 2.3 三态门功能表 2.5.1(b)三态门测试连线图 2)功能分析。当 E =1 时,三态门截止处于高阻态,输出状态由 1B 端的输入确定, 如图 2.5.2(a)所示。按图 2.5.2(b)的连线图连接电路,试测试当 1B=1 和 1B=0 时,Z 的输出(用示波器测)。其中开关 K1控制 74LS00 的输入端口 B,74LS125 输出端口 Z 接示波器测试,测试结果如表 2.4 所示。 2.5.2(a) 三态门功能分析的逻辑电路图 输入 输出 E’ A Y 0 0 0 1 1 1 0 Z 1 Z 14 13 12 11 10 9 8 74LS125 1 2 3 4 5 6 7 Vcc D1 D2 L0 GND 0 Z 1A 1Y 1 E 1 G 1A 1Y 1B 1 G 1 74LS125 74LS00 1 0 Z 1A 1Y 1 E 1 G 1A 1Y 1B 1 G 1 74LS125 74LS00 0

VeeVee GND Vee KI Z i111000 1111000 141312111098 151312111098 74LS125 74LS00 UU0UUUU biuduou GND GND 2.5.2(b) 三态门功能分析的连线图 表2.4三态门功能测试数据 输入 输出 E B Y 0 <08V 1 1-2V 五、实验预习要求 1.复习门电路的逻辑功能并写出逻辑函数表达式。 2.熟悉所用集成电路的引线位置及各引线用途并画出管脚图(参附录)。 3.画好实验用电路图和表格。 六、实验报告要求 1.列出各逻辑门的功能表,写出表达式并画逻辑图,标上管脚号。 2.写出门电路转换的表达式,画出转换电路图,给出测试数据。 3.回答问题: (1)怎样判断门电路逻辑功能是否正常? (2)若与非门一个输入端接连续脉冲,其余端什么状态时允许脉冲通过?什么状 态时禁止脉冲通过? 15

15 2.5.2(b) 三态门功能分析的连线图 表 2.4 三态门功能测试数据 五、实验预习要求 1.复习门电路的逻辑功能并写出逻辑函数表达式。 2.熟悉所用集成电路的引线位置及各引线用途并画出管脚图(参附录)。 3.画好实验用电路图和表格。 六、实验报告要求 1.列出各逻辑门的功能表,写出表达式并画逻辑图,标上管脚号。 2.写出门电路转换的表达式,画出转换电路图,给出测试数据。 3.回答问题: (1)怎样判断门电路逻辑功能是否正常? (2)若与非门一个输入端接连续脉冲,其余端什么状态时允许脉冲通过?什么状 态时禁止脉冲通过? 输入 输出 E’ B Y 1 0 <0.8V 1 1~2V 14 13 12 11 10 9 8 74LS125 1 2 3 4 5 6 7 Vcc Vcc GND GND 15 13 12 11 10 9 8 74LS00 1 2 3 4 5 6 7 Vcc K1 Z GND