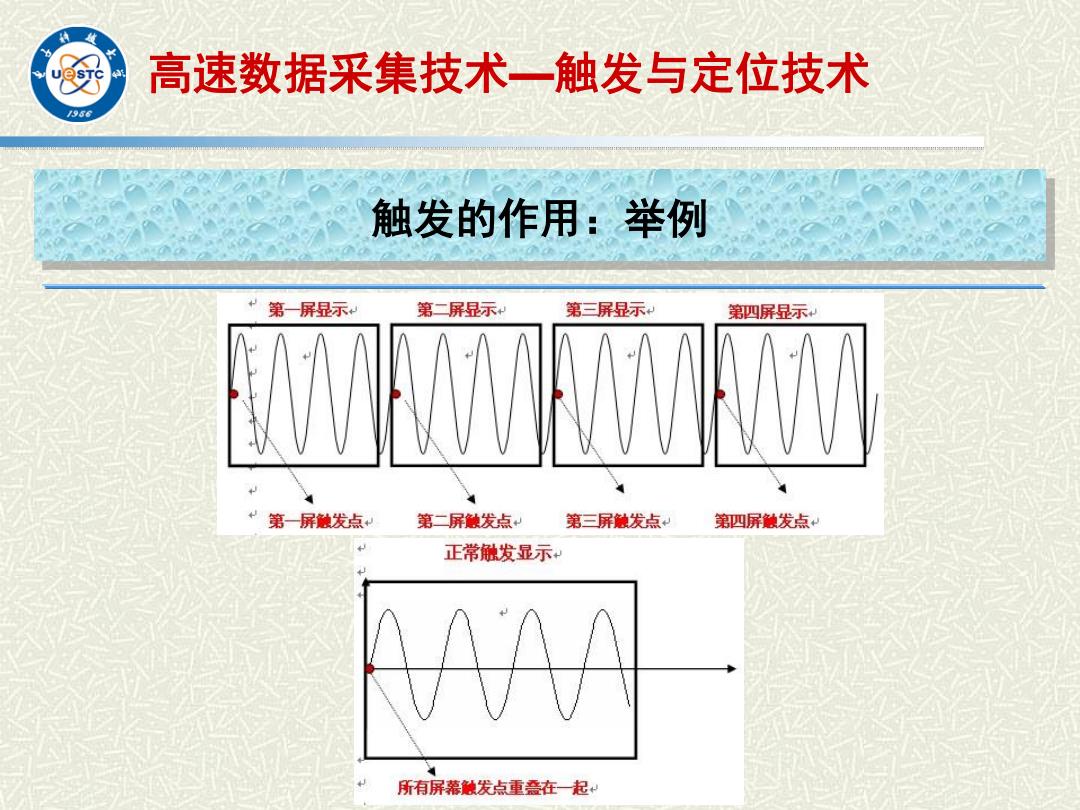

高速数据采集技术一触发与定位技术 触发的作用:举例 第一屏显示 第二屏显示 第三屏显示 第四屏显示 第一屏触发点 第二屏触发点 第三屏触发点。 第四屏触发点 正常触发显示 斗 所有屏幕触发点重意在一起+

触发的作用:举例 高速数据采集技术—触发与定位技术

高速数据采集技术一触发与定位技术 /96 触发是数字示波器区别于模拟示波器的最大特征之一 模拟示波器:只有简单的边沿触发。没有存储单元,触发只是示波 器显示波形的一个起始信号,单单定义了波形的起点。 数字存储示波器:把模拟信号数字化,由于有数据存储,并可以定 义触发点在内存中的位置,可以看到触发之前的波形,可以设置更 多更复杂的触发类型,满足不同特征波形的触发和观察。 怎样正确的设置触发条件来观察不同特征的波形呢? 先回顾一下触发电路

触发是数字示波器区别于模拟示波器的最大特征之一 模拟示波器:只有简单的边沿触发。没有存储单元,触发只是示波 器显示波形的一个起始信号,单单定义了波形的起点。 数字存储示波器:把模拟信号数字化,由于有数据存储,并可以定 义触发点在内存中的位置,可以看到触发之前的波形,可以设置更 多更复杂的触发类型,满足不同特征波形的触发和观察。 怎样正确的设置触发条件来观察不同特征的波形呢? 先回顾一下触发电路。 高速数据采集技术—触发与定位技术

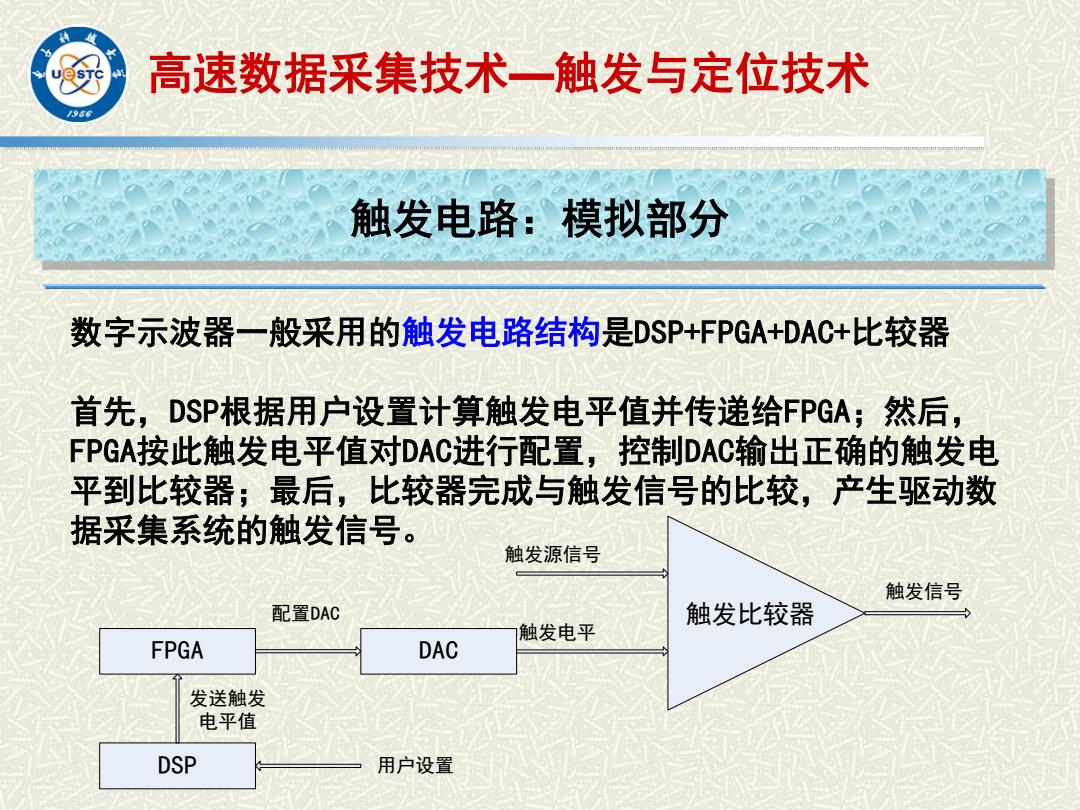

高速数据采集技术一触发与定位技术 触发电路:模拟部分 数字示波器一般采用的触发电路结构是DSP+FPGA+DAC+比较器 首先,DSP根据用户设置计算触发电平值并传递给FPGA;然后, FPGA按此触发电平值对DAC进行配置,控制DAC输出正确的触发电 平到比较器;最后,比较器完成与触发信号的比较,产生驱动数 据采集系统的触发信号。 触发源信号 触发信号 配置DAC 触发比较器 触发电平 FPGA DAC 发送触发 电平值 DSP 用户设置

触发电路:模拟部分 数字示波器一般采用的触发电路结构是DSP+FPGA+DAC+比较器 首先,DSP根据用户设置计算触发电平值并传递给FPGA;然后, FPGA按此触发电平值对DAC进行配置,控制DAC输出正确的触发电 平到比较器;最后,比较器完成与触发信号的比较,产生驱动数 据采集系统的触发信号。 FPGA DSP DAC 用户设置 触发比较器 触发源信号 触发电平 配置DAC 发送触发 电平值 触发信号 高速数据采集技术—触发与定位技术

高速数据采集技术一触发与定位技术 触发电路:数字部分 触发信号控制采集 FPGA、FIFO实现 采集的数字化信号遵循先进先出的原理存储到示波器内存(FIF0) 中去。 存储过程: 采满预触发深度之前,存储器只进不出; 采满预触发深度之后,触发信号到来之前,存储器边出边进; 触发到来之后,存储器只进不出,直到存满存储深度为止; 存满之后,存储器只出不进,取出数据画波形并显示。 存储器起点到触发点这段时间记录的波形数据就是触发前的波形信 息,即预触发。而触发点到存储器终点的波形称之为后触发

触发电路:数字部分 触发信号控制采集——FPGA、FIFO实现 采集的数字化信号遵循先进先出的原理存储到示波器内存(FIFO) 中去。 存储过程: 采满预触发深度之前,存储器只进不出; 采满预触发深度之后,触发信号到来之前,存储器边出边进; 触发到来之后,存储器只进不出,直到存满存储深度为止; 存满之后,存储器只出不进,取出数据画波形并显示。 存储器起点到触发点这段时间记录的波形数据就是触发前的波形信 息,即预触发。而触发点到存储器终点的波形称之为后触发。 高速数据采集技术—触发与定位技术

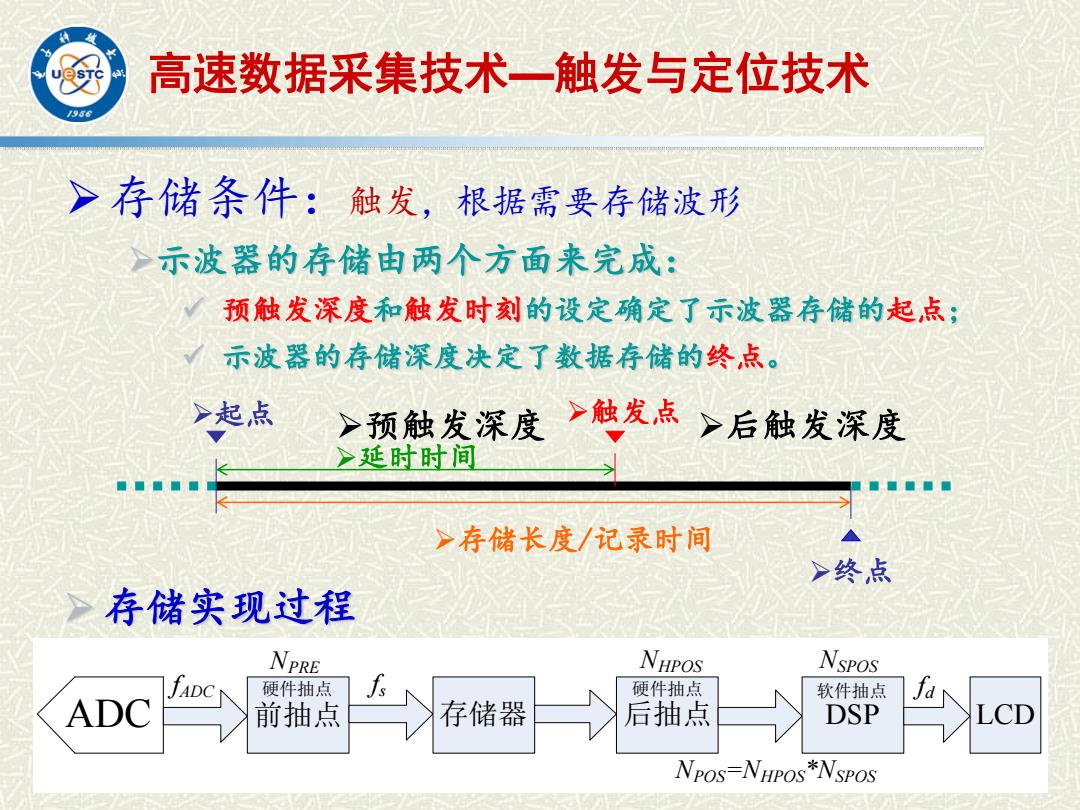

高速数据采集技术一触发与定位技术 1986 >存储条件:触发,根据需要存储波形 示波器的存储由两个方面来完成: 预触发深度和触发时刻的设定确定了示波器存储的起,点: 示波器的存储深度决定了数据存储的终,点。 >起点 >预触发深度 >触发点 >后触发深度 >延时时间 >存储长度/记录时间 >终点 存储实现过程 NPRE NHPOS NsPOS 硬件抽点 硬件抽点 软件抽点 ADC 前抽点 存储器 后抽点 DSP LCD NPOS-NHPOS*NSPOS

存储条件:触发,根据需要存储波形 示波器的存储由两个方面来完成: 预触发深度和触发时刻的设定确定了示波器存储的起点; 示波器的存储深度决定了数据存储的终点。 触发点 延时时间 存储长度/记录时间 起点 终点 预触发深度 后触发深度 存储实现过程 ADC 前抽点 存储器 后抽点 DSP fADC NPRE fs NHPOS fd LCD NSPOS NPOS=NHPOS*NSPOS 硬件抽点 硬件抽点 软件抽点 高速数据采集技术—触发与定位技术