该窗口为建立的项目信息,点击下iish”项目建立完毕。 建立工程后,可以使用Assignments菜单下的settings对话框对工程设置进行修改。 2.输入文本文件 新建VHDL文本文件:在QuartusII管理器界面中选择菜单File\New.,或单击新 建文件按钮,出现New对话框,在对话框Device Design Files中选择VHDL File。点 击ok按纽,打开编辑器。在文本编辑器窗口下,编辑输入2输入与非门的VHDL程 序。如图2.3.6所示。 可反y8心g©~9。合a 图2.3.6新建设计文件选择窗口和文本编辑窗口 QuatusII还提供了文本文件编辑模板,使用模板可快速准确地创建VHDL文本文 件,避免语法错误,提高编辑效率。选择菜单Editnsert Template.,打开Insert Template 对话框,点击右侧Language Template栏目打开VHDL,VHDL栏目下显示出所有VHDL 的程序模板,选择合适的模板,并在此基础上进行修改。 编辑完毕后保存,文件名保存为naud2lab1”,VHDL文件的扩展名为.vhd。 QuartusII支持多种硬件描述语言,不同的硬件描述语言编写的文件扩展名不同, 如AHDL文件扩展名为.tdf,Verilog HDL文件扩展名为.v,VHDL文件的扩展名为.vhd。 (注:文件名必须与程序中实体名一致) 选中“Add file to current project'"选项,添加当前文件到项目。 添加或删除与当前项目有关的文件的具体操作: 添加文件:如果希望将存放在别处的文件加入到当前的设计项目中,选择菜单 Assignments\Settings.,打开如图所示的Settings对话框。如图2.3.7。 图2.3,7将文件加入到当前的设计项目中

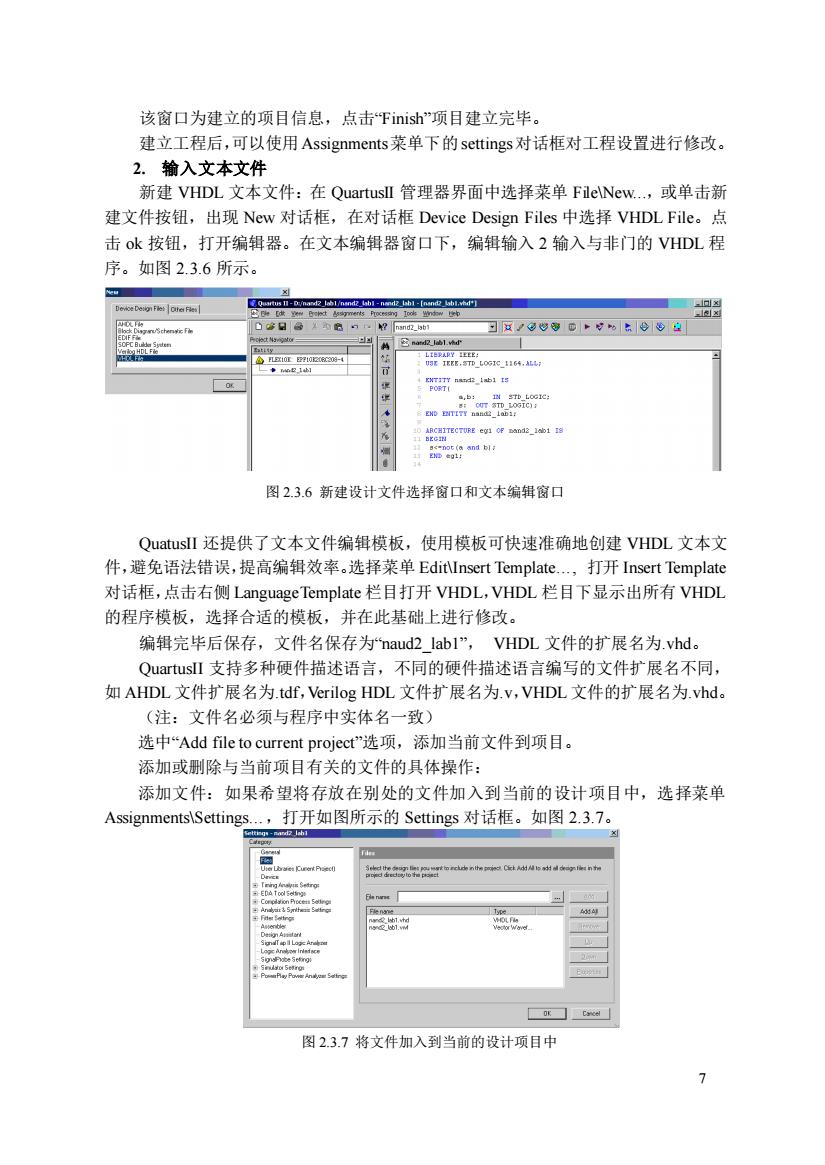

7 该窗口为建立的项目信息,点击“Finish”项目建立完毕。 建立工程后,可以使用Assignments菜单下的settings对话框对工程设置进行修改。 2. 输入文本文件 新建 VHDL 文本文件:在 QuartusII 管理器界面中选择菜单 File\New.,或单击新 建文件按钮,出现 New 对话框,在对话框 Device Design Files 中选择 VHDL File。点 击 ok 按钮,打开编辑器。在文本编辑器窗口下,编辑输入 2 输入与非门的 VHDL 程 序。如图 2.3.6 所示。 图 2.3.6 新建设计文件选择窗口和文本编辑窗口 QuatusII 还提供了文本文件编辑模板,使用模板可快速准确地创建 VHDL 文本文 件,避免语法错误,提高编辑效率。选择菜单 Edit\Insert Template., 打开 Insert Template 对话框,点击右侧 LanguageTemplate 栏目打开 VHDL,VHDL 栏目下显示出所有 VHDL 的程序模板,选择合适的模板,并在此基础上进行修改。 编辑完毕后保存,文件名保存为“naud2_lab1”, VHDL 文件的扩展名为.vhd。 QuartusII 支持多种硬件描述语言,不同的硬件描述语言编写的文件扩展名不同, 如 AHDL 文件扩展名为.tdf,Verilog HDL 文件扩展名为.v,VHDL 文件的扩展名为.vhd。 (注:文件名必须与程序中实体名一致) 选中“Add file to current project”选项,添加当前文件到项目。 添加或删除与当前项目有关的文件的具体操作: 添加文件:如果希望将存放在别处的文件加入到当前的设计项目中,选择菜单 Assignments\Settings.,打开如图所示的 Settings 对话框。如图 2.3.7。 图 2.3.7 将文件加入到当前的设计项目中

在Settings对话框左侧的Cagegory栏目下选择Files项,通过右边File Name栏的 “.”按钮查找文件选项,点击Add按钮添加文件。Add All按钮的作用是将当前目录 下的所有文件添加到项目中。 别除文件:如果希望将当前项目中的文件从项目中删除,首先选中待删除文件, Remove按钮则被激活,点击Remove按钮即可。 其它功能设置:在Settings对话框下,除了可以进行设计项目的文件设置外,还 可以进行与设计有关的各种其它功能设置,如:库Libraries、器件Device、EDA工具 EDA Tool、编译Compilation、分析与综合Analysis&Synthesis、定时分析Time Analysis 仿真Simulator、配置Fitting等设置。 3.设计项目编译 保存文件后,选择“Project""菜单,点击Set as Top-Level Entity”项,把当前文件设 置为顶层实体。如图2.38所示。 △® ene 图23.8将当前文件设置为顶层文件 注:Ouartus环境下所有操作(综合、编译、仿真等)都只对顶层实体进行,所以 编辑任何程序前,必须先设置该选项,把当前要编译的文件设置为顶层实体后,才能 对该文件进行编译等操作。 打开Processing'”菜单,点击“Start Compilation'”执行完全编译,如图2.3.9,编译器 将运行预先指定的各个模块的功能,运行顺序依次为:编译网表提取、数据库建立、 逻辑综合、逻辑适配、定时模拟网表文件的提取、装配。 Ctrl+Shift I Start Complation Ctrl+L ☑Analyze Current Eie 图2.3.9设计项目编译 编译成功后,编译器产生相应的输出文件。若有错误,编译器停止编译,并给出

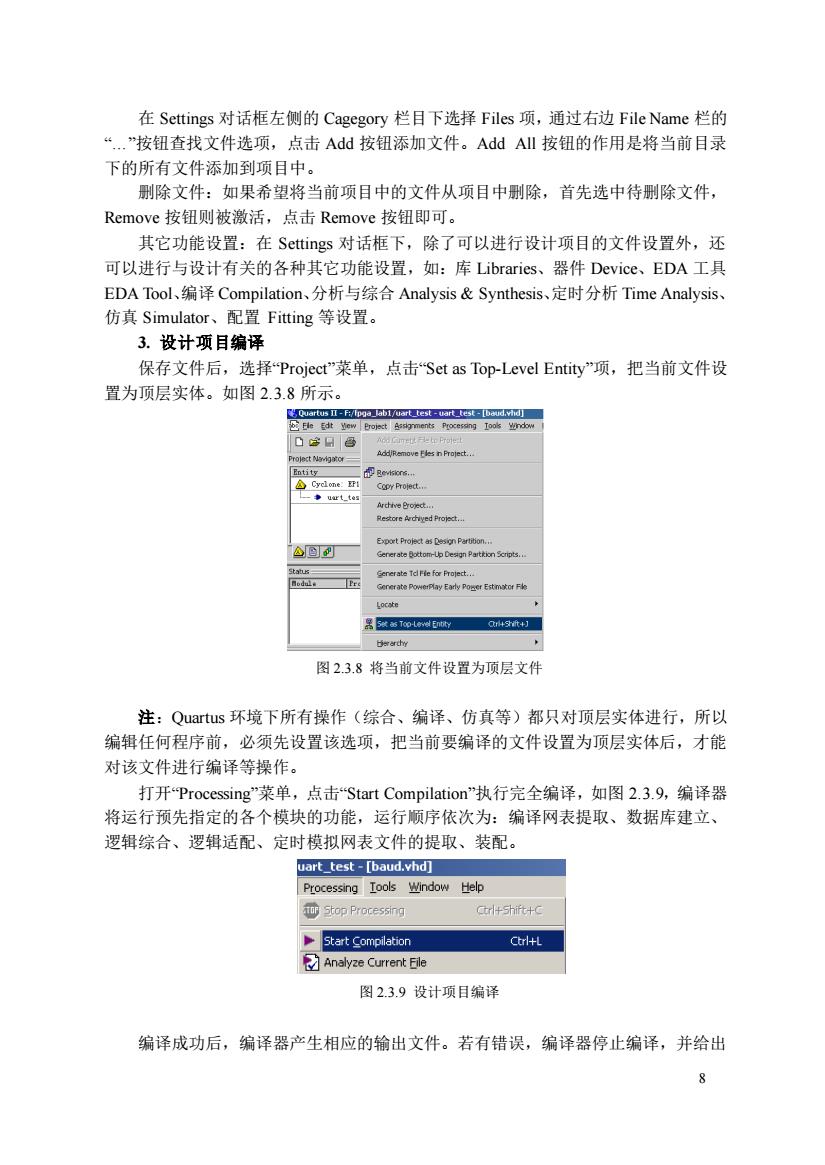

8 在 Settings 对话框左侧的 Cagegory 栏目下选择 Files 项,通过右边 File Name 栏的 “.”按钮查找文件选项,点击 Add 按钮添加文件。Add All 按钮的作用是将当前目录 下的所有文件添加到项目中。 删除文件:如果希望将当前项目中的文件从项目中删除,首先选中待删除文件, Remove 按钮则被激活,点击 Remove 按钮即可。 其它功能设置:在 Settings 对话框下,除了可以进行设计项目的文件设置外,还 可以进行与设计有关的各种其它功能设置,如:库 Libraries、器件 Device、EDA 工具 EDA Tool、编译 Compilation、分析与综合 Analysis & Synthesis、定时分析 Time Analysis、 仿真 Simulator、配置 Fitting 等设置。 3. 设计项目编译 保存文件后,选择“Project”菜单,点击“Set as Top-Level Entity”项,把当前文件设 置为顶层实体。如图 2.3.8 所示。 图 2.3.8 将当前文件设置为顶层文件 注:Quartus 环境下所有操作(综合、编译、仿真等)都只对顶层实体进行,所以 编辑任何程序前,必须先设置该选项,把当前要编译的文件设置为顶层实体后,才能 对该文件进行编译等操作。 打开“Processing”菜单,点击“Start Compilation”执行完全编译,如图 2.3.9,编译器 将运行预先指定的各个模块的功能,运行顺序依次为:编译网表提取、数据库建立、 逻辑综合、逻辑适配、定时模拟网表文件的提取、装配。 图 2.3.9 设计项目编译 编译成功后,编译器产生相应的输出文件。若有错误,编译器停止编译,并给出

错误信息,双击错误信息条,可给出错误之处,根据“Messages”消息栏给出的错误提 示修改程序,保存后再次编译,直至所有错误均改正后,系统会弹出编译结束窗口, 显示零错误零警告(一般警告信息可以忽略),单击“确定”按钮,出现编怪状态显示窗 口,如图2.3.10,编译报告给出所有编译结果,包括硬件信息、资源占用率等信息。 er 图23.10编译状态显示窗口 4.设计项目波形仿真 波形仿真是在波形编辑器中将设计的逻辑功能用波形图的形式显示,通过查看波 形图,检查设计的逻辑功能是否符合设计要求。 波形仿真的目的是进一步检验设计文件描述的逻辑功能能否实现预期的目标。波 形仿真分析是验证逻辑功能正确性必不可少的环节。 波形仿真的步骤包括新建波形文件、设置波形仿真器、插入仿真节点、编辑输入 波形、运行仿真器、检查输出波形是否符合设计要求。 1)建立波形图文件 关闭编译报告窗口后,在“文件”菜单下选择New”,选中“other files'标签页,在 弹出的窗口点击“Vector Waveform File'”点击OK”打开波形编辑窗口,如图2.3.1l。 。 图2.3.11新建波形图编辑窗口 9

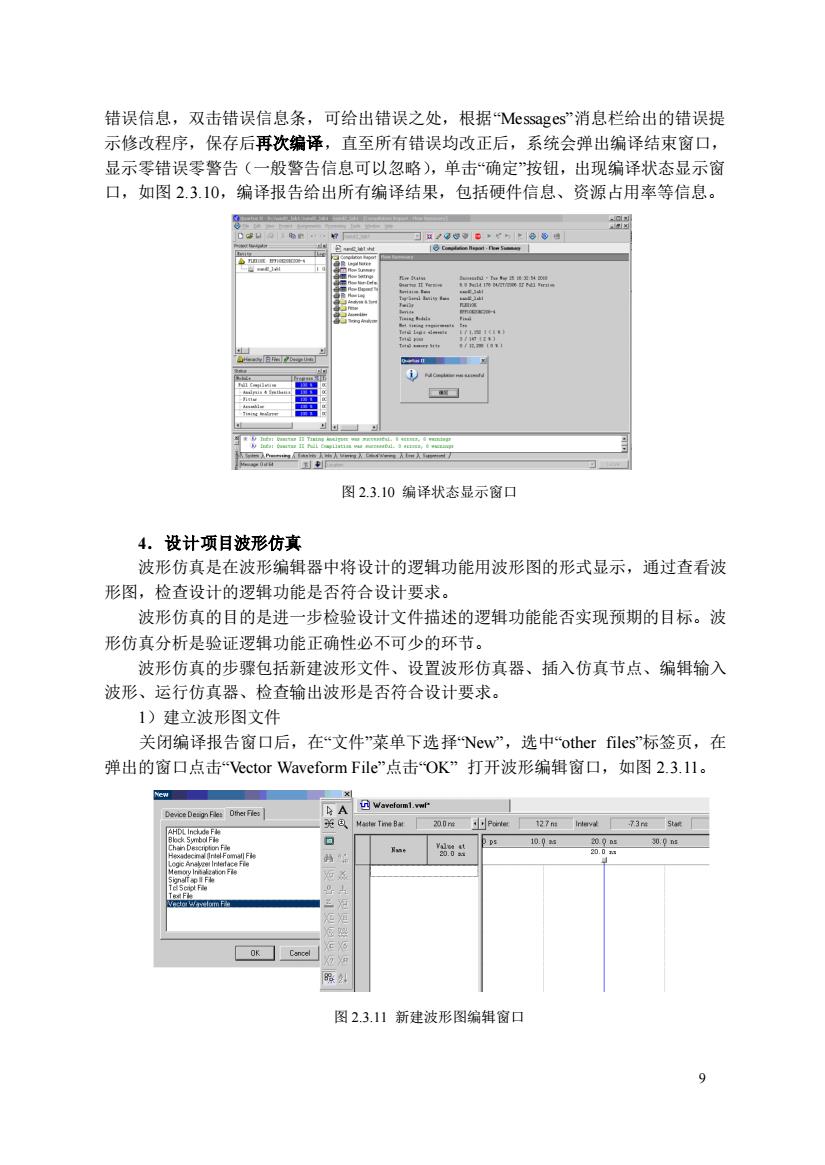

9 错误信息,双击错误信息条,可给出错误之处,根据“Messages”消息栏给出的错误提 示修改程序,保存后再次编译,直至所有错误均改正后,系统会弹出编译结束窗口, 显示零错误零警告(一般警告信息可以忽略),单击“确定”按钮,出现编译状态显示窗 口,如图 2.3.10,编译报告给出所有编译结果,包括硬件信息、资源占用率等信息。 图 2.3.10 编译状态显示窗口 4.设计项目波形仿真 波形仿真是在波形编辑器中将设计的逻辑功能用波形图的形式显示,通过查看波 形图,检查设计的逻辑功能是否符合设计要求。 波形仿真的目的是进一步检验设计文件描述的逻辑功能能否实现预期的目标。波 形仿真分析是验证逻辑功能正确性必不可少的环节。 波形仿真的步骤包括新建波形文件、设置波形仿真器、插入仿真节点、编辑输入 波形、运行仿真器、检查输出波形是否符合设计要求。 1)建立波形图文件 关闭编译报告窗口后,在“文件”菜单下选择“New”,选中“other files”标签页,在 弹出的窗口点击“Vector Waveform File”点击“OK” 打开波形编辑窗口,如图 2.3.11。 图 2.3.11 新建波形图编辑窗口

2)定义仿真观测的输入输出节点 在波形编辑窗口左侧栏的Name栏目下单击鼠标右键,出现浮动菜单,选择 Insert\Insert Note or Bus.”出现"Insert Note or Bus.”对话框,点击Node Finder.”按 键,出现Node Finder'”对话框,如图2.3.l2,查找节点信息,插入节点。 在图中Filter:”选项下选择管脚类型为Pins:all",然后单击List按钮,可在左 下侧区域看到设计项目中的输入输出信号,单击按钮=)”,将这些信号选择到 Selected Nodes'”区,表示对这些信号进行观测。 Node Finder Found Node 图2.3.12“Insert Note or Bus-.”插入节点对话 单击OK,出现波形编辑窗口,如图2.2.13。 》 00 图2.3.13波形编辑窗口 保存波形文件,文件名为nand2labl.vwf(注:扩展名默认不填,文件名与项目名同 名) 3)为输入信号赋值 波形编辑器窗口左侧为信号赋值工具条,根据实际要求点选工具按钮对输入信号 赋值。 为方便赋值,先浏览一下与此有关的工具条按钮和菜单。 10

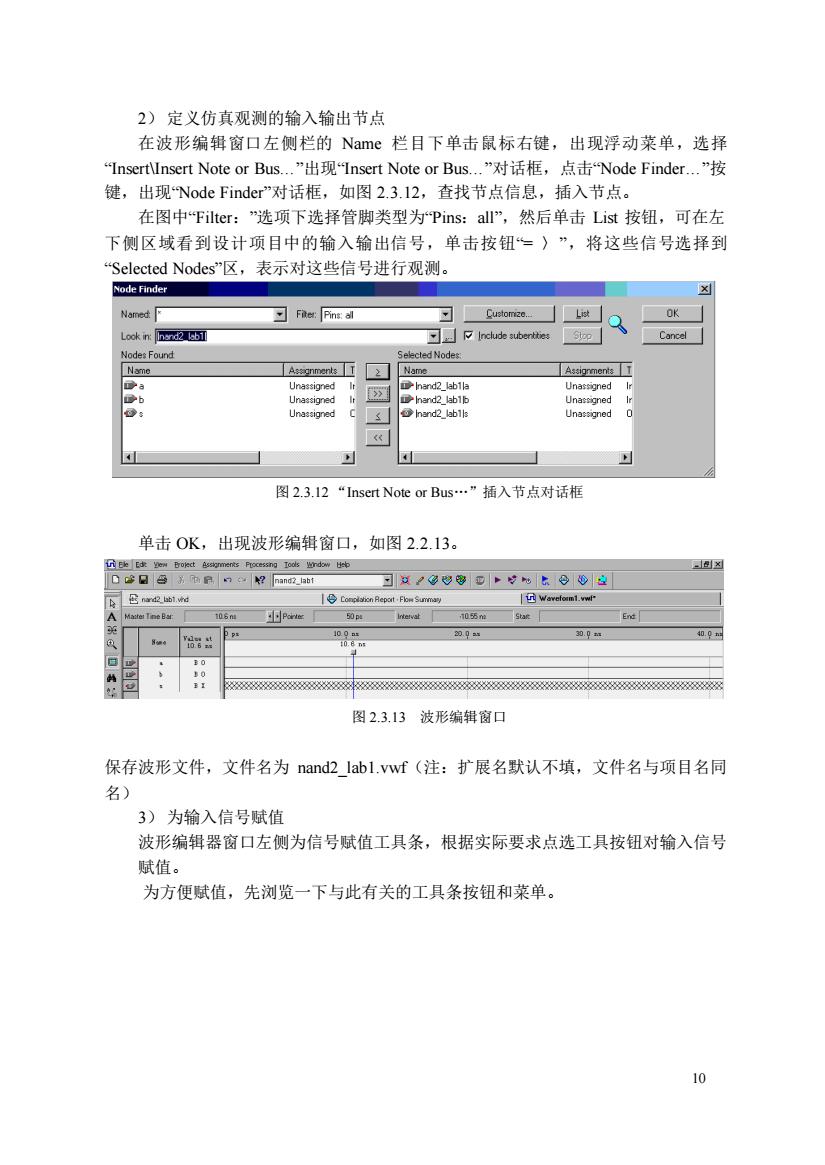

10 2) 定义仿真观测的输入输出节点 在波形编辑窗口左侧栏的 Name 栏目下单击鼠标右键,出现浮动菜单,选择 “Insert\Insert Note or Bus.”出现“Insert Note or Bus.”对话框,点击“Node Finder.”按 键,出现“Node Finder”对话框,如图 2.3.12,查找节点信息,插入节点。 在图中“Filter:”选项下选择管脚类型为“Pins:all”,然后单击 List 按钮,可在左 下侧区域看到设计项目中的输入输出信号,单击按钮“= 〉”,将这些信号选择到 “Selected Nodes”区,表示对这些信号进行观测。 图 2.3.12 “Insert Note or Bus.”插入节点对话框 单击 OK,出现波形编辑窗口,如图 2.2.13。 图 2.3.13 波形编辑窗口 保存波形文件,文件名为 nand2_lab1.vwf(注:扩展名默认不填,文件名与项目名同 名) 3) 为输入信号赋值 波形编辑器窗口左侧为信号赋值工具条,根据实际要求点选工具按钮对输入信号 赋值。 为方便赋值,先浏览一下与此有关的工具条按钮和菜单

图标 功能篇速 渴标 功能蕊迷 边据治取 文太编维 波彩编辑 波影是示馆被 定波形为未初始化 选定泼形为低电平 速宽发影为高电平 进定发影为高江状 选定减影为弱表知状数 选童左影为码低电平 选定波为稻高中平 透定发为无美态 进定波形为电垂取反 定彩为计载 选定泼形时网缘 设定减形的排序方 X? 选定泼形为任意设定值 选定减形为随机值 例如:为输入信号a,b赋值:选中a、b,单击工具条按钮对输入进行赋值。 选择a、b波形为计数脉冲形式,修改a的时间间隔为40ns,b的时间间隔为80ns 如图2.3.15。 图23.15设置输入信号 再次保存波形文件,如图2.3.16 End 1030040040000000,0 图2.316定义了输入信号的波形仿真窗口 4)时序仿真 选择Processing菜单下的Start Simulation选项,即开始波形仿真。状态窗口会 显示出仿真进程,仿真结束后,仿真结果已传递给波形文件。单击Open SCF按钮, 可打开波形文件,如图23.17所示。观察输出的波形,即考察在输入信号的激励下, 11

11 例如:为输入信号 a,b 赋值:选中 a、b,单击工具条按钮对输入进行赋值。 选择 a、b 波形为计数脉冲形式,修改 a 的时间间隔为 40ns,b 的时间间隔为 80ns, 如图 2.3.15。 图 2.3.15 设置输入信号 再次保存波形文件,如图 2.3.16 图 2.3.16 定义了输入信号的波形仿真窗口 4) 时序仿真 选择 Processing 菜单下的 Start Simulation 选项,即开始波形仿真。状态窗口会 显示出仿真进程,仿真结束后,仿真结果已传递给波形文件。单击 Open SCF 按钮, 可打开波形文件,如图 2.3.17 所示。观察输出的波形,即考察在输入信号的激励下