合优化等处理,使设计达到高度自动化,VHDL语言特别适合于大型或复杂的设计。 它具有以下一些优点 (1)VHDL语言是一种多层次的硬件描述语言,覆盖面,描述能力强。即设计 的原始描述可以是非常简练的描述,经过层层细化求精,最终成为可直接付诸生产的 电路级或版图参数描述,整个过程都可以在VHDL环境下进行。 (2)VHDL语言有良好的可读性,既可以被计算机接受,也容易被理解,用VHDL 书写的原文件,即是程序,又是文档,既是技术人员之间交换信息的文件,又可作为 合同签约者之间的文件 (3)VHDL本身的生命期长。因为VHDL的硬件描述与工艺技术无关,不会因工 艺变化而使描述过时。与工艺技术有关的参数可通过VHDL提供的属性加以描述,工 艺改变时,只需修改相应程序中的属性参数即可。 (4)支持大规模设计的分解和已有设计的再利用。一个大规模设计不可能一个人 独立完成,它将由多项目组来共同完成。VHDL为设计的分解和设计的再利用提供了 有力的支持。 (5)VHDL己成为IEEE承认的一个工业标准,事实上己成为通用硬件描述语言。 2.VHDL语言的基本组成 VHDL作为EDA技术的设计入门语言,它包含实体、结构体、程序包、库和配 置五个部分,其中实体用于描述设计单元的外部接口信号:结构体用于描述设计单元 内部结构和行为:程序包用来存放各设计模块共享的数据类型、常数、子程序等;库 是专门存放程序包的地方:配置语句是在一个实体对应有多个结构体时,按照设计者 的要求指定实体所要配置的结构体,以支持正确的编译。在五个组成部分中,实体和 结构体是必不可少的,其余的部分可以根据需要选用。下面详细介绍一下实体和结构 体两部分。 (1)entity实体:用来描述设计的对外端口信息,如输入和输出端口的描述,也 可以描述参数化的数值。 entity实体描述格式如下: entity实体名is [generic(类属表):] [port(端口表):] [begin 实体语句部分]: cnd[实体名]: 端口方向的四种模式:输入in、输出out、双向inout和缓冲buffer。缺省值是输入。 常用端口类型:布尔boolean、位bit、位矢量bit_vector、整数integer、标准逻辑std logic 和标准逻辑矢量std logic vector等。 如果使用std logic或std_logic_vector,需要在实体前使用下述语句进行说明: library IEEE; 2

2 合优化等处理,使设计达到高度自动化,VHDL 语言特别适合于大型或复杂的设计。 它具有以下一些优点 (1)VHDL 语言是一种多层次的硬件描述语言,覆盖面广,描述能力强。即设计 的原始描述可以是非常简练的描述,经过层层细化求精,最终成为可直接付诸生产的 电路级或版图参数描述,整个过程都可以在 VHDL 环境下进行。 (2)VHDL 语言有良好的可读性,既可以被计算机接受,也容易被理解,用 VHDL 书写的原文件,即是程序,又是文档,既是技术人员之间交换信息的文件,又可作为 合同签约者之间的文件。 (3)VHDL 本身的生命期长。因为 VHDL 的硬件描述与工艺技术无关,不会因工 艺变化而使描述过时。与工艺技术有关的参数可通过 VHDL 提供的属性加以描述,工 艺改变时,只需修改相应程序中的属性参数即可。 (4)支持大规模设计的分解和已有设计的再利用。一个大规模设计不可能一个人 独立完成,它将由多项目组来共同完成。VHDL 为设计的分解和设计的再利用提供了 有力的支持。 (5)VHDL 已成为 IEEE 承认的一个工业标准,事实上已成为通用硬件描述语言。 2.VHDL 语言的基本组成 VHDL 作为 EDA 技术的设计入门语言,它包含实体、结构体、程序包、库和配 置五个部分,其中实体用于描述设计单元的外部接口信号;结构体用于描述设计单元 内部结构和行为;程序包用来存放各设计模块共享的数据类型、常数、子程序等;库 是专门存放程序包的地方;配置语句是在一个实体对应有多个结构体时,按照设计者 的要求指定实体所要配置的结构体,以支持正确的编译。在五个组成部分中,实体和 结构体是必不可少的,其余的部分可以根据需要选用。下面详细介绍一下实体和结构 体两部分。 (1)entity 实体:用来描述设计的对外端口信息,如输入和输出端口的描述,也 可以描述参数化的数值。 entity 实体描述格式如下: entity 实体名 is [generic(类属表);] [port(端口表);] [begin 实体语句部分]; end [实体名]; 端口方向的四种模式:输入 in、输出 out、双向 inout 和缓冲 buffer。缺省值是输入。 常用端口类型:布尔 boolean、位 bit、位矢量 bit_vector、整数 integer、标准逻辑 std_logic 和标准逻辑矢量 std_logic_vector 等。 如果使用 std_logic 或 std_logic_vector ,需要在实体前使用下述语句进行说明: library IEEE;

use IEEE std logic 1164.all; (2)结构体:是电路和系统的逻辑功能描述部分。所有的结构体均附属于该实体 是实体的说明。 结构体描述格式如下: architecture结构体名of实体名is [说明语句: begin 「并行语句 end结构体名]: 结构体由两部分组成:begin前的说明语句部分和begin后的并行语句部分。 结构体名是该结构体的唯一名称,后面跟随的实体名表明该结构体对应的是哪个实 体,s表明结构体的命名结束。 说明语句用于对结构体内部所用到的信号、常数和函数等的定义,其定义只对结构体 内部可见,即仅结构体内部可以使用。 并行语句描述电路和系统并行发生的行为。 3

3 use IEEE_std_logic_1164.all; (2) 结构体:是电路和系统的逻辑功能描述部分。所有的结构体均附属于该实体, 是实体的说明。 结构体描述格式如下: architecture 结构体名 of 实体名 is [说明语句]; begin [并行语句]; end [结构体名]; 结构体由两部分组成:begin 前的说明语句部分和 begin 后的并行语句部分。 结构体名是该结构体的唯一名称,of 后面跟随的实体名表明该结构体对应的是哪个实 体,is 表明结构体的命名结束。 说明语句用于对结构体内部所用到的信号、常数和函数等的定义,其定义只对结构体 内部可见,即仅结构体内部可以使用。 并行语句描述电路和系统并行发生的行为

第2章FPGA开发工具使用 2.1 MaxplusIⅡ概述 MAX+plusII是Altera公司在Windows环境下开发的可编程逻辑设计软件平台 MAX+plusII是Multiple Array Matrix and Programmable Logic Use System的缩写。该系 统将数字电路设计集成在一个环境内,支持Altera公司的各种可编程器件,允许多种 输入方式(图形输入、文本输入、波形输入等)输入逻辑设计文件,经过系统编辑器 的编译、综合等操作,对设计项目进行时序仿真分析、延时时间分析、编译等,最后 将编译好的电路分配到一个或多个器件中。 MAX+plusII不仅支持原理图输入的设计项目,还支持硬件描述语言(如AHDl 和VHDL)输入的设计项目。AHDL(Altera Hardware Description Language)语言是 4tera公司自创的一种高级硬件行为描述语言,该语言可以使用布尔方程、算术运算 真值表条件语句等方式进行描述,适合状态机的设计。而VHDL语言是一种符合EEE 标准的高级硬件行为描述语言,目前已成为数字系统设计的主要硬件描述语言。AHDL 和VHDL语言都可以用文本进行设计的,但文件名后缀分别为*.tdf和*.vhd。 MAX+plus通过输入文件、项目编译、项目仿真、时序仿真、编程下载完成一个 完整的设计项目。 2.2 QuartusIⅡ软件概述 QuartusII软件是Altera公司最新版本的EDA开发软件,支持APEX系列、Cyclone 系列、Strati议系列和Excalibur系列等新型系列器件的开发。含有工作组计算、集成逻 辑分析仪、EDA工具集成、多过程支持、增强重编译和IP集成等特性。支持百万门 级的设计,支持高速IVO设计,具有更强的设计能力和更快的编译速度。QuartusIⅡ开 发软件为可编程片上系统(OPC)设计提供了一个完整的设计环境。无论是使用个人 电脑、NUIX或Linux工作站,QuartusII都提供了方便设计、快速编译处理以及编程 功能 为了保证QuartuslI软件能正常运行,首次运行QuartuslI必须设置license,dat文 件。否则仿真和下载等功能将被禁用。具体操作是在QuartusII管理器界面中选择 Tool\License Setup.,点击“”按钮,弹出对话框,选择License.dat文件或直接输入带 全路径名的文件名。 进入Windows操作系统,启动QuartusII,就可以进行项目设计的一系列工作了。 QuartuslI输入的设计过程可分为创建工程、输入文件、项目编译、项目校验和编 程下载等几个步骤。下面以文本输入方式介绍整个设计过程

4 第 2 章 FPGA 开发工具使用 2.1 MaxplusII 概述 MAX+plusII 是 Altera 公司在 Windows 环境下开发的可编程逻辑设计软件平台, MAX+plusII 是 Multiple Array Matrix and Programmable Logic Use System 的缩写。该系 统将数字电路设计集成在一个环境内,支持 Altera 公司的各种可编程器件,允许多种 输入方式(图形输入、文本输入、波形输入等)输入逻辑设计文件,经过系统编辑器 的编译、综合等操作,对设计项目进行时序仿真分析、延时时间分析、编译等,最后 将编译好的电路分配到一个或多个器件中。 MAX+plusII 不仅支持原理图输入的设计项目,还支持硬件描述语言(如 AHDL 和 VHDL)输入的设计项目。AHDL(Altera Hardware Description Language)语言是 Altera 公司自创的一种高级硬件行为描述语言,该语言可以使用布尔方程、算术运算、 真值表条件语句等方式进行描述,适合状态机的设计。而 VHDL 语言是一种符合 IEEE 标准的高级硬件行为描述语言,目前已成为数字系统设计的主要硬件描述语言。AHDL 和 VHDL 语言都可以用文本进行设计的,但文件名后缀分别为*.tdf 和*.vhd。 MAX+plusII 通过输入文件、项目编译、项目仿真、时序仿真、编程下载完成一个 完整的设计项目。 2.2 QuartusII 软件概述 QuartusII 软件是 Altera 公司最新版本的 EDA 开发软件,支持 APEX 系列、Cyclone 系列、Stratix 系列和 Excalibur 系列等新型系列器件的开发。含有工作组计算、集成逻 辑分析仪、EDA 工具集成、多过程支持、增强重编译和 IP 集成等特性。支持百万门 级的设计,支持高速 I/O 设计,具有更强的设计能力和更快的编译速度。QuartusII 开 发软件为可编程片上系统(SOPC)设计提供了一个完整的设计环境。无论是使用个人 电脑、NUIX 或 Linux 工作站,QuartusII 都提供了方便设计、快速编译处理以及编程 功能。 为了保证 QuartusII 软件能正常运行,首次运行 QuartusII 必须设置 license.dat 文 件。否则仿真和下载等功能将被禁用。具体操作是在 QuartusII 管理器界面中选择 Tool\License Setup.,点击“.”按钮,弹出对话框,选择 License.dat 文件或直接输入带 全路径名的文件名。 进入 Windows 操作系统,启动 QuartusII,就可以进行项目设计的一系列工作了。 QuartusII 输入的设计过程可分为创建工程、输入文件、项目编译、项目校验和编 程下载等几个步骤。下面以文本输入方式介绍整个设计过程

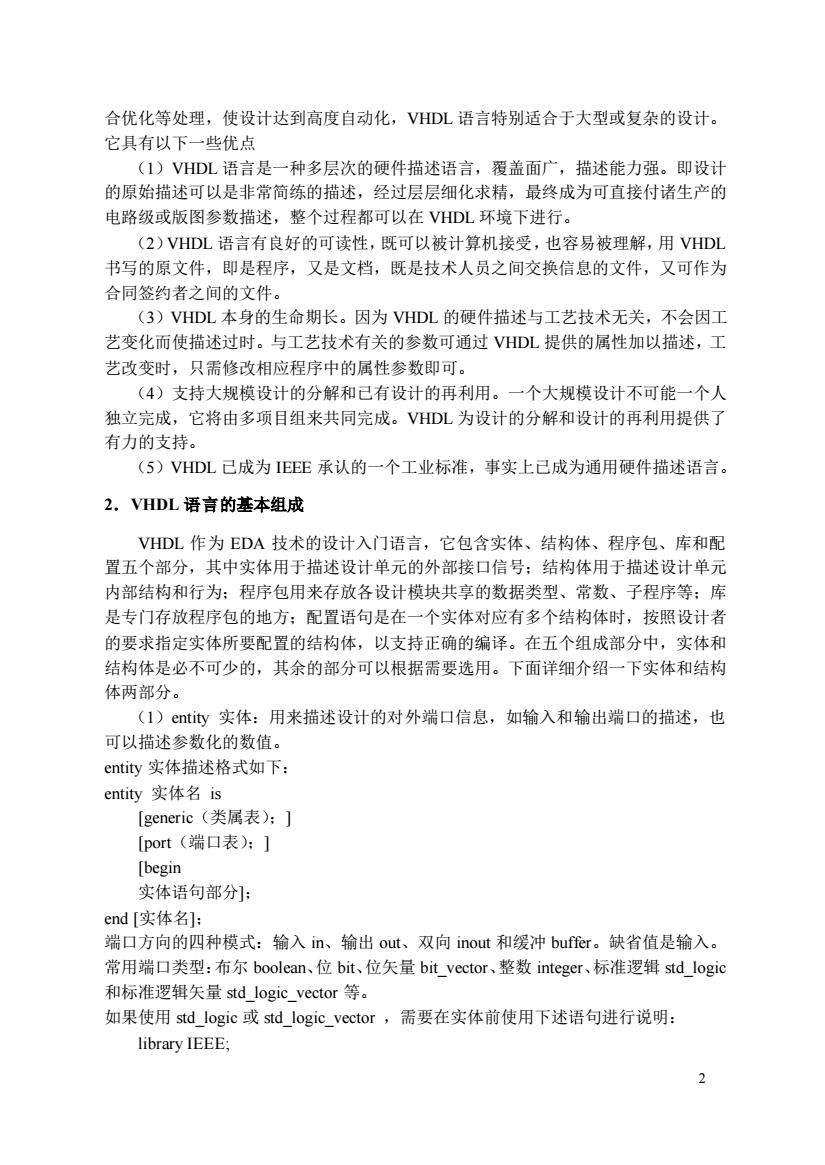

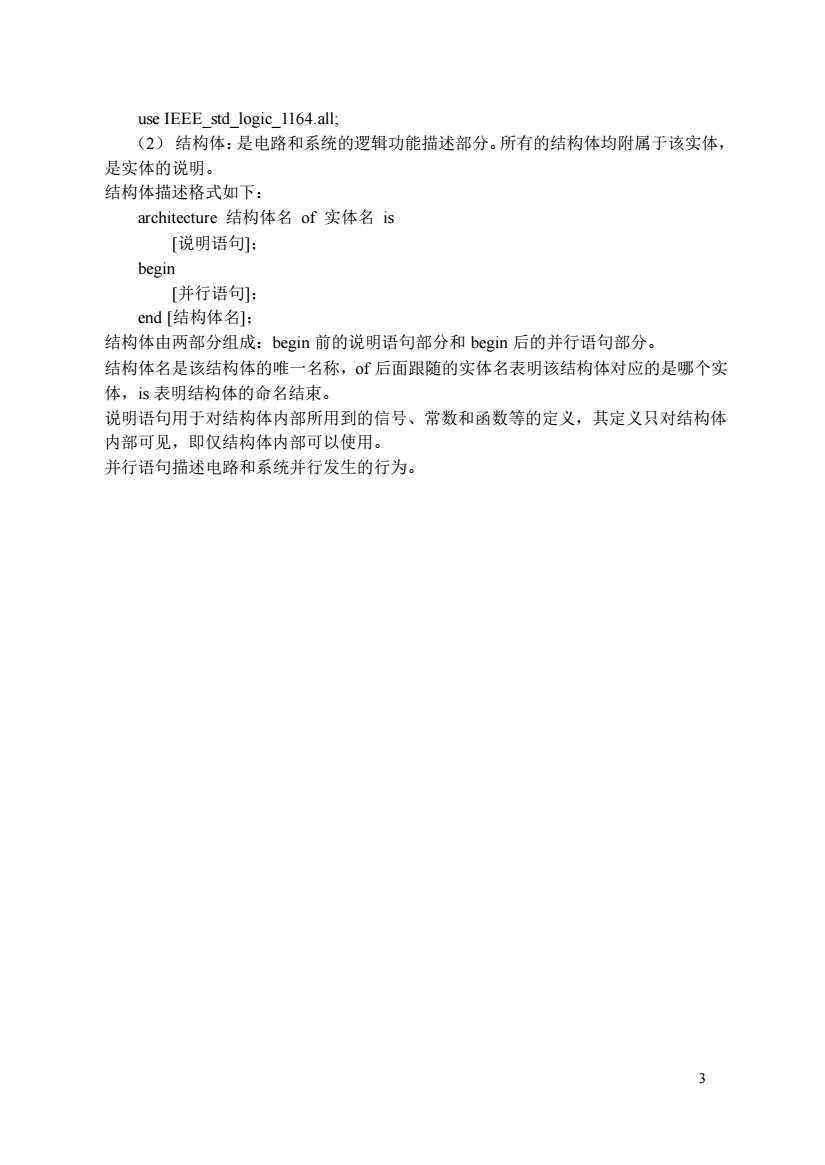

2.3文本输入的设计过程 现通过一个简单设计实例说明QuartusII的基本文本设计过程, 例:用硬件描述语言VHDL设计一个2输入与非门。 设计放d:\nand2lab1目录下,工程文件名为nand2labl。 点击“我的电脑”,在D盘新建名为nand2labl”文件夹。 1.创建工程文件 利用QuartusII软件创建工程向导(New Project Wizard)创建一个新工程。 打开QuartusIl6.0软件界面,在“文件"菜单下选择New Project Wizard",点击next” 后弹出如图2.3.1对话框。 d Directory.Name,1p-ee灯geW) 图2.3 I New Project Wizard对话框第一页 选第一行右侧的“”选择工程目录为d:\nand2lab1”,在第二行输入项目名称: nand2labl,第三行默认把项目名设为顶层文件名,点击ncxt”。 2)新建项目向导第二页,如图2.3.2,该窗口可为项目添加己经编辑好的程序文件, 默认为空,点击“next”,弹出图2.3.3。 图2.3.2 New Project Wizard对话框第二页 3)新建项目向导第三页,如图2.3.3,该窗口可以选择FPGA硬件信息,在Family 5

5 2.3 文本输入的设计过程 现通过一个简单设计实例说明 QuartusII 的基本文本设计过程。 例:用硬件描述语言 VHDL 设计一个 2 输入与非门。 设计放 d:\ nand2_lab1 目录下,工程文件名为 nand2_lab1 。 点击“我的电脑”,在 D 盘新建名为“nand2_lab1”文件夹。 1. 创建工程文件 利用 QuartusII 软件创建工程向导(New Project Wizard)创建一个新工程。 打开 QuartusII6.0 软件界面,在“文件”菜单下选择“New Project Wizard”,点击“next” 后弹出如图 2.3.1 对话框。 图 2.3.1 New Project Wizard 对话框第一页 选第一行右侧的“.”选择工程目录为“d:\ nand2_lab1”,在第二行输入项目名称: nand2_lab1,第三行默认把项目名设为顶层文件名,点击“next”。 2)新建项目向导第二页,如图 2.3.2,该窗口可为项目添加已经编辑好的程序文件, 默认为空,点击“next”,弹出图 2.3.3。 图 2.3.2 New Project Wizard 对话框第二页 3)新建项目向导第三页,如图 2.3.3,该窗口可以选择 FPGA 硬件信息,在 Family

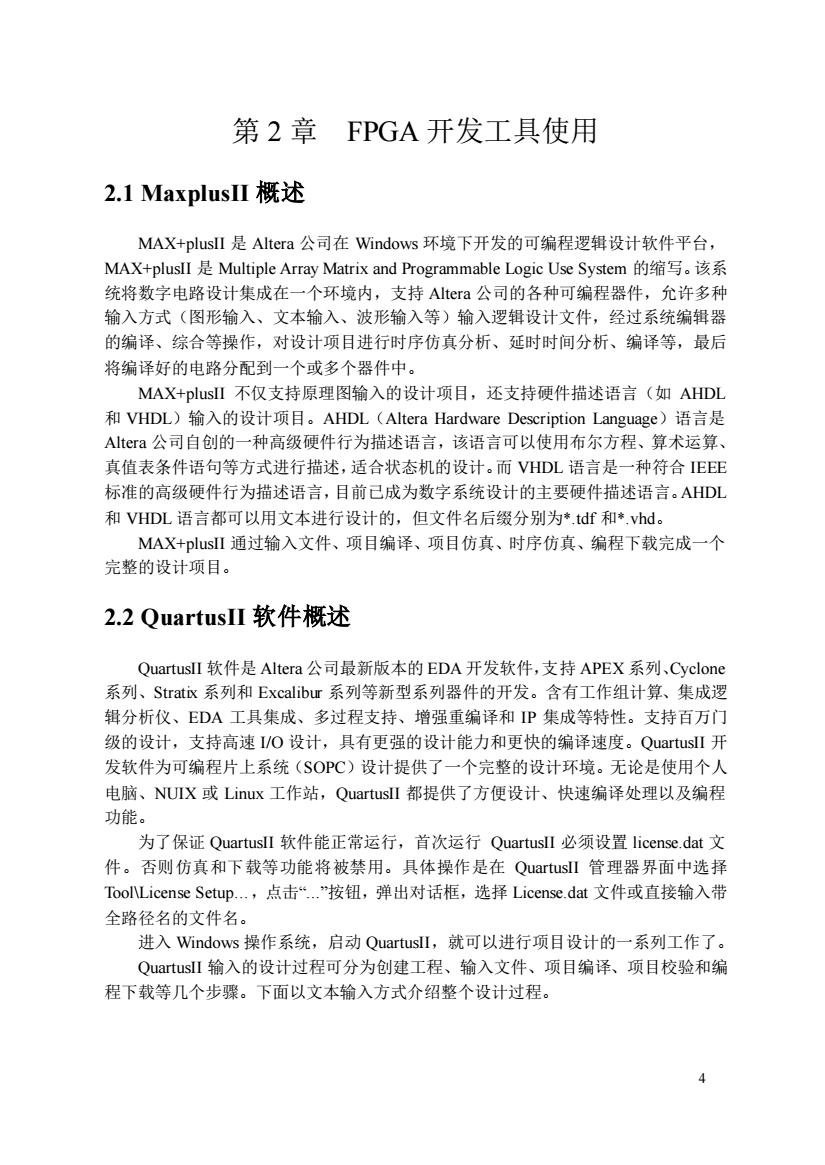

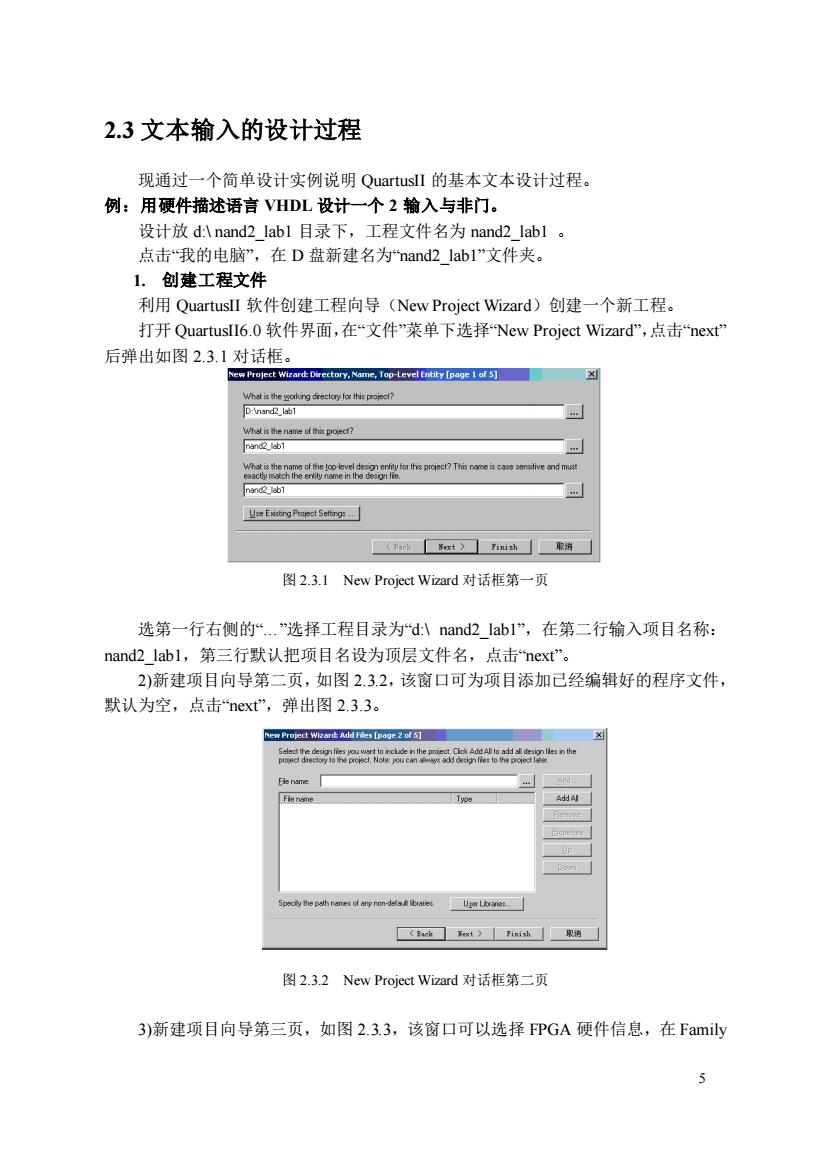

下拉框内选择FLEX10K”,在Avaliable devices窗口选择芯片型号为: EPF10K20RC208-4,其它选项默认。点击“next”。 《点厂)厂u由黎别 图2.3.3 New Project Wizard对话框第三页 4)新建项目向导第四页,如图2.3.4,该窗口用来添加第三方EDA工具软件参与 综合、仿真、时序分析等工作,本实验默认不选,点击“nx”,弹出图2.3.5。 《s)1合泉为 图2.3.4 New Project Wizard对话框第四页 5)新建项目向导第五页,如图2.3.5, 〈。>回事有 图2.3.5 New Project Wizard对话框第五页 6

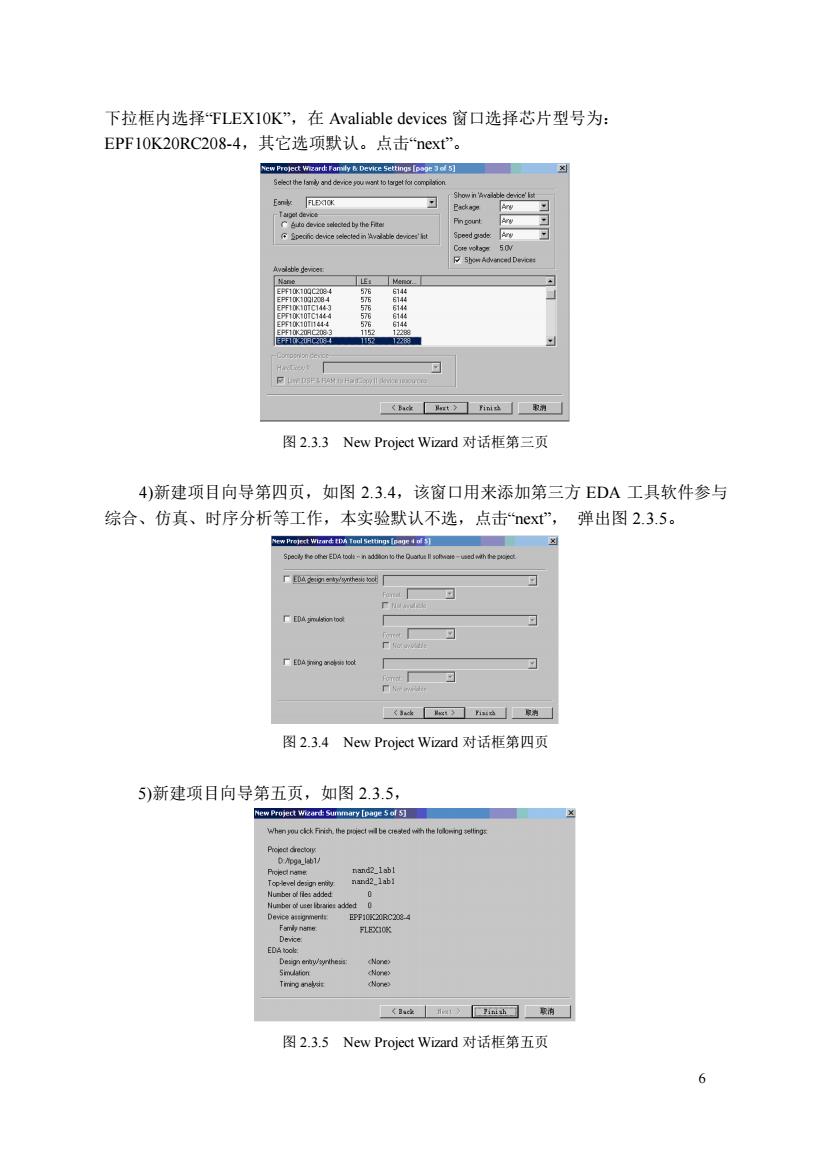

6 下拉框内选择“FLEX10K”,在 Avaliable devices 窗口选择芯片型号为: EPF10K20RC208-4,其它选项默认。点击“next”。 图 2.3.3 New Project Wizard 对话框第三页 4)新建项目向导第四页,如图 2.3.4,该窗口用来添加第三方 EDA 工具软件参与 综合、仿真、时序分析等工作,本实验默认不选,点击“next”, 弹出图 2.3.5。 图 2.3.4 New Project Wizard 对话框第四页 5)新建项目向导第五页,如图 2.3.5, 图 2.3.5 New Project Wizard 对话框第五页