4.2常用的组合逻辑电路 4.2.1译码器 译码器功能:将输入的代码“翻译”成另外一种代码输 出。 常用的译码器有:二进制译码器,二一十进制译码器和 七段显示译码器等几类。 1.二进制译码器: 译码输入:n位二进制代码 译码输出:m位输出信号m=2n 译码规则:对应输入的一组二进制代码有且仅有一个对 应的输出端为有效电平,其余输出端为相反电平

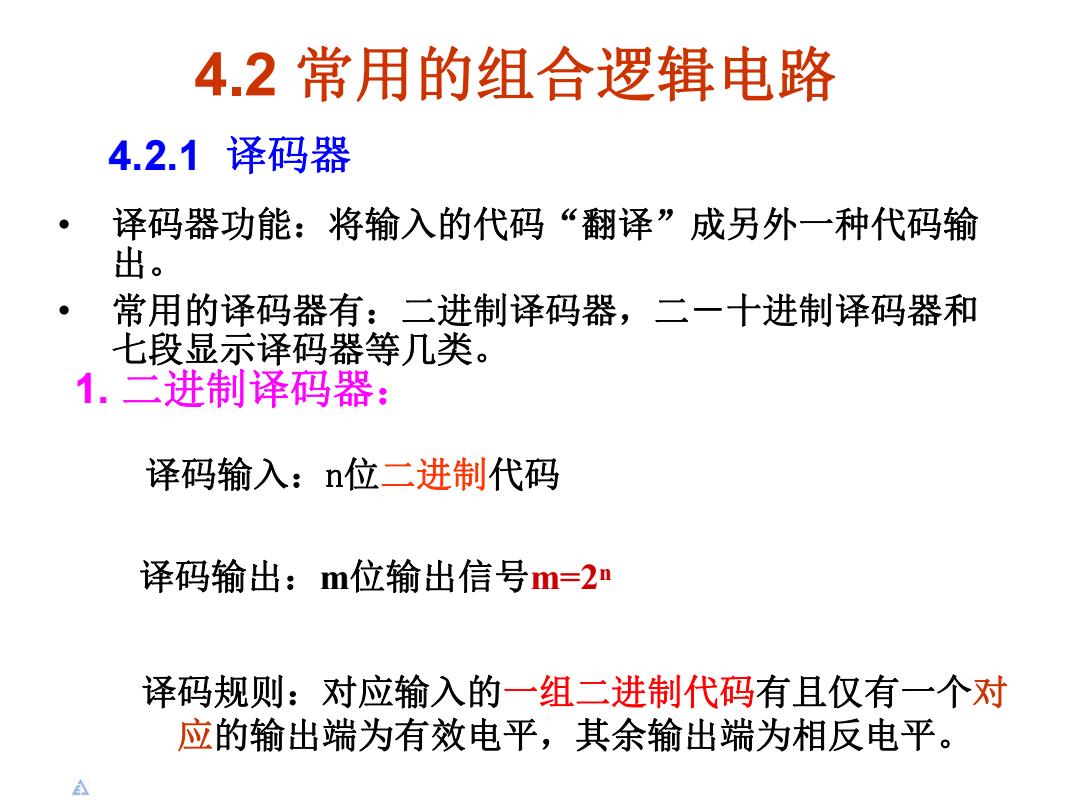

4.2 常用的组合逻辑电路 • 译码器功能:将输入的代码“翻译”成另外一种代码输 出。 • 常用的译码器有:二进制译码器,二-十进制译码器和 七段显示译码器等几类。 4.2.1 译码器 译码输入:n位二进制代码 译码输出:m位输出信号m=2 n 译码规则:对应输入的一组二进制代码有且仅有一个对 应的输出端为有效电平,其余输出端为相反电平。 1. 二进制译码器:

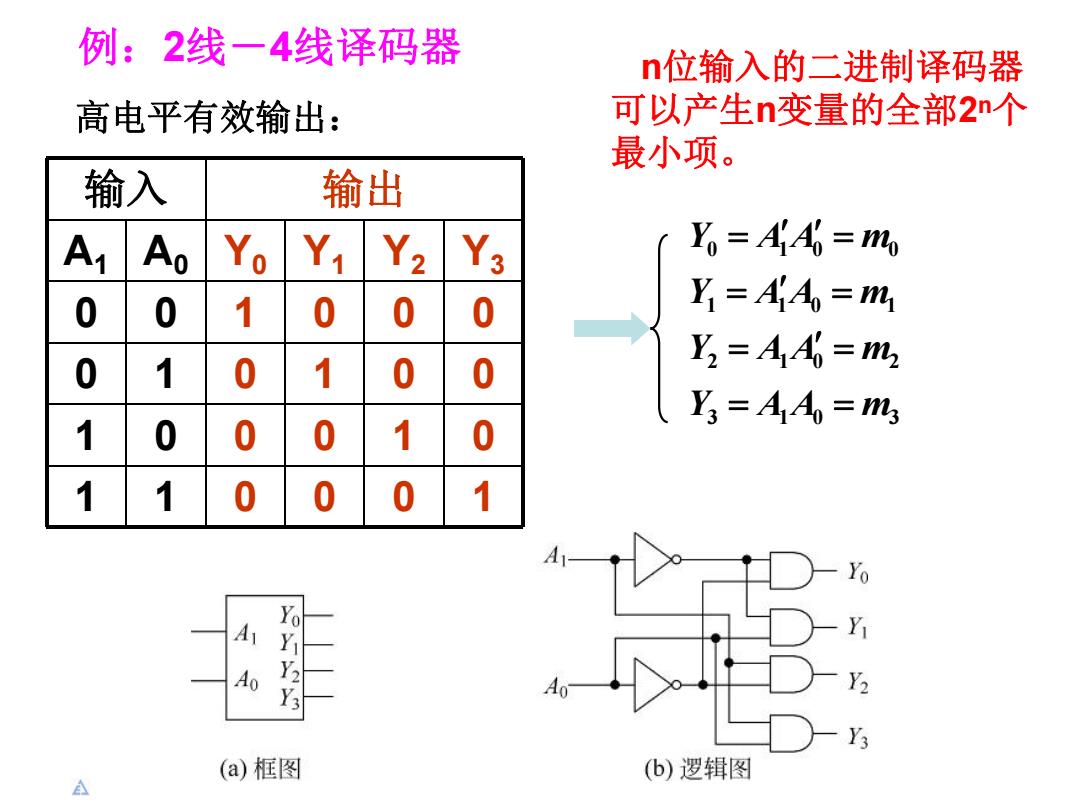

例:2线一4线译码器 n位输入的二进制译码器 高电平有效输出: 可以产生n变量的全部2n个 最小项。 输入 输出 A Ao 3 Yo =AAo=mo 0 0 0 Y=AA=m 0 1 0 1 Y=AA=m2 Y3=A Ao=mg 1 0 0 0 0 1 1 0 0 Y (a)框图 (b)逻辑图 A

例:2线-4线译码器 3 1 0 3 2 1 0 2 1 1 0 1 0 1 0 0 Y A A m Y A A m Y A A m Y A A m n位输入的二进制译码器 可以产生n变量的全部2n个 最小项。 输入 输出 A1 A0 Y0 Y1 Y2 Y3 0 0 1 0 0 0 0 1 0 1 0 0 1 0 0 0 1 0 1 1 0 0 0 1 高电平有效输出:

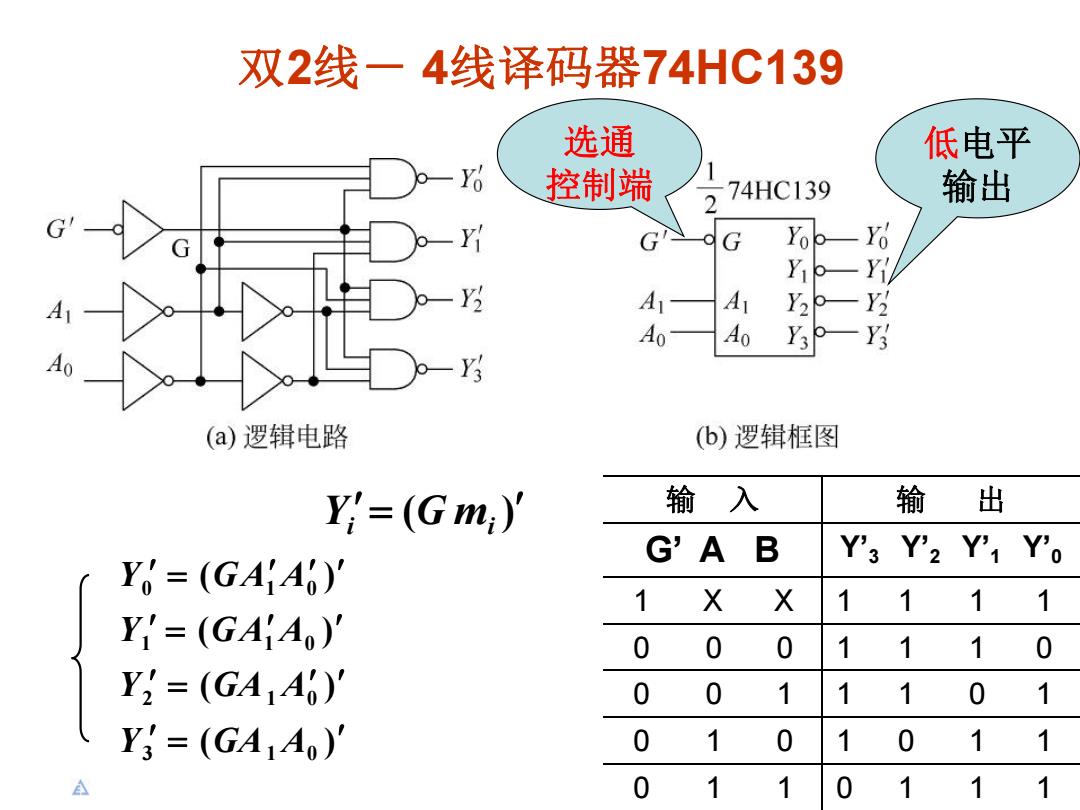

双2线-4线译码器74HC139 选通 低电平 控制端 2 74HC139 输出 Yop Yo A 4 A Ao Ao Yi (a)逻辑电路 (b)逻辑框图 Y=(Gmi ) 输入 输 出 G'A B Y'3 Y'2 Y1 Yo Yo=(GA:A)" 1 X × 1 1 1 1 Y=(GAA) 0 0 0 1 1 0 Y=(GA1A0)' 0 0 1 7 0 1 Y3=(GA1A)' 0 0 1 0 1 A 0 1 0 1 1 1

双2线- 4线译码器74HC139 ( ) Yi G mi 低电平 输出 选通 控制端 ( ) ( ) ( ) ( ) 3 1 0 2 1 0 1 1 0 0 1 0 Y GA A Y GA A Y GA A Y GA A 输 入 输 出 G’ A B Y’ 3 Y’ 2 Y’ 1 Y’ 0 1 X X 1 1 1 1 0 0 0 1 1 1 0 0 0 1 1 1 0 1 0 1 0 1 0 1 1 0 1 1 0 1 1 1

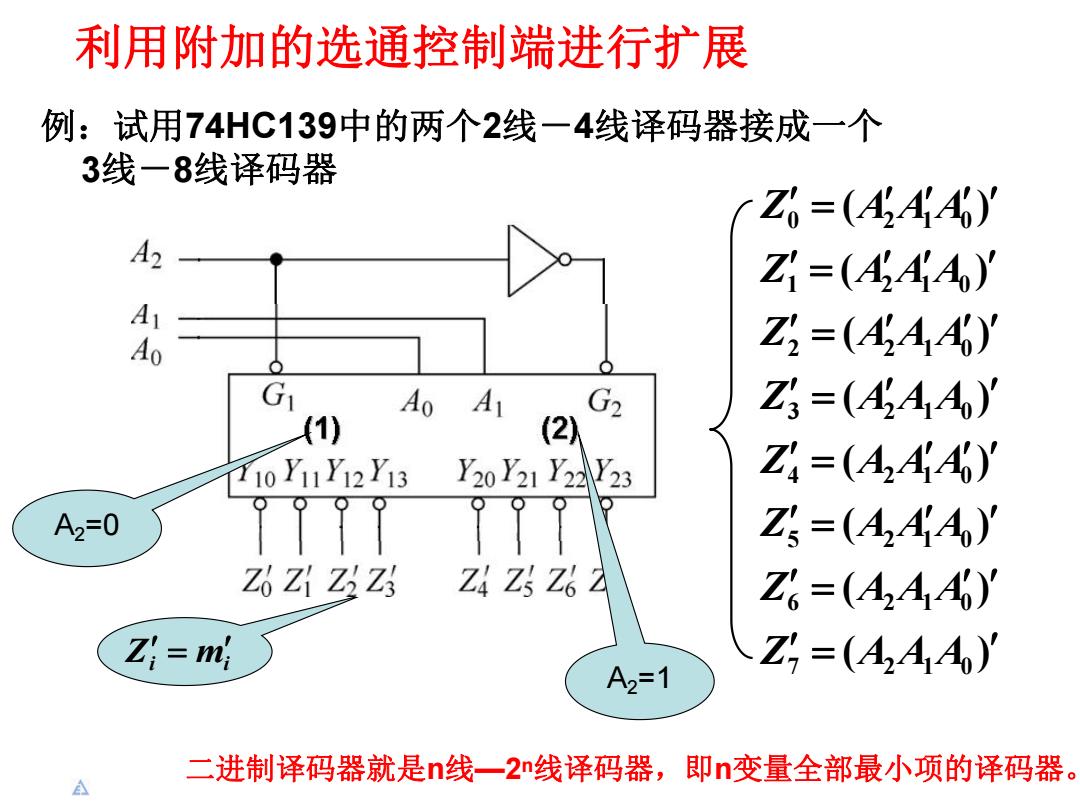

利用附加的选通控制端进行扩展 例:试用74HC139中的两个2线一4线译码器接成一个 3线一8线译码器 Z0=(AAA6)1 A2 Z=(444)' A Ao Z=(444)' Ao A1 G Z3=(444)' (1) (2λ 10YnY12Yi3 Y20Y21Y22Y23 Z:=(44) A2=0 Z=(444) Zo ZiZZ Zi Zs Zo2 Zo=(444) Z;=m Z)=(A,A1A0)1 A2=1 二进制译码器就是n线一2n线译码器,即n变量全部最小项的译码器

例:试用74HC139中的两个2线-4线译码器接成一个 3线-8线译码器 ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) 7 2 1 0 6 2 1 0 5 2 1 0 4 2 1 0 3 2 1 0 2 2 1 0 1 2 1 0 0 2 1 0 Z A A A Z A A A Z A A A Z A A A Z A A A Z A A A Z A A A Z A A A Zi mi 利用附加的选通控制端进行扩展 二进制译码器就是n线—2n线译码器,即n变量全部最小项的译码器。 A2=0 A2=1

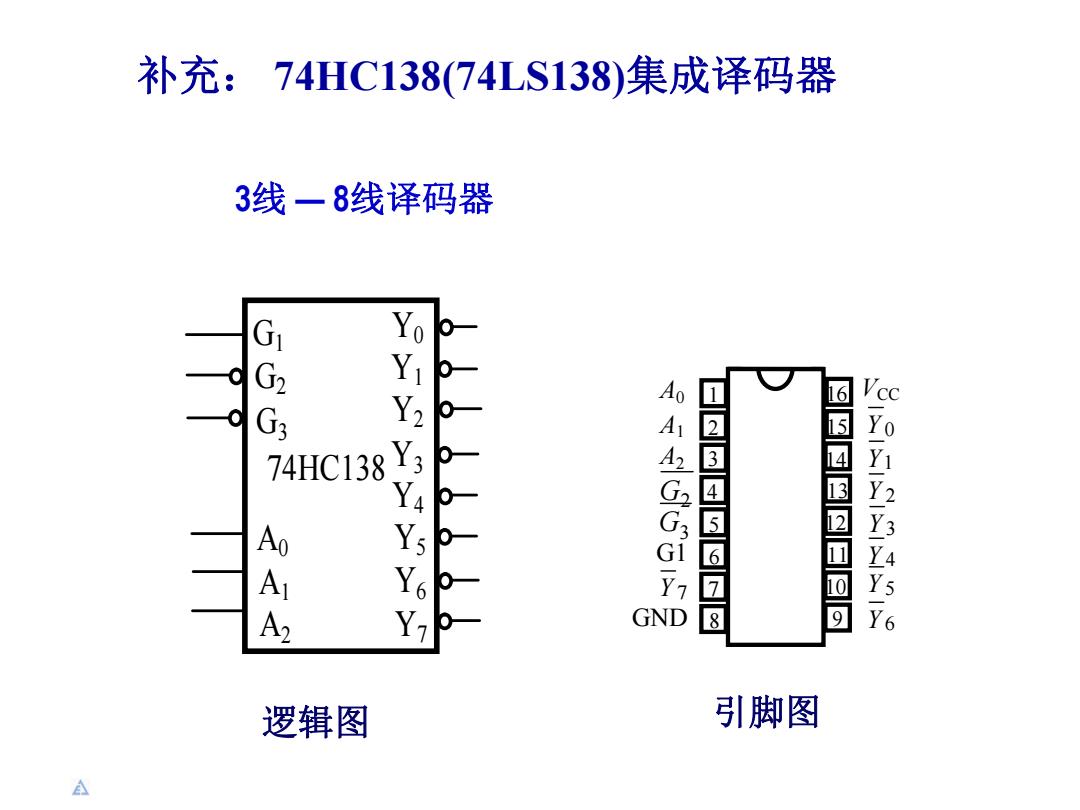

补充:74HC138(74LS138)集成译码器 3线一8线译码器 G6 0 74HC138 12343678 654 E GND 9 一23% 逻辑图 引脚图 A

补充: 74HC138(74LS138)集成译码器 A0 A1 A2 G2 G3 G1 Y 7 GND VCC Y1 Y 2 Y3 Y 4 Y5 Y 6 Y 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 逻辑图 引脚图 74HC138 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 G1 G2 G3 A0 A1 A2 3线 — 8线译码器