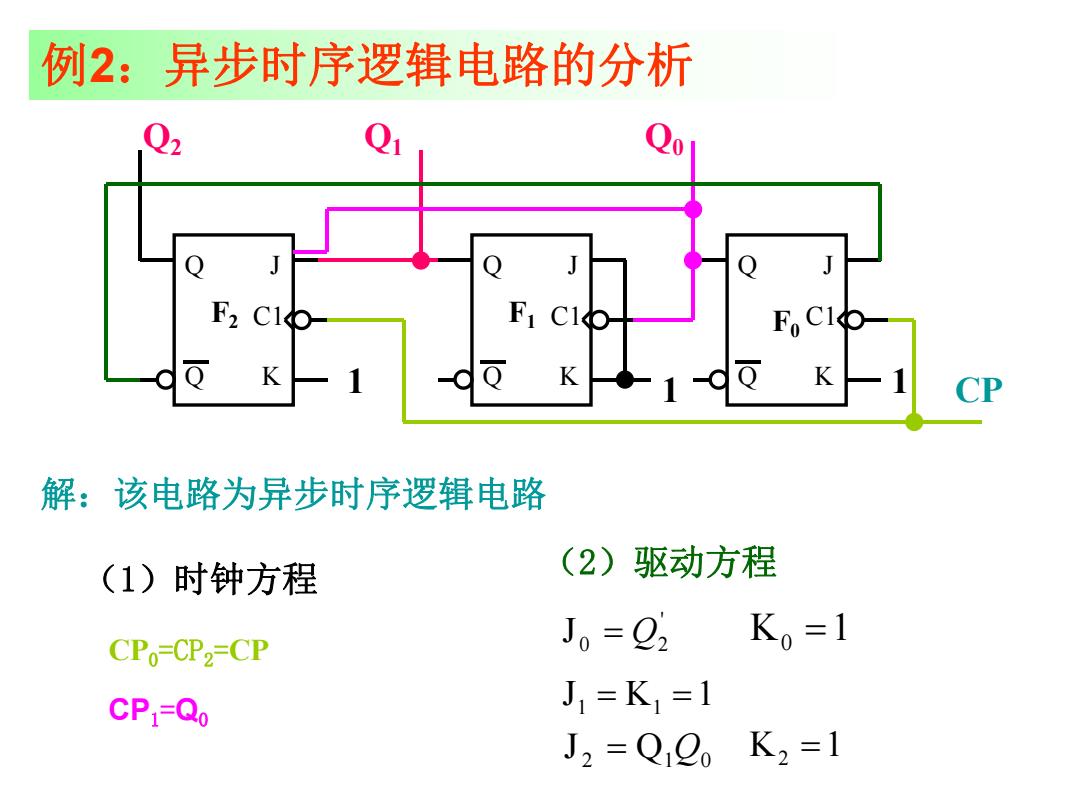

例2:异步时序逻辑电路的分析 CP 解:该电路为异步时序逻辑电路 (1)时钟方程 (2)驱动方程 CPo=CP2=CP J。=Q2 K。=1 CP1-Qo J1=K1=1 J2=Q20 K2=1

CP1=Q0 解:该电路为异步时序逻辑电路 (1)时钟方程 CP0=CP2=CP 例2:异步时序逻辑电路的分析 ' 0 2 J Q J K 1 1 1 K 1 0 K2 1 2 Q1 0 J Q (2)驱动方程 F2 J C1 K Q Q F0 J C1 K Q Q Q2 Q0 CP J C1 K Q Q F1 Q1 1 1 1

(3)状态方程 Q-JQ+KO Q=Q22 (CPo) J。=Q2 K=1 Q1=0 (CP1↓) J1=K=1 Q2=92200 (CP2↓) J2=QjQo K2=1 (④)状态转换表、状态转换图 CP Q220o Q:0"0, CP2CPCPo 000 00 1 无效状态 ↓ ↓ ↓ 001 01 0 ↓↓↓ 010 01 1 111 110 101 ↓ 011 10 0 ↓↓↓ ↓ 100 000 000 001 010 101 01 0 无效状态 ↓↓↓ 有效循环 11 0 0 100 011 11 0 0 0 ↓↓

(3)状态方程 ' 0 2 J Q J1 K1 1 K0 1 K2 1 2 Q1Q0 J ' 0 ' 2 * Q0 Q Q 1 0 ' 2 * Q2 Q Q Q '1 * Q1 Q (4)状态转换表、状态转换图 CP CP2CP1CP0 Q2Q1Q0 * 0 * 1 * Q2Q Q ↓ 0 0 0 0 0 1 ↓ ↓ (CP0↓) (CP2↓) (CP1↓) 000 001 ↓ 0 0 1 0 1 0 ↓ ↓ ↓ 010 ↓ 0 1 0 0 1 1 ↓ ↓ 011 ↓ 0 1 1 1 0 0 ↓ ↓ ↓ 100 ↓ 1 0 0 0 0 0 ↓ ↓ 1 0 1 0 1 0 ↓ ↓ ↓ 1 1 0 0 1 0 ↓ ↓ 1 1 1 0 0 0 ↓ ↓ ↓ 111 110 101 无效状态 有效循环 无 效 状 态 Q JQ' K'Q *

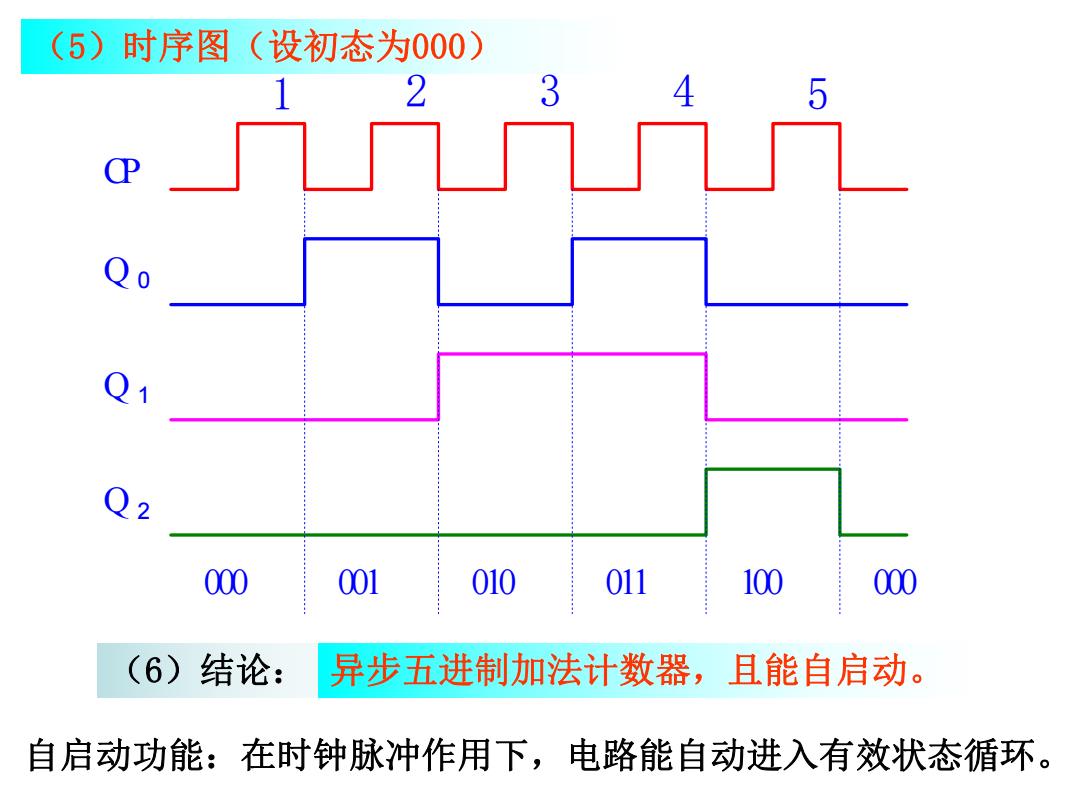

(5)时序图(设初态为000) 000 001 010 011 100 00 (6)结论: 异步五进制加法计数器,且能自启动。 自启动功能:在时钟脉冲作用下,电路能自动进入有效状态循环

Q Q Q CP 000 001 010 011 100 000 0 1 2 1 2 3 4 5 (6)结论: 异步五进制加法计数器,且能自启动。 (5)时序图(设初态为000) 自启动功能:在时钟脉冲作用下,电路能自动进入有效状态循环

63常用的时序逻辑电路 6.3.1寄存器 寄存器:用来存储二值信息代码的逻辑部件。它的主 要组成部分是触发器。 一个触发器能存储1位二进制代码,存储n位二进 制代码的寄存器需要用n个触发器组成。寄存器实际 上是若干触发器的集合

6.3.1 寄存器 寄存器:用来存储二值信息代码的逻辑部件。它的主 要组成部分是触发器。 一个触发器能存储1位二进制代码,存储 n 位二进 制代码的寄存器需要用 n 个触发器组成。寄存器实际 上是若干触发器的集合。 6.3 常用的时序逻辑电路

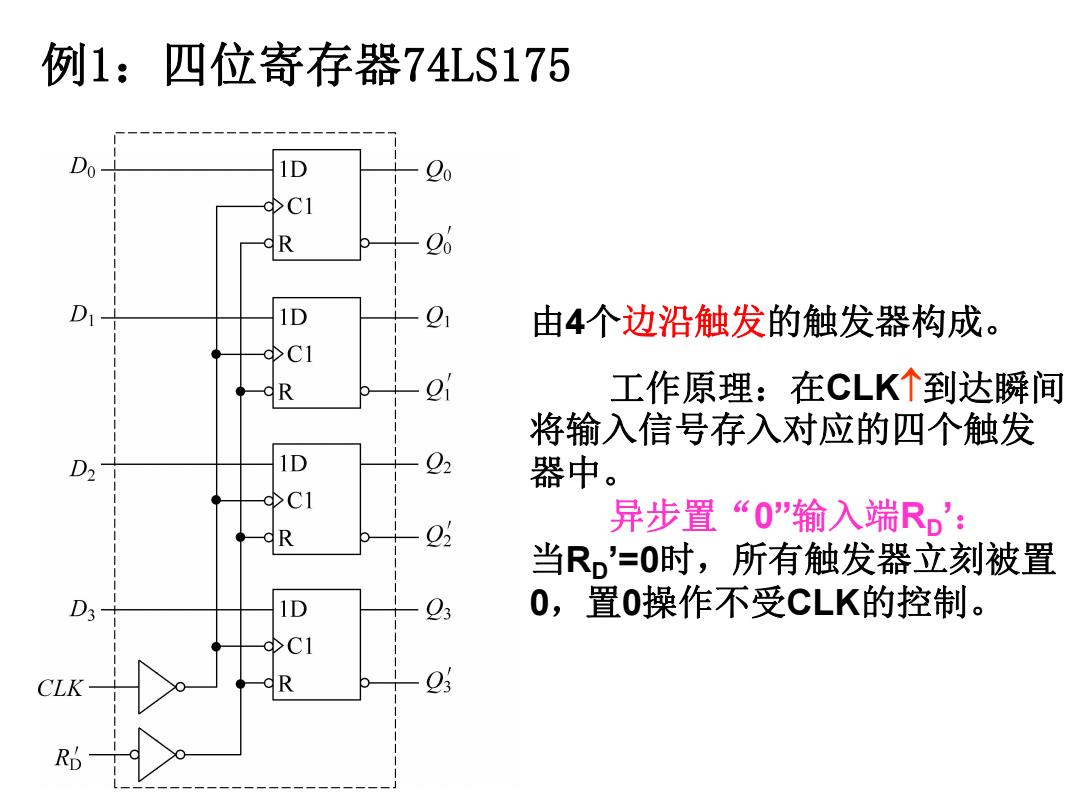

例1:四位寄存器74LS175 R D D 91 由4个边沿触发的触发器构成。 91 工作原理:在CLK个到达瞬间 将输入信号存入对应的四个触发 92 器中。 异步置“0输入端R,': 92 当R,'=0时,所有触发器立刻被置 0,置0操作不受CLK的控制。 3

例1:四位寄存器74LS175 由4个边沿触发的触发器构成。 工作原理:在CLK到达瞬间 将输入信号存入对应的四个触发 器中。 异步置“0”输入端RD ’ : 当RD ’=0时,所有触发器立刻被置 0,置0操作不受CLK的控制